# **DISCIPLINA EA701**

## **Introdução aos Sistemas Embarcados**

### **ROTEIRO 11: REDES INDUSTRIAIS**

**Topologias de Rede, Modelos de Comunicação, Arbitragem de Barramento, Mecanismos de Sincronização e Robustez, Filtragem de Mensagens, Rede CAN (Protocolo CAN, *Transceiver MCP2551*), Rede DMX**

**Profs. Antonio A. F. Quevedo e Wu Shin-Ting**

**FEEC / UNICAMP**

**Revisado e modificado em maio de 2025 por Ting com auxílio do Chatgpt**

**Revisado em outubro de 2024**

This work is licensed under Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International. To view a copy of this license, visit <https://creativecommons.org/licenses/by-nc-sa/4.0/>

|                                                                 |           |

|-----------------------------------------------------------------|-----------|

| <b>INTRODUÇÃO</b>                                               | <b>2</b>  |

| <b>PROJETOS-EXEMPLO</b>                                         | <b>5</b>  |

| Projeto de comunicação CAN usando loopback                      | 5         |

| Projeto de comunicação CAN usando loopback e filtros            | 18        |

| Projeto de comunicação CAN usando 4 nós                         | 21        |

| Projeto de comunicação CAN usando múltiplos nós parametrizáveis | 33        |

| <b>FUNDAMENTOS TEÓRICOS</b>                                     | <b>37</b> |

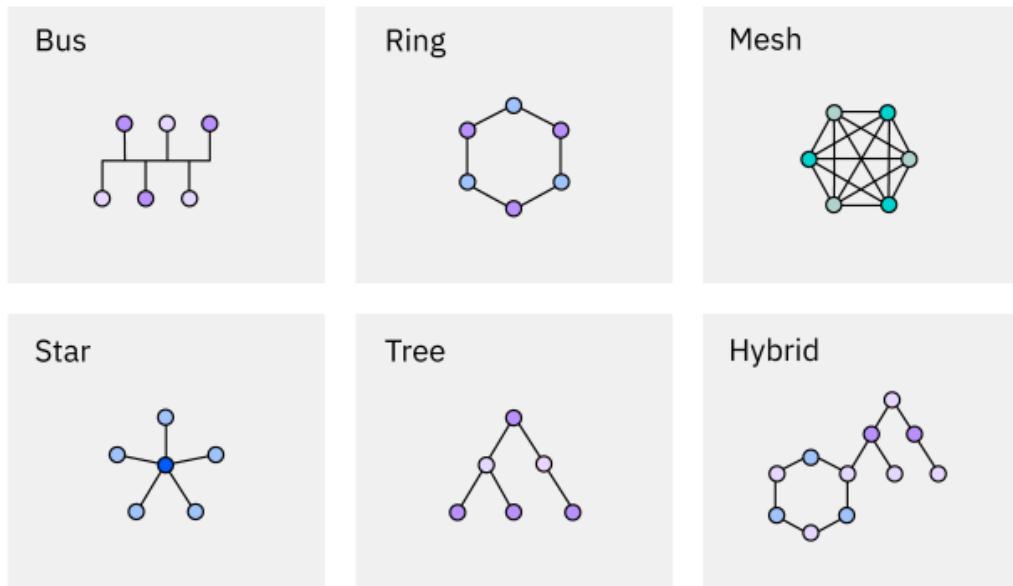

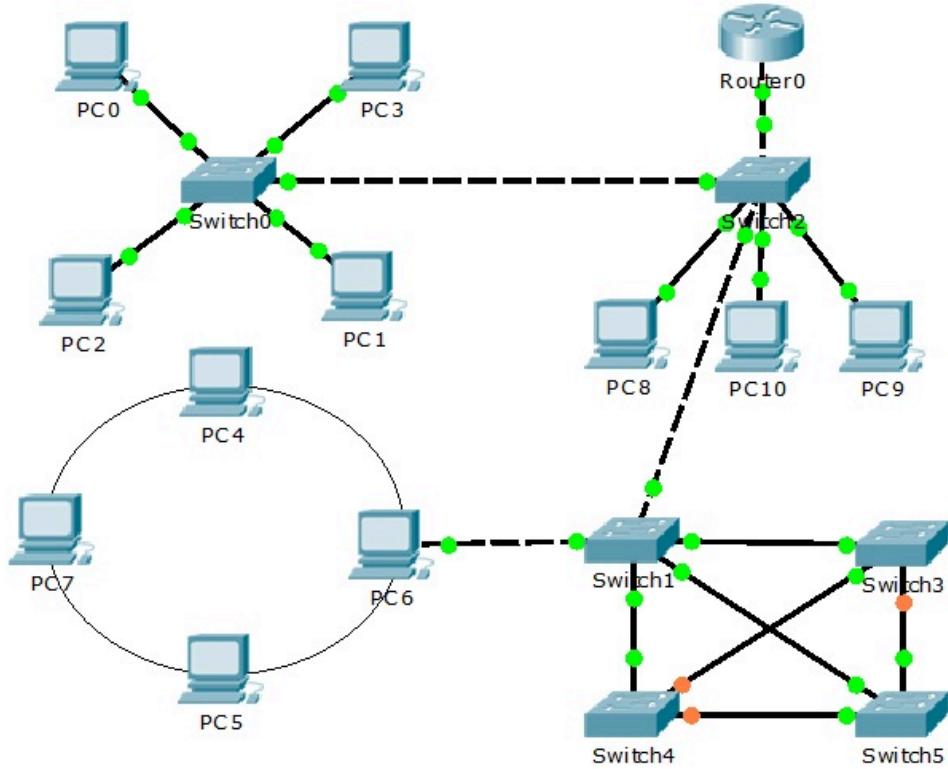

| TOPOLOGIAS DE REDE                                              | 38        |

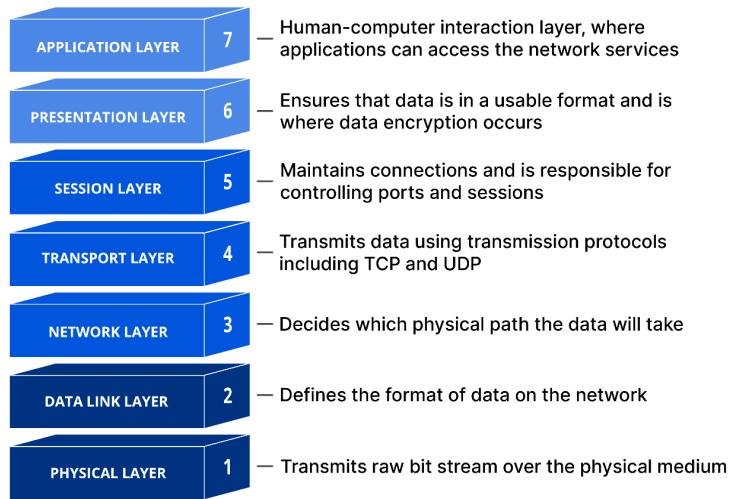

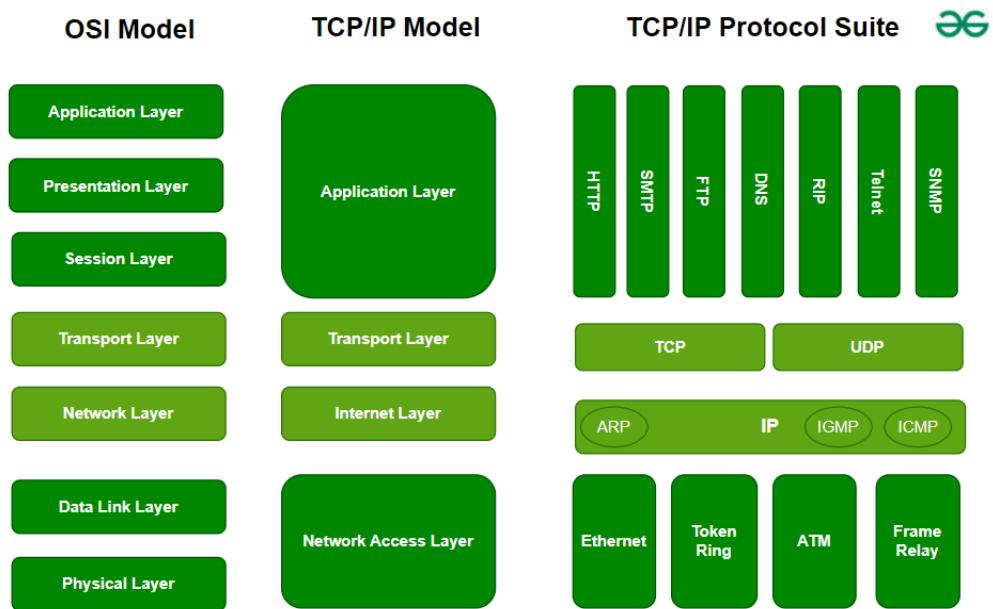

| MODELOS DE COMUNICAÇÃO                                          | 44        |

| Modelos de comunicação de propósito genérico                    | 45        |

| Modelos de comunicação para propósitos específicos              | 47        |

| ARBITRAGEM DE BARRAMENTO                                        | 51        |

| Sem mecanismo de arbitragem                                     | 52        |

| Controle centralizado                                           | 52        |

| Arbitragem simples descentralizada                              | 52        |

| Arbitragem com priorização de identificadores                   | 53        |

| GRANULARIDADE DE COMUNICAÇÃO                                    | 54        |

| MECANISMOS DE SINCRONIZAÇÃO                                     | 55        |

| Segmentação de tempo em bits                                    | 56        |

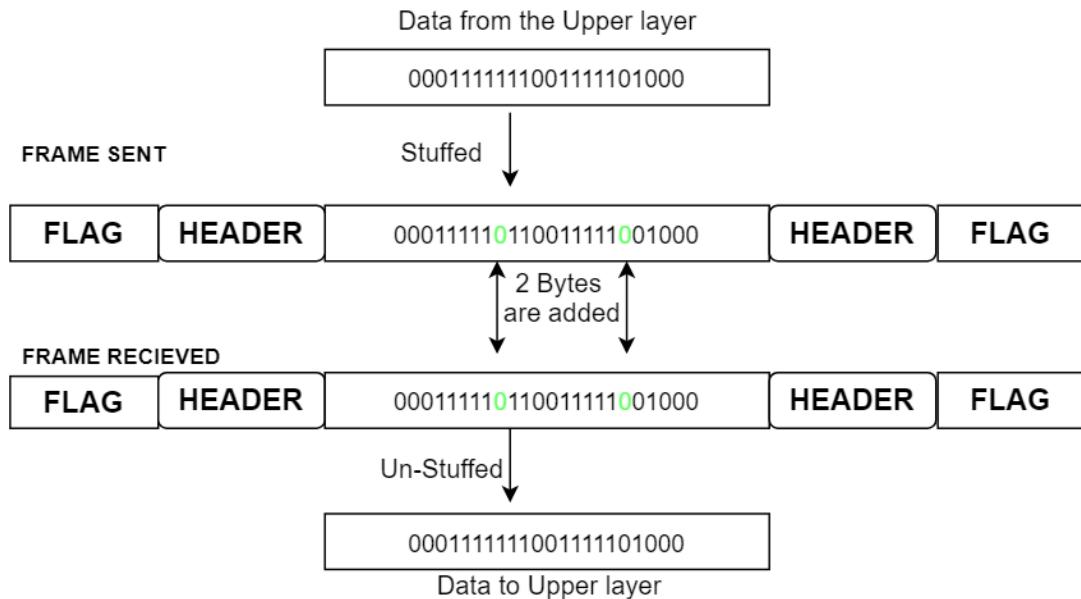

| Bit stuffing                                                    | 57        |

| Segmentação de quadros                                          | 58        |

| Sincronização de mensagens                                      | 59        |

| MECANISMOS DE ROBUSTEZ                                          | 60        |

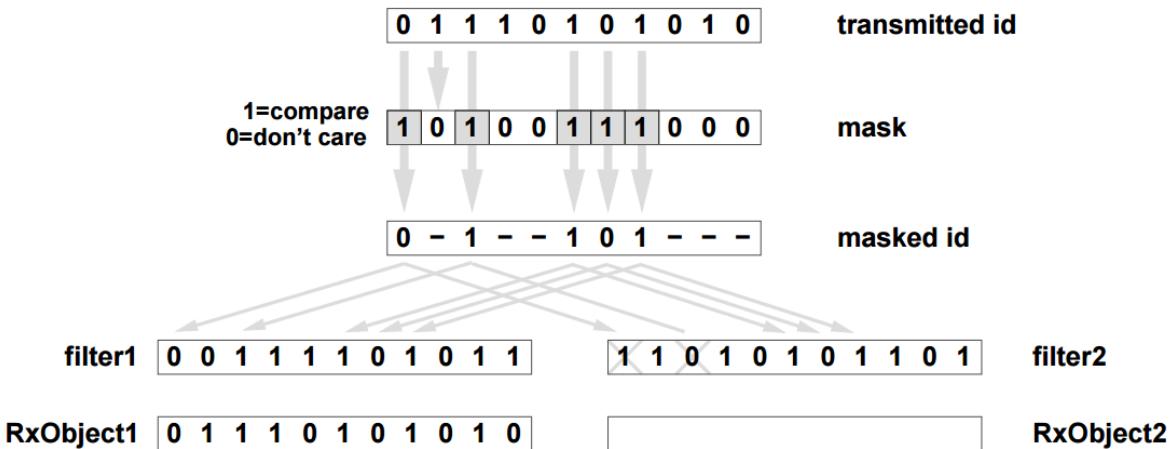

| FILTRAGENS DE MENSAGENS                                         | 63        |

| <b>PROTOCOLOS DE REDES INDUSTRIAS ESTRUTURADOS</b>              | <b>66</b> |

| PROTOCOLO DMX                                                   | 66        |

| PROTOCOLO CAN                                                   | 67        |

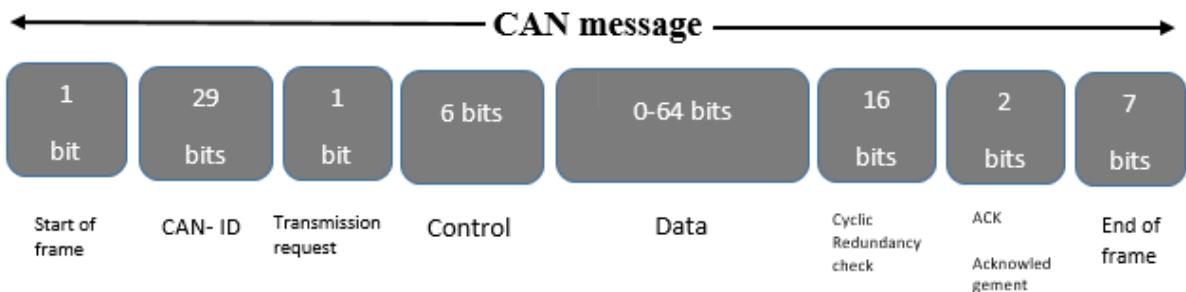

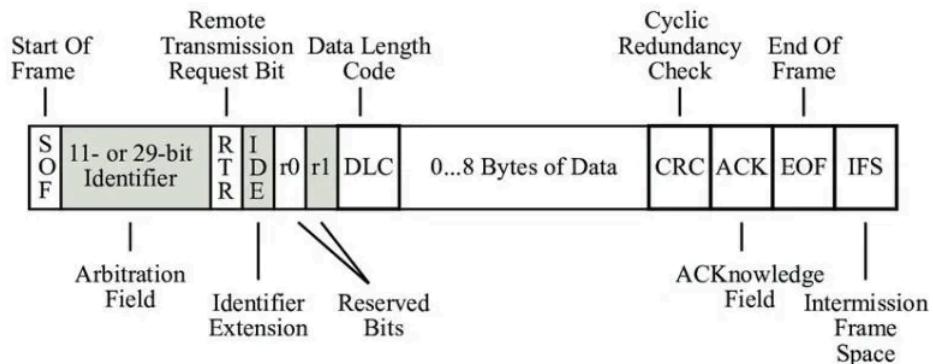

| Formato de quadro CAN                                           | 69        |

| Transceivers MCP2551                                            | 70        |

| <b>STM32H7A3: MÓDULO FDCAN</b>                                  | <b>71</b> |

## INTRODUÇÃO

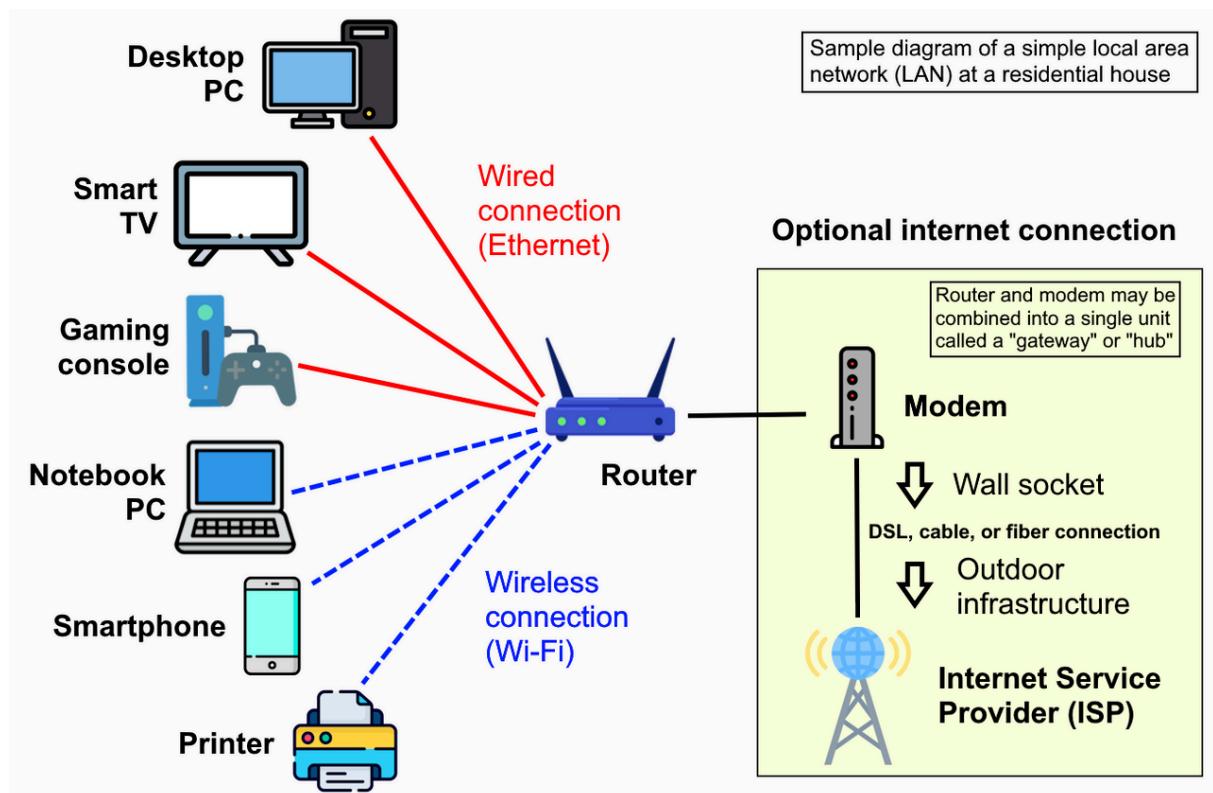

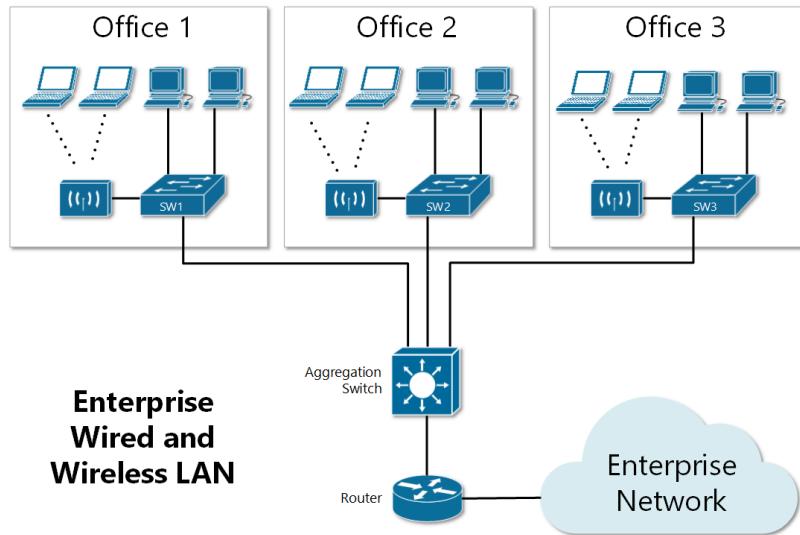

Nos sistemas embarcados modernos, sensores e atuadores são comumente integrados ao microcontrolador utilizando interfaces seriais como SPI (do inglês *Serial Peripheral Interface*) e I2C (do inglês *Inter-Integrated Circuit*). Essas interfaces são populares por sua simplicidade, baixo custo e eficiência em curtas distâncias. No Roteiro 10, vimos que o I2C é ideal para conectar múltiplos dispositivos com apenas duas linhas de comunicação (SDA e SCL), tornando-o apropriado para sistemas com restrição de espaço e número limitado de fios. Já o SPI, com suas quatro linhas (MISO, MOSI, SCLK e SS), oferece maior velocidade de comunicação e é preferido em aplicações que exigem maior taxa de transferência de dados.

Historicamente, antes do advento dessas interfaces otimizadas para comunicação interna em placas, o protocolo RS-232 foi um dos primeiros e mais difundidos padrões para comunicação serial entre dispositivos, como computadores e periféricos. Embora ainda seja encontrado em algumas aplicações legadas e se comunicam com os periféricos UART/USART dos microcontroladores através de transceptores (em inglês, *transceivers*), como um [MAX232](#), suas limitações de velocidade, distância e sensibilidade a ruído o tornaram menos adequado para as exigências de sistemas embarcados modernos e ambientes industriais.

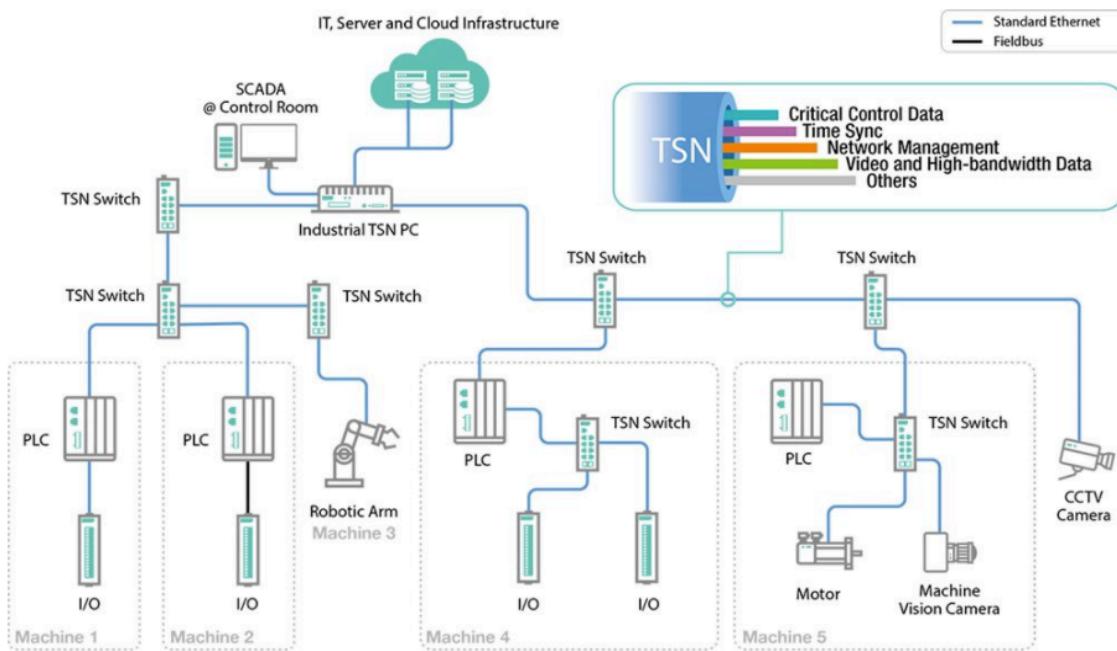

Contudo, tanto o SPI quanto o I2C (e o RS-232, em maior grau) apresentam limitações significativas em ambientes industriais e automotivos. Esses são frequentemente classificados como ambientes hostis devido à presença de ruído eletromagnético, variações extremas de temperatura, umidade e vibração mecânica. Em tais ambientes, onde falhas de comunicação podem comprometer a segurança e a funcionalidade do sistema como um todo, a evolução natural é a adoção de redes de comunicação mais resilientes, como a **rede CAN** (do inglês *Controller Area Network*). Desenvolvida originalmente para a indústria automotiva pela Bosch, a rede CAN tornou-se um padrão em sistemas embarcados críticos por diversos motivos, destacando-se:

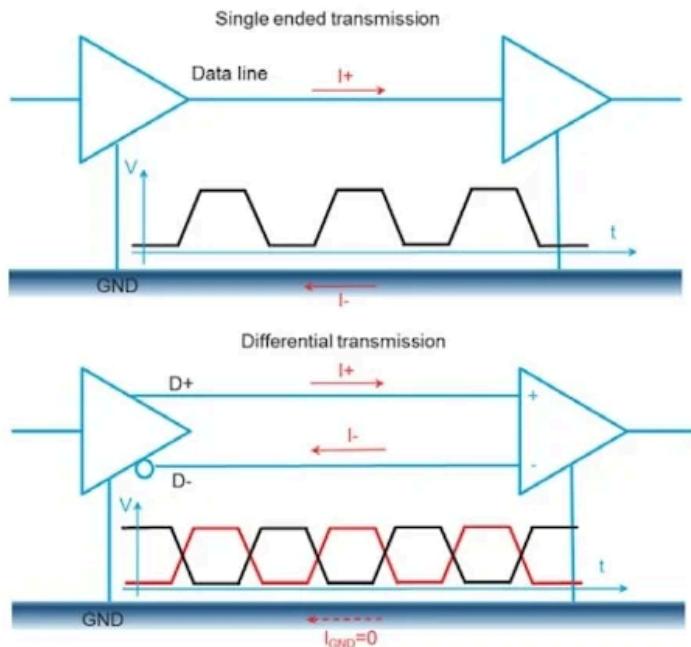

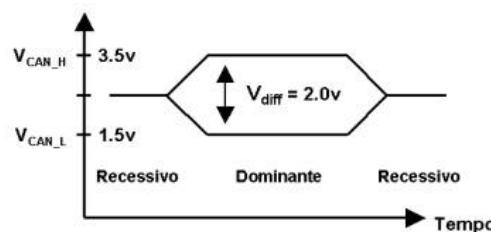

- **alta imunidade a ruídos:** Diferente dos sinais unipolares (em inglês *single-ended*) utilizados nas interfaces UART, SPI e I2C, que transmitem um sinal referenciado ao terra, o **sinal diferencial** utilizado na rede CAN transmite a informação pela diferença de potencial entre duas linhas (CAN\_H e CAN\_L), tornando-o muito mais resistente a interferências comuns no ambiente industrial e automotivo.

Fonte: [All About Circuits](#).

- **deteção e correção de erros:** O protocolo implementa mecanismos sofisticados de verificação de integridade dos dados, como CRC (do inglês *Cyclic Redundancy Check*), detecção de *bits* dominantes e recessivos, além de retransmissão automática em caso de falha.

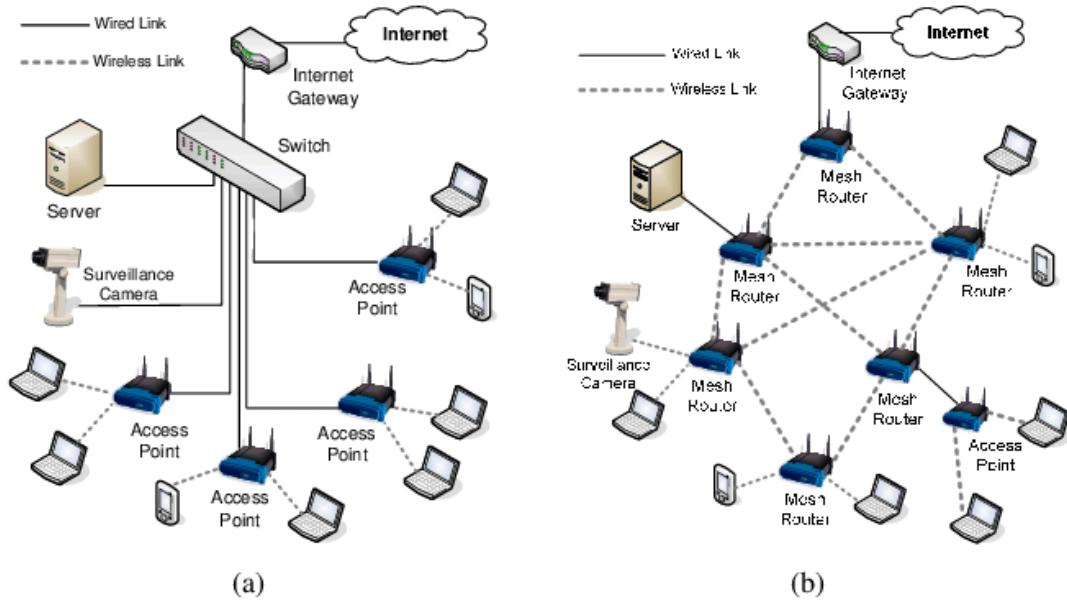

- **topologia distribuída e flexível:** Um aspecto crucial da rede CAN é a sua capacidade de gerenciar a comunicação de múltiplos nós de forma descentralizada e sem colisões, através de um sofisticado mecanismo de **arbitragem de barramento**, onde as mensagens mais prioritárias (determinadas pelo identificador) têm precedência na transmissão, garantindo previsibilidade e determinismo — requisitos fundamentais em sistemas embarcados críticos.

- **escalabilidade:** Enquanto no SPI o número de dispositivos é diretamente limitado pela necessidade de uma linha de seleção dedicada (\CS) para cada escravo, e no I2C pelo espaço de endereçamento (normalmente 7 bits, limitando a 127 dispositivos teóricos), a rede CAN permite a coexistência de múltiplos nós no mesmo barramento, com a seleção lógica baseada no conteúdo da mensagem (ID), o que oferece uma escalabilidade muito superior, além de simplificar o cabeamento.

- **alcance maior dos sinais:** Enquanto I2C e SPI são geralmente limitados a poucos metros de cabo, a rede CAN pode operar eficientemente em distâncias superiores a 40 metros em velocidades mais altas (até 1 Mbps) e até 1 km em velocidades reduzidas.

- **padrões e interoperabilidade:** A padronização da rede CAN (como CAN 2.0A/B e CAN FD) garante compatibilidade entre dispositivos de diferentes fabricantes, o que facilita a manutenção e o desenvolvimento modular de sistemas.

Além da evolução física dos meios e da robustez dos sinais, essa transição representa também uma mudança na granularidade da informação transmitida, onde passamos de protocolos que basicamente trocam bytes e bits de forma sequencial (como UART, SPI e I2C) para redes que operam no nível de **mensagens estruturadas**, cada uma identificada e tratada conforme sua prioridade ou endereço lógico no barramento. Esse conceito é essencial para compreender como redes como a CAN conseguem oferecer comunicação eficiente, escalável e determinística.

A adoção da rede CAN em sistemas embarcados marca não apenas uma evolução em termos físicos e de confiabilidade, robustez e eficiência do meio de transmissão, mas também a entrada em uma nova abordagem conceitual baseada em redes de controle distribuídas. Nesse novo paradigma, dispositivos não são apenas sensores ou atuadores isolados conectados a um microcontrolador, mas **nós inteligentes** que compartilham informações em um barramento comum e cooperam para o funcionamento de todo o sistema. Para compreender plenamente essa transição e os benefícios da rede CAN, é essencial introduzir alguns conceitos fundamentais de **redes de controle**, que irão sustentar a arquitetura e os protocolos utilizados.

Neste Roteiro, aprofundaremos nosso estudo das redes de controle. Começaremos com uma abordagem prática, explorando o periférico FDCAN (do inglês *Flexible Data-Rate Controller Area Network*) integrado no STM32H7A através de três projetos-exemplo: a implementação da função de loopback, a filtragem de identificadores e a montagem de uma rede CAN completa. Em seguida, passaremos para os fundamentos teóricos. Abordaremos as **topologias de rede** e os diversos tipos de comunicação que nelas ocorrem, os quais exigem um conceito essencial: a **arbitragem de barramento**. Introduziremos o **sinal diferencial**, contrastando-o com o sinal unipolar que abordamos anteriormente. Para garantir a confiabilidade e robustez da comunicação, apresentaremos **mecanismos modernos de detecção e correção de erros** integrados em protocolos como o CAN. Além da checagem de bit de paridade (detecção de erros em um bit) e *handshaking* (processo de negociação que pode revelar a ocorrência de um erro) já vistos em roteiros anteriores, exploraremos conceitos como verificação cíclica de redundância (em inglês, *Cyclic Redundancy Check* – CRC), *bit stuffing* e a confirmação da integridade da mensagem.

Com esses conceitos estabelecidos, mostraremos duas redes de controle práticas: a rede CAN e a rede DMX. O protocolo CAN, projetado para transmissão de dados em distâncias médias, utiliza linhas de transmissão diferencial, o que o torna ideal para cenários críticos e de alta demanda. Já o protocolo DMX é amplamente empregado no controle de iluminação e efeitos especiais, utilizando um barramento serial unidirecional para a transmissão de dados.

## PROJETOS-EXEMPLO

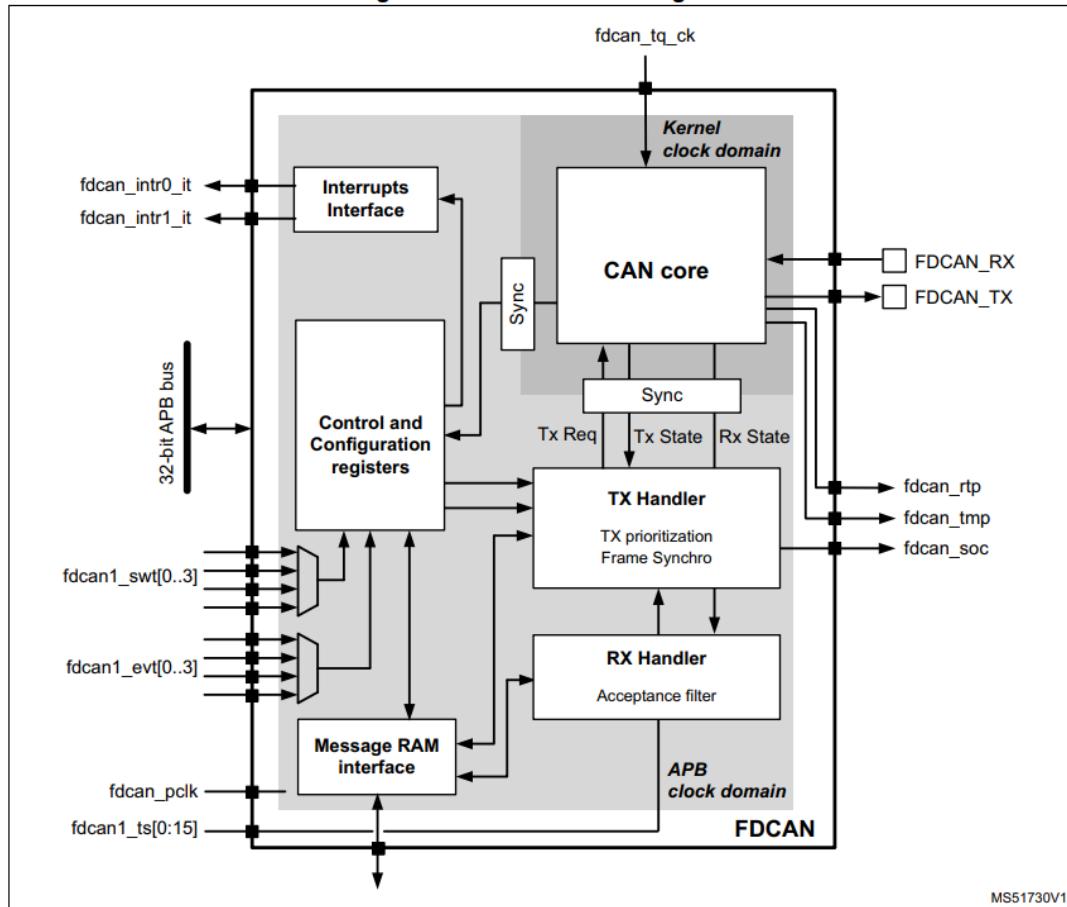

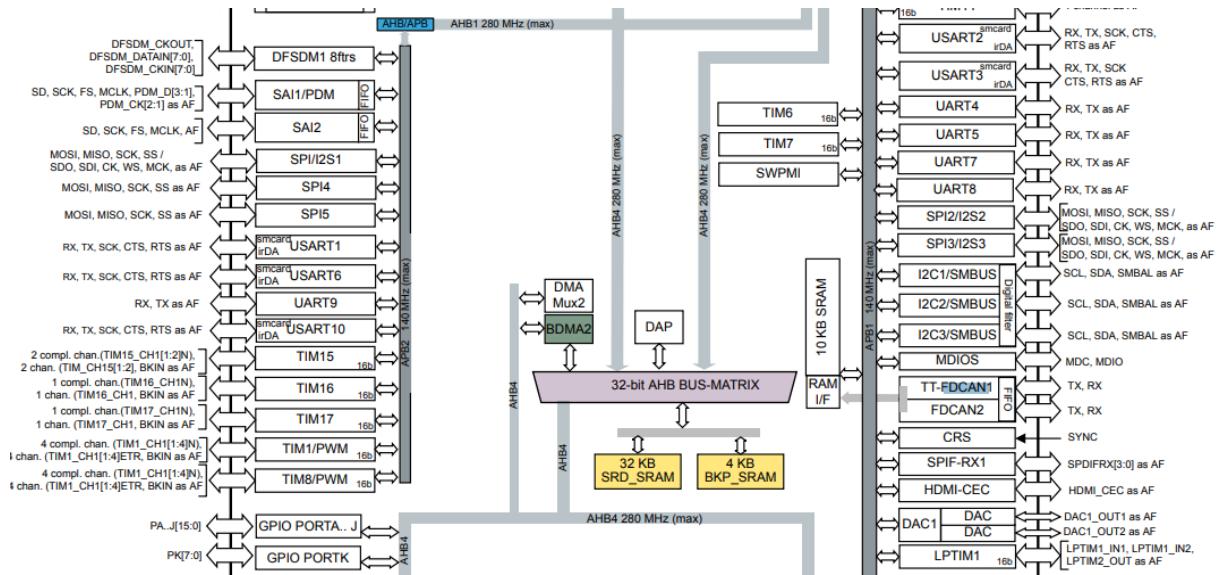

Nesta seção, exploraremos a implementação de um barramento CAN utilizando o periférico FDCAN (do inglês *Flexible Data-Rate Controller Area Network*) do microcontrolador STM32H7A. Apresentaremos três projetos práticos, organizados de forma progressiva, para introduzir os conceitos e as configurações necessárias para o barramento. O **FDCAN** é uma evolução do clássico protocolo CAN, cuja característica mais distintiva, e o motivo do “FD” no nome, é permitir que a fase de dados de um quadro CAN seja transmitida a uma taxa de *bits* mais alta do que a fase de arbitragem (onde o ID da mensagem é transmitido). Isso significa que, após a arbitragem bem-sucedida, a comunicação pode acelerar significativamente (podendo atingir 5 Mbps ou mais), otimizando a largura de banda. A fase de arbitragem continua na velocidade nominal para garantir a robustez. O STM32H7A3 possui 2 controladores FDCAN do tipo *Flexible-Datarate*, mas vamos usar apenas um deles, em modo padrão.

### Projeto de comunicação CAN usando *loopback*

Você já pensou em como testar e diagnosticar a operação de uma comunicação sem depender de ligações de *transceivers* por um par diferencial, como em uma comunicação CAN? Uma abordagem eficaz para verificar a comunicação em um barramento é o uso do recurso de **loopback**. Esse recurso consiste em estabelecer uma conexão direta entre os sinais Tx e Rx do controlador, que envia uma mensagem para si mesmo, permitindo uma verificação interna da comunicação. Esse procedimento permite que, durante a transmissão, o controlador mestre monitore se os níveis lógicos presentes na linha coincidem com os dados enviados. Sem a conexão entre Tx de um transmissor com o Rx de um receptor, o controlador pode interpretar a falta de resposta como uma colisão no barramento, levando ao abortamento da transmissão. Assim, o *loopback* não só facilita testes sem necessidade de equipamentos adicionais, mas também assegura que o controlador funcione corretamente, detectando eventuais falhas na comunicação.

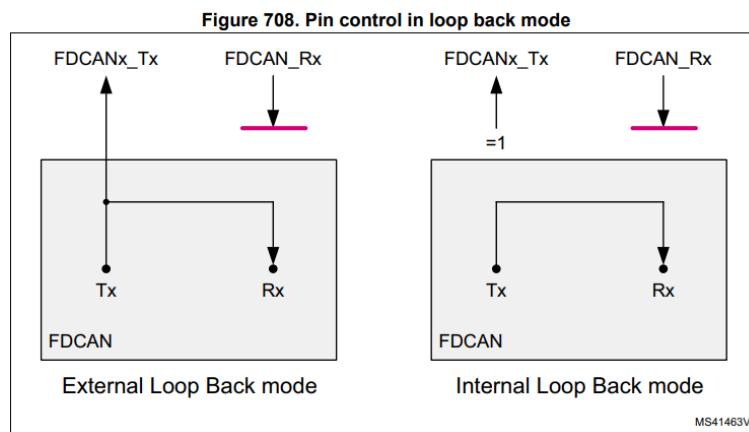

Os controladores FDCAN do STM32H7 podem ser configurados para o modo *loopback* interno ou externo, ou seja, eles não precisam de intervenção física para realizar a conexão entre seus sinais. No modo **interno**, CAN\_Tx e CAN\_Rx são ligados um ao outro, e ambos são desligados de seus pinos no encapsulamento do microcontrolador. No modo **externo**, o pino CAN\_Tx permanece ligado a seu pino correspondente. Vamos usar o *loopback* externo para que se possa visualizar os sinais do controlador, conectando-se o analisador lógico ao pino CAN\_Tx.

1. Crie um projeto chamado “CAN\_Base”, sem inicializar os periféricos. Ative o *Debug*. Selecione HSI como fonte do *Clock* do Sistema e mantenha o *clock* geral em 64MHz (configurações padrão). Gere o código.

2. Abra o arquivo “main.c”. Vamos criar variáveis globais para os *buffers* de dados de transmissão e recepção e uma variável geradora de dados. Na seção **/\* USER CODE BEGIN PV \*/**

```

uint8_t TxData[8];

uint8_t RxData[8];

int indx = 0;

```

Insira no escopo **/\* USER CODE BEGIN PFP \*/** os protótipos das funções que implementaremos

```

void FDCAN2_Init(void);

void FDCAN2_AddMessageToTxFifoQ(uint32_t id);

void FDCAN2_GetMessageFromRxFifo0(void);

void FDCAN2_AlocaSRamCANSegmentos(void);

uint8_t Code2ByteCounter(uint8_t code);

```

3. Vamos implementar as 5 funções no escopo **/\* USER CODE BEGIN 4 \*/**. Para a primeira função de inicialização do FDCAN, insira o seguinte código:

```

void FDCAN2_Init () {

{

//Configura o sinal de relogio pll1_q_ck para fdcan_ker_clk

//A fonte HSI ja eh habilitada e configurada pelo MxCube

//Desabilita PLL1

RCC->CR &= ~RCC_CR_PLL1ON;

while (RCC->CR & RCC_CR_PLL1RDY); //aguarda a desabilitacao

//Configura pre-scaler e DIVM1

RCC->PLLCKSELR &= ~(RCC_PLLCKSELR_PLLSRC |

RCC_PLLCKSELR_DIVM1);

RCC->PLLCKSELR |= RCC_PLLCKSELR_DIVM1_2; // 0x4

//Configura os fatores de divisoes/multiplicacoes

RCC->PLL1DIVR &= ~(RCC_PLL1DIVR_N1 |

RCC_PLL1DIVR_Q1);

RCC->PLL1DIVR |= (((12U-1U) << RCC_PLL1DIVR_N1_Pos) |

((2U-1U) << RCC_PLL1DIVR_Q1_Pos));

//Configura o fator fracionario

RCC->PLL1FRACR = (4096U << RCC_PLL1FRACR_FRACN1_Pos);

//Faixa de frequencias de operacao de PLL1 ( 8 a 16 MHz)

```

```

RCC->PLLCFGR |= RCC_PLLCFGR_PLL1RGE;

//Faixa de frequencia de VCO usado por PLL1 (128 a 560 MHz)

RCC->PLLCFGR &= ~RCC_PLLCFGR_PLL1VCOSEL;

//Habilita as configuracoes dos divisores

RCC->PLLCFGR |= (RCC_PLLCFGR_PLL1FRACEN |

RCC_PLLCFGR_DIVQ1EN );

// Reativar PLL1

RCC->CR |= RCC_CR_PLL1ON;

while (!(RCC->CR & RCC_CR_PLL1RDY)); //aguarda a ativacao

}

{

//Ativar clock gating de FDCAN e dos perifericos necessarios a sua

operacao

// Seleciona ker_ck para FDCAN (pll1_q_ck)

RCC->PLLCFGR |= RCC_PLLCFGR_DIVQ1EN_Msk; // habilita pll1_q_ck

RCC->CDCCIP1R &= ~RCC_CDCCIP1R_FDCANSEL_Msk; // fonte para FDCAN

RCC->CDCCIP1R |= RCC_CDCCIP1R_FDCANSEL_0;

// Habilita o clock do FDCAN2

RCC->APB1HENR |= RCC_APB1HENR_FDCANEN;

/** Configura os pinos FDCAN2 GPIO

PB13      -----> FDCAN2_TX

PB5       -----> FDCAN2_RX

*/

RCC->AHB4ENR |= (RCC_AHB4ENR_GPIOBEN);

// Configura o pino FDCAN2_TX

GPIOB->MODER &= ~(GPIO_MODER_MODE13_Msk); // Limpar modos

GPIOB->MODER |= GPIO_MODER_MODE13_1; // Modo alternativo

// Seleciona a função alternativa FDCAN2_TX (AF9) para o pino

GPIOB->AFR[1] &= ~(GPIO_AFRH_AFSEL13_Msk); // AF9 para PB13

GPIOB->AFR[1] |= (GPIO_AFRH_AFSEL13_0); // AF9 para PB13

GPIOB->AFR[1] |= (GPIO_AFRH_AFSEL13_3); // AF9 para PB13

GPIOB->OSPEEDR &= ~(GPIO_OSPEEDR_OSPEED13_Msk); //Baixa velocidade

// Configurar o pino FDCAN2_RX

GPIOB->MODER &= ~(GPIO_MODER_MODE5_Msk); // Limpar modos

GPIOB->MODER |= GPIO_MODER_MODE5_1; // Modo alternativo

// Selecionar a função alternativa FDCAN2_RX (AF9) para o pino

GPIOB->AFR[0] &= ~(GPIO_AFRL_AFSEL5_Msk); // AF9 para PB5

GPIOB->AFR[0] |= (GPIO_AFRL_AFSEL5_0); // AF9 para PB5

GPIOB->AFR[0] |= (GPIO_AFRL_AFSEL5_3); // AF9 para PB5

GPIOB->OSPEEDR &= ~(GPIO_OSPEEDR_OSPEED5_Msk); // Baixa velocidade

/* Habilita IRQ correspondente a FDCAN2 interrupt Init (Linha de

interrupção 0) */

NVIC_SetPriority(FDCAN2_IT0_IRQn, 1);

NVIC_EnableIRQ(FDCAN2_IT0_IRQn);

}

{

//Chaveia para o modo de inicializacao

//Sair do modo Sleep

FDCAN2->CCCR &= ~FDCAN_CCCR_CSR;

/* Check Sleep mode acknowledge */

while ((FDCAN2->CCCR & FDCAN_CCCR_CSA) == FDCAN_CCCR_CSA);

// Coloca o FDCAN em modo de inicializacao

FDCAN2->CCCR |= FDCAN_CCCR_INIT; // Ativa o modo de inicializacao

// Aguarda até que o modo de inicializacao seja efetivo

while (!(FDCAN2->CCCR & FDCAN_CCCR_INIT));

}

{

//Configuracao dos registradores de FDCAN propriamente dito

```

```

FDCAN2->CCCR |= FDCAN_CCCR_CCE_Msk; // Habilita a configuração

// Desabilita retransmissao automatica

FDCAN2->CCCR |= FDCAN_CCCR_DAR_Msk;

// Desabilita o recurso de pausa de transmissao

FDCAN2->CCCR &= ~FDCAN_CCCR_TXP_Msk;

// Desabilita protocolo de processamento de excecao

FDCAN2->CCCR |= FDCAN_CCCR_PXHD_Msk;

// Defina o formato de quadro/campo de dados (Quadro Classico)

FDCAN2->CCCR &= ~(FDCAN_CCCR_FDOE |

FDCAN_CCCR_BRSE);

// Defina o modo de operacao (Loopback externo)

FDCAN2->CCCR &= ~(FDCAN_CCCR_TEST |

FDCAN_CCCR_MON |

FDCAN_CCCR_ASM);

FDCAN2->TEST &= ~FDCAN_TEST_LBCK;

FDCAN2->CCCR |= FDCAN_CCCR_TEST;

FDCAN2->TEST |= FDCAN_TEST_LBCK;

// Configura o tempo de amostragem e prescalers para o tempo de bit

// nominal (Formato de quadro classico)

// Configuracao de tempo de bit de dados apenas no modo FD + BRS.

FDCAN2->NBTP = (((uint32_t)13 - 1U) << FDCAN_NBTP_NSJW_Pos) |

(((uint32_t)86U - 1U) << FDCAN_NBTP_NTSEG1_Pos) //Nom.Time Segm. 1

(((uint32_t)13U - 1U) << FDCAN_NBTP_NTSEG2_Pos) //Nom.Time Segm. 2

((uint32_t)1U - 1U) << FDCAN_NBTP_NBRP_Pos); //Nom.BitRate PScaler

}

{

// Configura tamanho do campo/quadro/frame de dados para TX e RX

// Define o uso do buffer TxFIFO para transmissao

FDCAN2->TXBC &= ~FDCAN_TXBC_TFQM_Msk;

// Configurar o tamanho de cada campo/quadro/frame de dados de uma mensagem TX (8 bytes)

FDCAN2->TXESC &= ~FDCAN_TXESC_TBDS_Msk;

// Configura tamanho de cada campo de dados de uma mensagem RX (8 bytes)

FDCAN2->RXESC &= ~FDCAN_RXESC_F0DS_Msk;

}

{

//Configura enderecos iniciais de cada segmento em SRAMCAN

//Cada unidade do segmento tem 32 bits (4U bytes)

//RX FIFO 0: 1 mensagem de 8 bytes de dados + 8 bytes de cabecalho

//TX FIFO: 1 mensagem de 8 bytes de dados + 8 bytes de cabecalho

FDCAN2_AlocaSRamCANSegmentos ();

}

{

// Sai do modo de inicialização

FDCAN2->CCCR &= ~FDCAN_CCCR_INIT; // Desativa o modo de inicialização

// Aguarda até que o modo de inicialização seja efetivo

while ((FDCAN2->CCCR & FDCAN_CCCR_INIT));

}

{

// Habilita a linha de interrupcao 0

FDCAN2->ILE |= FDCAN_ILE_EINT0; // habilita a linha de interrupcao

FDCAN2->IE |= FDCAN_IE_RFONE; // habilita evento para novas mensagens na Rx FIFO

FDCAN2->ILS &= ~FDCAN_ILS_RF0NL; //associa a linha de interrupcao 0

}

}

```

Note que, por didática, as instruções foram agrupadas em 8 blocos delimitados pelas chaves.

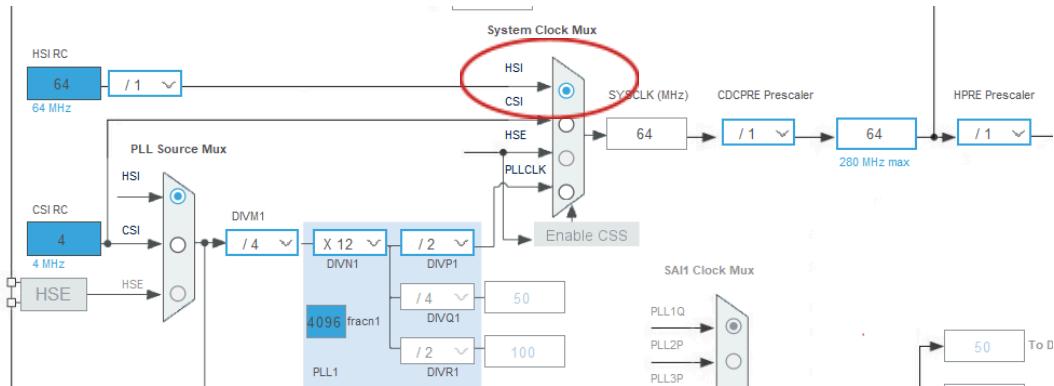

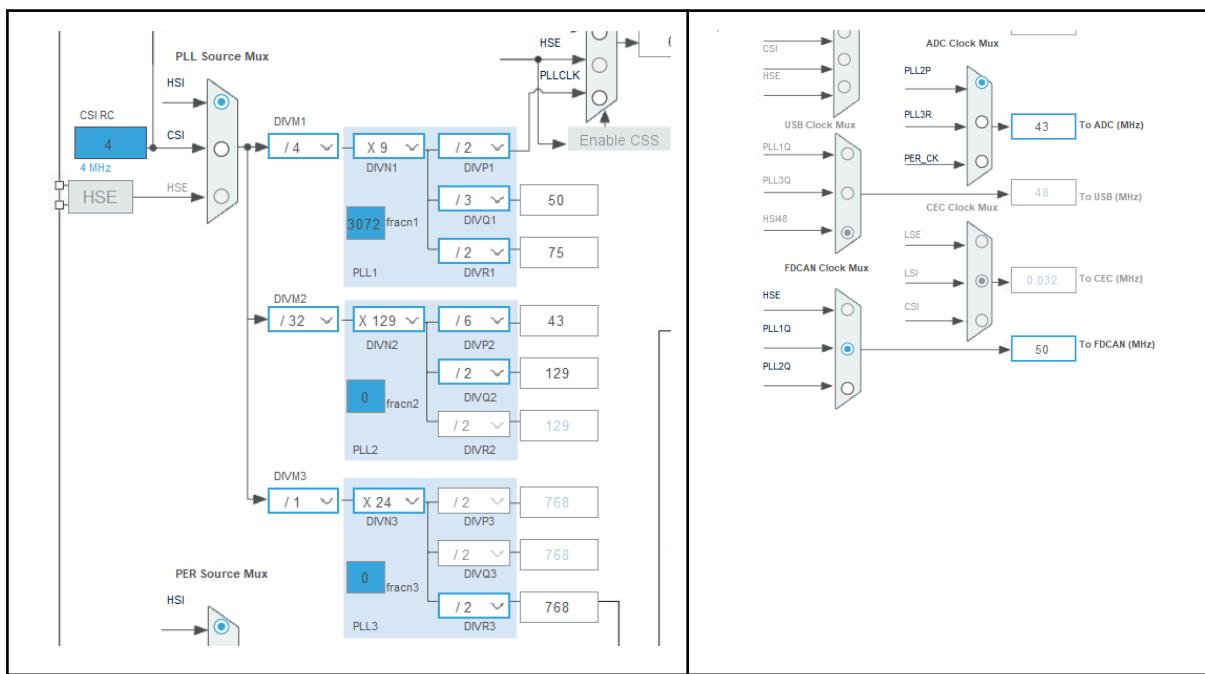

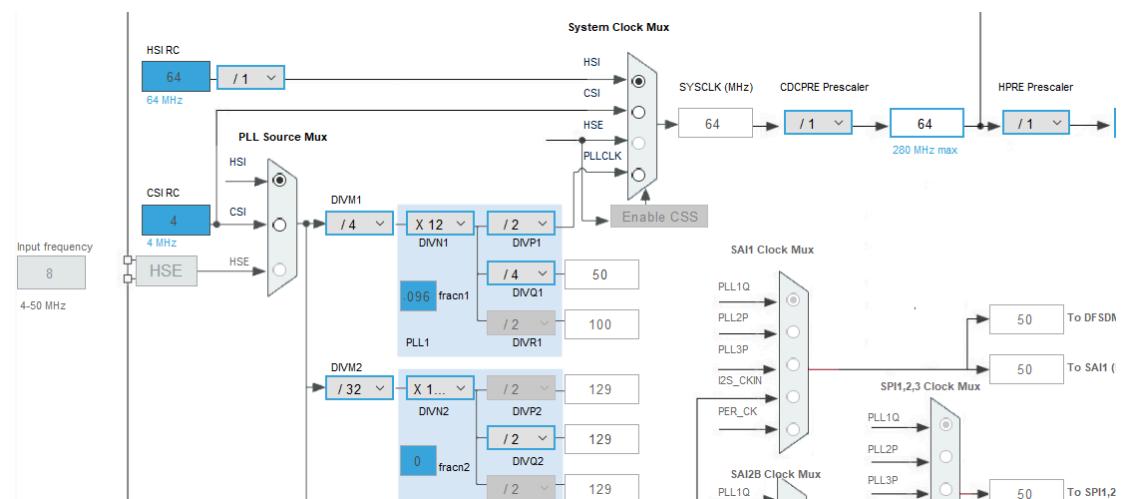

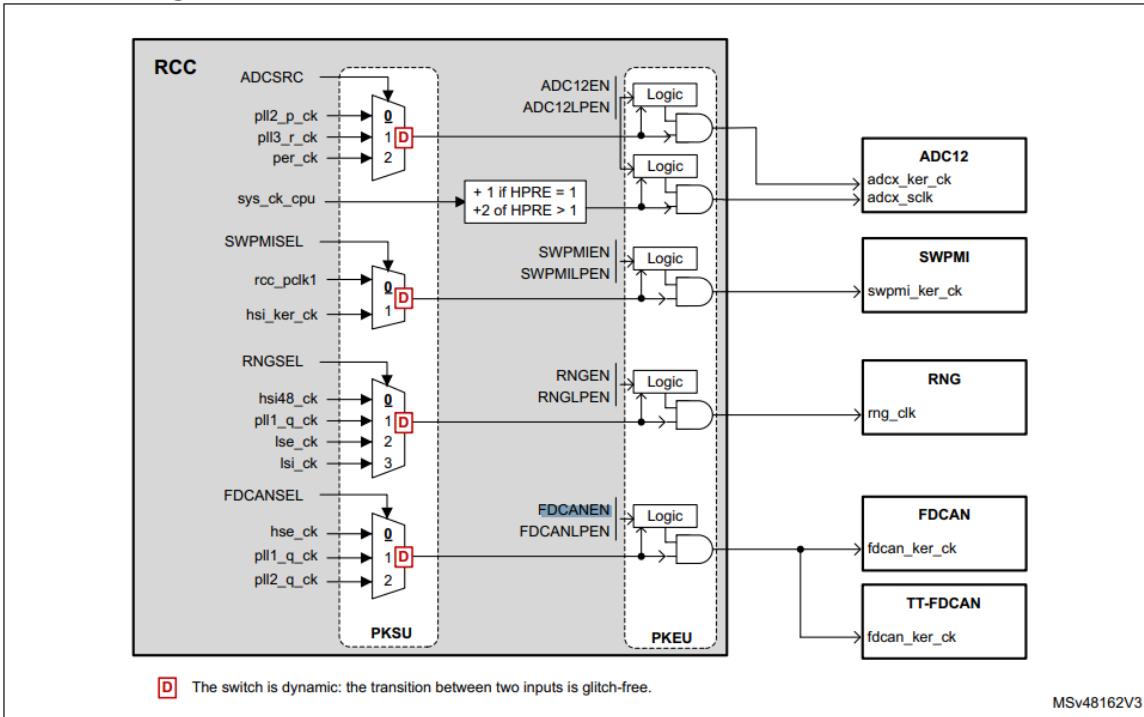

O primeiro bloco configura o circuito PLL1 (do inglês *Phase-Locked Loop 1*) do microcontrolador STM32H7A para gerar um sinal de *clock* de 50MHz para o periférico FDCAN. O objetivo é ajustar a “velocidade” e a “precisão” do sinal de relógio que o FDCAN usará para operar em 50MHz. Durante a configuração, o PLL1 é temporariamente desabilitado. A fonte de *clock* HSI (*clock* padrão) é usada, e um *prescaler* de 4 é aplicado antes de entrar no PLL1. Em seguida, os fatores de divisão e multiplicação, incluindo o fator fracionário do PLL1, são configurados para que o sinal de saída final seja de 50MHz. Por fim, as configurações dos divisores são habilitadas antes de reabilitar PLL1. A figura a seguir sintetiza os campos de *bits* configurados, resultando em um sinal de 50MHz para o FDCAN. É importante assegurar que a faixa de frequências de operação do PLL1 estar entre 8 e 16 MHz e a faixa de frequência do VCO (do inglês, *Voltage Controlled Oscillator*), utilizado pelo PLL1, entre 128 e 560 MHz.

O segundo bloco realiza a habilitação e configuração inicial do periférico FDCAN2 e seus pinos GPIO associados no microcontrolador STM32H7A, além de configurar a interrupção. Ele prepara o *hardware* para que o FDCAN2 possa se comunicar. O código primeiramente habilita o *clock gating* para o FDCAN2 e seus componentes auxiliares, garantindo que recebam energia e sinais de *clock*. Ele seleciona `p111_q_ck` (o *clock* de 50MHz configurado anteriormente) como a fonte de *clock* principal para o FDCAN. Em seguida, as linhas GPIO PB13 (para FDCAN2\_TX) e PB5 (para FDCAN2\_RX) são configuradas em modo de função alternativa (AF9), conectando-as internamente ao periférico FDCAN2. Por fim, a interrupção FDCAN2\_IT0\_IRQn é habilitada e configurada com prioridade 0, permitindo que o microcontrolador responda a eventos específicos do FDCAN2.

O terceiro bloco de instruções coloca o periférico FDCAN2 no modo de inicialização (em inglês *Initialization mode*). O código garante que o FDCAN2 saia do modo *Sleep*, um estado de baixa energia, para então ativá-lo no modo de inicialização. Este modo é essencial, pois permite a configuração dos parâmetros operacionais do FDCAN, como as taxas de *baud*, filtros, e outros ajustes antes que o periférico possa começar a enviar ou receber mensagens na rede CAN. O código também inclui laços de *while* para aguardar a confirmação de que o FDCAN2 realmente saiu do *Sleep* e entrou no modo de inicialização, garantindo que as próximas configurações sejam aplicadas corretamente.

O quarto bloco de instruções realiza a configuração detalhada dos parâmetros operacionais do periférico FDCAN2, incluindo o modo de comunicação, regras de retransmissão e a

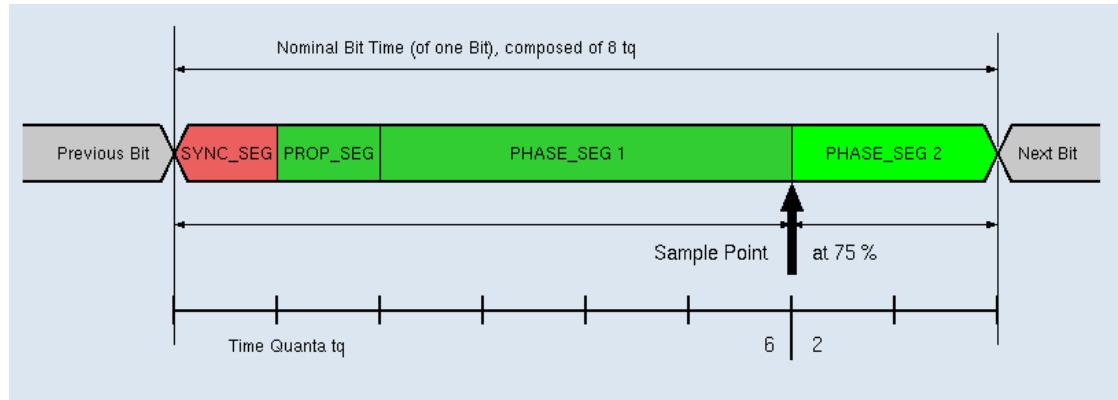

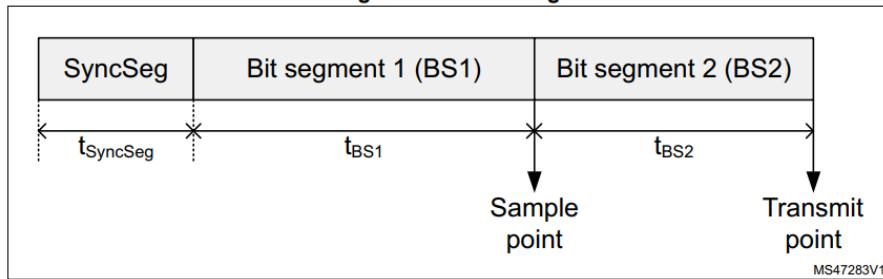

temporização de *bits*. O código habilita o modo de configuração do FDCAN2 (CCE) e, em seguida, desabilita a retransmissão automática (DAR) e o recurso de pausa de transmissão (TXP). Ele também desativa o processamento de exceção de protocolo (PXHD) e define o formato do quadro como CAN Clássico, desabilitando as funcionalidades *Flexible Data-Rate* (FDOE) e *Bit Rate Switch* (BRSE). Além disso, configura o FDCAN2 para **operar em modo Loopback Externo**. Por fim, o código ajusta os parâmetros de temporização nominal do *bit* (NBTP), incluindo o *prescaler* de taxa de *bit*, os segmentos de tempo (NTSEG1, NTSEG2) e a largura do *jump* de sincronização (NSJW). Esses tempos são relacionados com a taxa de transmissão do FDCAN e são cruciais para garantir a correta sincronização e comunicação na rede CAN. As seguintes figuras sumarizam os valores configurados neste bloco. Note na última linha que a *baud rate* nominal estabelecida é de 500.000 *bits* por segundo.

| Basic Parameters        |                        |

|-------------------------|------------------------|

| Frame Format            | Classic mode           |

| Mode                    | External LoopBack mode |

| Auto Retransmission     | Disable                |

| Transmit Pause          | Disable                |

| Protocol Exception      | Disable                |

| Nominal Sync Jump Width | 13                     |

| Data Prescaler          | 25                     |

| Data Sync Jump Width    | 1                      |

| Data Time Seg1          | 2                      |

| Data Time Seg2          | 1                      |

| Clock Calibration Unit   |              |

|--------------------------|--------------|

| Clock Calibration        | Disable      |

| Bit Timings Parameters   |              |

| Nominal Prescaler        | 1            |

| Nominal Time Quantum     | 20.0 ns      |

| Nominal Time Seg1        | 86           |

| Nominal Time Seg2        | 13           |

| Nominal Time for one Bit | 2000 ns      |

| Nominal Baud Rate        | 500000 bit/s |

O quinto bloco realiza a configuração do tamanho dos campos de dados (*payload*) para as mensagens de transmissão (TX) e recepção (RX) do periférico FDCAN2, além de definir o modo de operação da fila de transmissão. O código primeiro define que o FDCAN2 usará uma fila de transmissão (TxFIFO) em vez de *buffers* dedicados, limpando o *bit* TFQM. Em seguida, ele configura o tamanho da carga útil (*payload*) para as mensagens de transmissão (TXESC) e recepção (RXESC) para 8 *bytes* cada. Essa configuração é essencial para o FDCAN2, especialmente quando operando em modo CAN Clássico (onde o *payload* máximo é 8 *bytes*, como configurado no bloco anterior), garantindo que o controlador saiba o volume de dados que espera enviar e receber por mensagem.

O sexto bloco configura as áreas de memória RAM dedicadas ao periférico FDCAN2 para armazenar filtros, *buffers* de recepção e transmissão. Essas instruções são agrupadas na função `FDCAN2_AlocaSRamCANSegmentos` que implementaremos e detalharemos no próximo item.

O sétimo bloco tira o periférico FDCAN2 do modo de inicialização, tornando-o operacional para a transmissão e recepção de dados na rede CAN. O código desativa o *bit* INIT no registrador CCCR do FDCAN2, o que o remove do modo de inicialização. Em seguida, um laço while é utilizado para aguardar a confirmação de que o periférico realmente saiu desse modo. Após a execução bem-sucedida deste bloco, o FDCAN2 estará pronto para participar ativamente da comunicação no barramento CAN, seja enviando ou recebendo mensagens, de acordo com as configurações previamente estabelecidas.

Por último, o oitavo bloco habilita a linha de interrupção 0 do FDCAN2 e a configura para disparar quando uma nova mensagem é recebida na *Rx FIFO 0*. O código habilita a linha de interrupção 0 (EINT0) no registrador ILE do FDCAN2, que é o ponto de entrada para o sistema de interrupções. Em seguida, ele ativa o evento específico de interrupção para novas mensagens na *Rx FIFO 0* (RF0NE) através do registrador IE. Por fim, o código associa explicitamente este evento à linha de interrupção 0, garantindo que o microcontrolador será notificado via interrupção sempre que uma nova mensagem CAN for recebida e armazenada na *Rx FIFO 0* do FDCAN2.

4. Vamos implementar a função FDCAN2\_AlocaSRamCANSegmentos, adicionando o seguinte código depois da função FSCAN2\_Init.

```

void FDCAN2_AlocaSRamCANSegmentos (void) {

uint32_t Origem = 0;

/* Endereço inicial da lista de filtros padrão (Standard ID Filter List)

*/

MODIFY_REG(FDCAN2->SIDFC, FDCAN_SIDFC_FLSSA, (Origem <<

FDCAN_SIDFC_FLSSA_Pos));

/* Quantidade de elementos na lista de filtros padrão (cada elemento = 1

palavra de 32 bits) */

MODIFY_REG(FDCAN2->SIDFC, FDCAN_SIDFC_LSS, (1U << FDCAN_SIDFC_LSS_Pos));

/* Endereço inicial de Rx FIFO 0 */

Origem += (1U); // Avança 1 palavra apos os filtros

MODIFY_REG(FDCAN2->RXF0C, FDCAN_RXF0C_F0SA, (Origem <<

FDCAN_RXF0C_F0SA_Pos));

/* Quantidade de elementos na Rx FIFO 0 (cada elemento tem o tamanho fixo

configurado do payload maximo. Para payload de ate 8 bytes são 16 bytes -

4 palavras de 32 bits (2 de header + 2 de carga util). */

MODIFY_REG(FDCAN2->RXF0C, FDCAN_RXF0C_F0S, (1U << FDCAN_RXF0C_F0S_Pos));

/* Endereço inicial de Tx buffer */

Origem += (4U); // Avança 4 palavras (tamanho fixo de 1 elemento RX FIFO0)

MODIFY_REG(FDCAN2->TXBC, FDCAN_TXBC_TBSA, (Origem <<

FDCAN_TXBC_TBSA_Pos));

/* Quantidade de elementos Tx FIFO/queue */

MODIFY_REG(FDCAN2->TXBC, FDCAN_TXBC_TFQS, (1U << FDCAN_TXBC_TFQS_Pos));

/* Zera o conteúdo da área reservada

(soma das palavras dos filtros, RX FIFO e TX FIFO) */

for (uint32_t RAMcounter = SRAMCAN_BASE; RAMcounter <

SRAMCAN_BASE+(1U+4U+4U)*4U; RAMcounter += 4U)

{

*(uint32_t *) (RAMcounter) = 0x00000000;

}

}

```

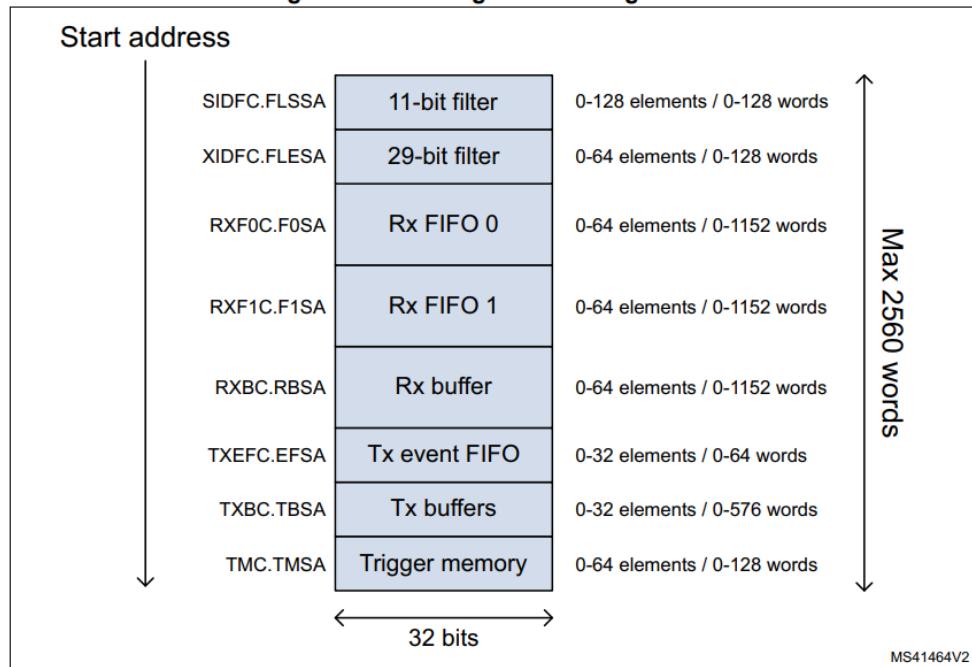

Os periféricos FDCAN exigem uma região de memória interna dedicada para processar diversas estruturas de dados, como filtros, *buffers* de recepção e transmissão. Essa área é chamada de *CAN Message RAM*, ou SRAM CAN, e deve ser alocada manualmente em uma região apropriada da SRAM do microcontrolador. O endereço base dessa RAM é configurado por meio da macro `SRAMCAN_BASE`, que informa aos periféricos FDCAN onde começam seus dados dentro da memória RAM. A macro está definida no arquivo `stm32h7a3xxq.h`. É importante notar que todos os endereços utilizados pelos registradores internos dos periféricos FDCAN são, na verdade, *offsets* relativos a esse endereço base da SRAM CAN, e não endereços absolutos da CPU.

A função `FDCAN2_AlocaSRamCANSegmentos` é responsável por gerenciar o *layout* da SRAM CAN, definindo os endereços iniciais e os tamanhos das estruturas de dados. Ela configura o endereço de início e o número de elementos para a lista de filtros padrão (SIDFC). Em seguida, estabelece o endereço de início e a capacidade da *Rx FIFO 0 (RXF0C)*. Por fim, define o endereço de início e o tamanho da fila/*buffer* de transmissão (TXBC). A variável `Origem` é utilizada para calcular esses endereços de forma incremental dentro da SRAM CAN. Após a configuração das posições, o código limpa toda a área da memória que será utilizada, preenchendo-a com zeros para assegurar um estado inicial limpo antes das operações do FDCAN2. Segue-se um resumo do *layout* configurado com `FDCAN2_AlocaSRamCANSegmentos` para a CAN Message RAM do FDCAN2.

|                         |                    |

|-------------------------|--------------------|

| Message Ram Offset      | 0                  |

| Std Filters Nbr         | 1                  |

| Ext Filters Nbr         | 0                  |

| Rx Fifo0 Elmts Nbr      | 1                  |

| Rx Fifo0 Elmt Size      | 8 bytes data field |

| Rx Fifo1 Elmts Nbr      | 0                  |

| Rx Fifo1 Elmt Size      | 8 bytes data field |

| Rx Buffers Nbr          | 0                  |

| Rx Buffer Size          | 8 bytes data field |

| Tx Events Nbr           | 0                  |

| Tx Buffers Nbr          | 0                  |

| Tx Fifo Queue Elmts Nbr | 1                  |

| Tx Fifo Queue Mode      | FIFO mode          |

| Tx Elmt Size            | 8 bytes data field |

A macro `MODIFY_REG` definida no arquivo-cabeçalho `stm32h7a3xxq.h`

```

#define MODIFY_REG(REG, CLEARMASK, SETMASK) \

((REG) = (((REG) & (~ (CLEARMASK))) | (SETMASK)))

```

realiza dois passos atômicos em um único comando: aplica a máscara `CLEARMASK` para zerar os *bits* que se quer alterar e a máscara `SETMASK` para setar os novos valores desses *bits*. Os *bits* que não estão envolvidos nas máscaras **permanecem inalterados**.

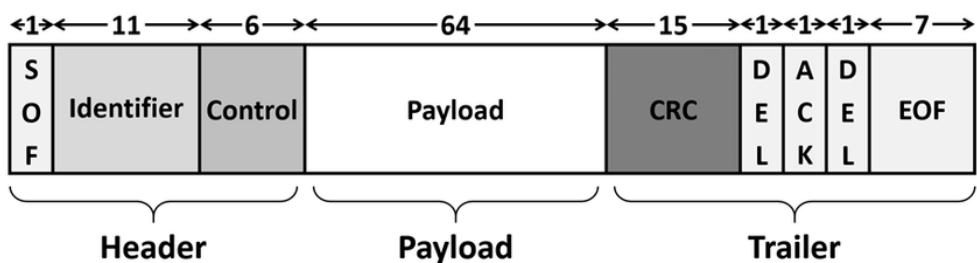

5. Diferentemente de protocolos como UART, SPI e I2C, que operam com a transmissão sequencial de *bytes* (ou *bits*), o protocolo CAN é orientado à mensagem. Isso significa que, no CAN, o que circula pela rede não são *bytes* isolados enviados de um transmissor para um receptor, mas sim mensagens estruturadas e autocontidas, compostas por campos bem definidos como identificador, controle, dados, verificação e delimitação. Vamos adicionar as

funções FDCAN2\_AddMessageToTxFifoQ e Code2ByteCounter para envio de mensagens em /\* USER CODE BEGIN 4 \*/

```

uint8_t Code2ByteCounter(uint8_t code) {

uint8_t ByteCounter = 0;

switch (code) { // Do codigo binario para ...

case 0:

ByteCounter = 8;

break;

case 1:

ByteCounter = 12;

break;

case 2:

ByteCounter = 16;

break;

case 3:

ByteCounter = 20;

break;

case 4:

ByteCounter = 24;

break;

case 5:

ByteCounter = 32;

break;

case 6:

ByteCounter = 48;

break;

case 7:

ByteCounter = 64;

break;

}

return (ByteCounter);

}

void FDCAN2_AddMessageToTxFifoQ (uint32_t id) {

uint32_t PutIndex;

uint32_t TxElementW1;

uint32_t TxElementW2;

uint32_t *TxAddress;

uint32_t ByteCounter;

if ((FDCAN2->TXBC & FDCAN_TXBC_TFQS) && !(FDCAN2->TXFQS &

FDCAN_TXFQS_TFQF)) {

// Le o indice do buffer TxFIFO/Queue

PutIndex = (FDCAN2->TXFQS & FDCAN_TXFQS_TFQPI) >> FDCAN_TXFQS_TFQPI_Pos;

// Monta a primeira palavra do cabecalho

TxElementW1 = ((0x0 << 31) | //FDCAN_ESI_ACTIVE

(0b0 << 30) | // FDCAN_STANDARD_ID

(0b0 << 29) | // FDCAN_DATA_FRAME

(id << 18U)); //Identifier padrao nos bits [28:18]

// Monta a segunda palavra do cabecalho

TxElementW2 = ((0x00 << 24U) | // Message Marker

(0b0 << 23U) | // FDCAN_NO_TX_EVENTS

(0b0 << 21U) | // FDCAN_CLASSIC_CAN

(0b0 << 20U) | // FDCAN_BRS_OFF

(0b1000 << 16U)); // DataLength (8-bytes)

/* Calcula o endereco do buffer TxFIFO/Queue */ */

TxAddress = (uint32_t *) (SRAMCAN_BASE+ (1U+4U)*4U +

```

```

(PutIndex* ((FDCAN2->TXBC & FDCAN_TXBC_TFQS) >> FDCAN_TXBC_TFQS_Pos)*4U));

/* Escreve 2 palavras de cabeçalho na RAM de mensagens CAN */

*TxAuxAddress = TxElementW1;

TxAuxAddress++;

*TxAuxAddress = TxElementW2;

TxAuxAddress++;

/* Escreve dados da mensagem */

ByteCounter = Code2ByteCounter ((FDCAN2->TXESC & FDCAN_TXESC_TBDS) >>

FDCAN_TXESC_TBDS_Pos);

for (uint8_t i = 0; i < ByteCounter; i += 4)

{

*TxAuxAddress = (((uint32_t)TxData[i + 3U] << 24U) |

((uint32_t)TxData[i + 2U] << 16U) |

((uint32_t)TxData[i + 1U] << 8U) |

(uint32_t)TxData[i]);

TxAuxAddress++;

}

/* Ativa requisição de transmissão do elem. Index no TxFIFO/Queue */

FDCAN2->TXBAR = ((uint32_t)1 << PutIndex);

}

}

}

```

A função Code2ByteCounter é uma função auxiliar que converte um código numérico, que especifica o tamanho do *payload*, para o número real de *bytes* de dados. Por exemplo, código 0 retorna 8 *bytes* (2 palavras de 4 *bytes*), código 7 retorna 64 *bytes* (16 palavras de 4 *bytes*).

A função FDCAN2 \_AddMessageToTxFifoQ tem como objetivo preparar e agendar uma mensagem CAN para transmissão usando a *Tx FIFO/Queue* do FDCAN2. Ela verifica se a fila de transmissão está habilitada e não está cheia. Se houver espaço, a função calcula o próximo índice disponível na fila. Em seguida, ela monta as duas palavras de cabeçalho da mensagem CAN (que incluem o ID da mensagem, padrão do ID (11 *bits*), tipo de quadro (Clássico), e comprimento dos dados (8 *bits*)), e as escreve na SRAM CAN no local correto da fila. Após isso, os dados da mensagem (lidos de um *array*/vetor TxData global) são copiados para a mesma área de memória. Finalmente, a função solicita a transmissão da mensagem recém-adicionada ao FDCAN2, ativando o *bit* correspondente ao índice da mensagem no registrador TXBAR, o que permite que o *hardware* inicie o processo de envio.

Note que no *header* de transmissão temos definido o ID da transmissão. Cada mensagem CAN tem um identificador, geralmente associado ao nó que a enviou. Assim cada nó que recebe a mensagem sabe sua origem.

6. Agora, vamos implementar a função FDCAN2 \_GetMessageFromRxFifo0 para recepção de mensagens, que também será adicionada ao escopo /\* USER CODE BEGIN 4 \*/

```

void FDCAN2_GetMessageFromRxFifo0 (void) {

uint32_t GetIndex = 0;

uint32_t *RxAddress;

uint32_t ByteCounter;

//Bytes a serem lidos

ByteCounter = Code2ByteCounter

((FDCAN2->RXESC & FDCAN_RXESC_F1DS) >> FDCAN_RXESC_F1DS_Pos);

}

```

```

if ((FDCAN2->RXF0C & FDCAN_RXF0C_F0S) && (FDCAN2->RXF0S &

FDCAN_RXF0S_F0FL)) {

//Le mensagens quando FIFO 0 cheia

if (((FDCAN2->RXF0S & FDCAN_RXF0S_F0F) >> FDCAN_RXF0S_F0F_Pos) == 1U)

{

/* Calcula o indice do elemento no Rx FIFO 0 */

GetIndex += ((FDCAN2->RXF0S & FDCAN_RXF0S_F0GI) >>

FDCAN_RXF0S_F0GI_Pos);

/* Obtem o tamanho de dados de RX FIFO0 na unidade de 32 bits */

uint8_t data_size = ByteCounter/4;

/* Calcula o endereco efetivo da mensagem

* Cada elemento de RXFIFO0:

* dados (data_size) + header (2 palavras de 32 bits) */

RxAddress = (uint32_t *) (SRAMCAN_BASE+(1U)*4 +

(GetIndex * (2U + data_size) * 4U));

}

/* Incrementa RxAddress para acessar a seq. palavra do cabecalho */

RxAddress++;

/* Incrementa RxAddress para acessar os campos de dados */

RxAddress++;

/* Retrieve Rx payload */

for (uint8_t i = 0; i < ByteCounter; i++)

{

RxData[i] = ((uint8_t *) RxAddress)[i];

}

// Acknowledge a recepcao, incrementando Get_idx

FDCAN2->RXFOA = GetIndex;

}

}

```

Para acessar um quadro na fila RX FIFO0, utilizamos o índice GetIndex, que é atualizado automaticamente pelo *hardware* a cada acesso. O tamanho de cada quadro, expresso em unidades de 32 bits, é determinado pelo *payload* configurado em FDCAN\_RXESC\_F1DS, acrescido de duas palavras de 32 bits referentes ao cabeçalho de uma mensagem.

7. Estando implementadas as funções básicas de inicialização, transmissão e recepção de mensagens do protocolo CAN, voltamos à função `main` para implementar a tarefa do projeto. Adicione no escopo `/* USER CODE BEGIN 2 */`

```

FDCAN2_Init();

```

e no escopo `/* USER CODE BEGIN 3 */`

```

for (int i=0; i<8; i++) {

TxData[i] = idx++;

}

FDCAN2_AddMessageToTxFifoQ (0x11);

HAL_Delay (1000);

```

A tarefa implementada configura o periférico FDCAN2 no microcontrolador STM32H7A para operar em modo *loopback*, e então, a cada segundo (1000 mili-seg), ele gera uma nova mensagem CAN com um ID fixo (0x11) e um *payload* de dados sequencialmente crescente (no primeiro quadro, os valores dos *bytes* vão de 0 a 7; no segundo quadro, de 8 a 15, e assim em diante.), adicionando-a à fila de transmissão. Dada a configuração em modo *loopback*, essas mensagens transmitidas serão imediatamente recebidas de volta pelo próprio FDCAN2,

permitindo testar a funcionalidade de transmissão e recepção sem a necessidade de um barramento CAN externo.

Essa estrutura é um excelente ponto de partida para testar e depurar a sua configuração do FDCAN2, especialmente no modo *loopback*.

8. Falta ainda implementar a rotina de serviço FDCAN2\_IT0\_IRQHandler para tratar o evento RF0NE que corresponde ao evento de recepção de uma nova mensagem na Rx FIFO 0. A interrupção deste evento foi habilitada em FDCAN2\_Init. Abra o arquivo `stm32h7xx_it.c` e insira no escopo `/* USER CODE BEGIN PFP */`

```

void FDCAN2_GetMessageFromRxFifo0 (void);

e em /* USER CODE BEGIN 1 */

void FDCAN2_IT0_IRQHandler(void)

{

if (FDCAN2->IR & FDCAN_IR_RF0N) { // Recepcao de nova mensagem

FDCAN2_GetMessageFromRxFifo0 ();

FDCAN2->IR |= FDCAN_IR_RF0N_Msk;

}

}

```

Quando o FDCAN2 recebe uma nova mensagem na *Rx FIFO 0*, ele gera uma interrupção, e esta função FDCAN2\_IT0\_IRQHandler é executada, se a interrupção FDCAN2\_IE\_RF0NE e a linha FDCAN2\_IT0\_IRQHandler estiverem habilitadas. Dentro da ISR, o código verifica se a *flag* RF0N (Recepção de Nova Mensagem na FIFO 0) está ativa no registrador de interrupções (FDCA2\_IR). Se estiver, isso indica que uma mensagem foi de fato recebida, e a função FDCAN2\_GetMessageFromRxFifo0() é então chamada para processar e ler essa mensagem. Após o processamento, a *flag* RF0N é limpa (FDCAN2->IR |= FDCAN\_IR\_RF0N\_Msk;), indicando que a interrupção foi tratada e preparando o sistema para futuras novas mensagens.

9. Realize o *build* e transfira o código executável para o STM32H7A no modo *debug*. Quando o programa estiver carregado, vá à aba de *Live Expressions* e adicione as expressões “TxData” e RxData”. Depois inicie a execução. Veja os valores de TxData sendo atualizados a cada segundo, e os valores de RxData atualizados de acordo.

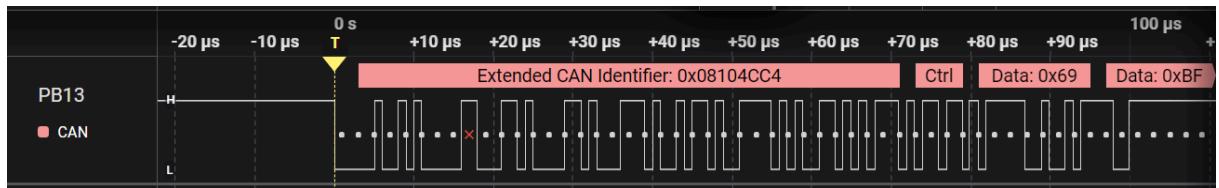

11. Conecte o canal 0 do analisador lógico ao pino PB13. Isto pode ser feito no pino 3 do *header* H7 (CAN2) ou no pino 5 de CN7 da placa NUCLEO. Lembre-se de conectar o GND do analisador a um GND da placa (pino 5 do *header* H7 ou um dos GND disponíveis nos conectores CN7 a CN10). Ajuste a aquisição para iniciar na borda de descida do canal e faça uma aquisição de 1ms.

| CN7  |      |       |      |       |

|------|------|-------|------|-------|

| PC6  | D16  | 1 2   | D15  | PB8   |

| PB15 | D17  | 3 4   | D14  | PB9   |

| PB13 | D18  | 5 6   | AVDD | VREFP |

| PB12 | D19  | 7 8   | GND  | GND   |

| PA15 | D20  | 9 10  | D13  | PA5   |

| PC7  | D21  | 11 12 | D12  | PA6   |

| PB5  | D22  | 13 14 | D11  | PA7   |

| PB3  | D23  | 15 16 | D10  | PD14  |

| PA4  | D24  | 17 18 | D9   | PD15  |

| PB4  | D25  | 19 20 | D8   | PG9   |

| VDDA | AVDD | 1 2   | D7   | PG12  |

| AGND | AGND | 3 4   | D6   | PA8   |

| GND  | GND  | 5 6   | D5   | PE11  |

| PC1  | A8   | 7 8   | D4   | PE14  |

| PC5  | A7   | 9 10  | D3   | PE13  |

Ative o modo CAN do analisador (abra mais opções clicando no sinal “+” no campo superior direito, ao lado de “Analyzer”). Configure-o com a *Bit Rate* em 500.000. Note os vários elementos do quadro no sinal capturado e compare com a [referência](#), lembrando que este quadro é de formato padrão.

11. Mude o valor do parâmetro de entrada 0x11 na função `FDCAN2_AddMessageToTx_fifoQ` (0x11) para qualquer valor que caiba em 11 bits, exceto o zero (1 a 2047). Execute o programa. O que acontece? As mensagens ainda são recebidas?

Note que todas as mensagens que forem colocadas no barramento irão gerar a interrupção de recepção. Um programa mais completo precisa verificar o ID da mensagem, através do valor do campo “ID” do cabeçalho para decidir o que vai fazer com ela.

12. As unidades de transmissão no protocolo CAN são os *quadros de mensagens* estruturado (*frames*), e eles são efetivamente construídos antes da transmissão, enviados quadro por quadro. Com base nesse entendimento, você consegue explicar a demanda por um espaço de memória SRAM CAN que deve ser configurado manualmente para complementar a operação do *hardware* de um periférico FDCAN?

13. Comparado aos protocolos RS-232, I2C e SPI, quais **informações adicionais** são inseridas no cabeçalho de uma mensagem CAN? Há alguma vantagem prática para esse *overhead* de dados? Não se preocupe se ainda não tiver a resposta; abordaremos isso mais adiante.

14. O que são os segmentos de tempo em *bits* configuráveis em uma rede CAN, e qual é o papel deles na sincronização entre os nós e na garantia da integridade dos dados? De que

maneira esses segmentos contribuem para esses objetivos? Caso você ainda não saiba a resposta, não se preocupe. Vamos explorar esse conceito adiante.

15. Imagine um cenário automotivo onde sensores de freio e o sistema de infoentretenimento precisam enviar dados simultaneamente pela mesma rede CAN. Sendo uma rede multi-mestre, na qual diversos dispositivos podem iniciar transmissões a qualquer instante, como o protocolo CAN decide qual mensagem “vence” o acesso ao barramento e será transmitida sem interrupções? Por quê uma simples configuração com *pull-ups* e *open-drain*, como no I2C, não seria suficiente para gerenciar essa arbitragem complexa? E qual o papel crucial dos identificadores de mensagem nesse processo?

## Projeto de comunicação CAN usando *loopback* e filtros

Você já parou para pensar em como as informações que você recebe na internet são filtradas? Muitas vezes, você se depara apenas com conteúdos que realmente interessam a você, como se houvesse um assistente pessoal organizando tudo. Mas como isso acontece? É fascinante saber que existem programas que analisam o conteúdo e enviam apenas o que se alinha aos seus interesses. Imagine se isso pudesse ser feito diretamente pelo *hardware*, bloqueando dados irrelevantes antes mesmo de chegarem ao seu processador! Essa otimização na comunicação não é apenas teórica. No nosso projeto anterior, discutimos como as mensagens CAN operam. Cada mensagem que passa pelo barramento aciona a interrupção de recepção do módulo, e é o *software* que decide se essa mensagem é relevante ou não. Em um ambiente onde muitas mensagens estão trafegando, essa tarefa pode sobrecarregar a CPU. É aqui que entram os **filtros de Identificador**. Esses filtros analisam as mensagens assim que chegam, e só geram interrupções se atenderem a critérios específicos. Isso não só alivia a carga de trabalho do processador, mas também torna a comunicação muito mais eficiente. Vamos explorar juntos como essas tecnologias podem ser aplicadas na prática e como vocês podem desenvolver soluções inovadoras para otimizar ainda mais a troca de informações!

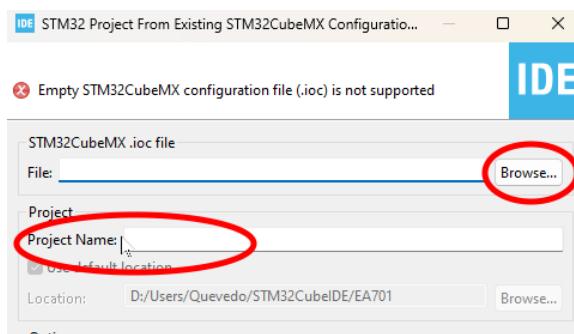

1. Crie um projeto “CAN\_Filtros”, **sem inicializar os periféricos**. Este projeto tem a mesma configuração do projeto anterior. Assim, para facilitar o trabalho, use a opção do menu *File – New – STM32 Project from an Existing STM32CubeMX Configuration File (.ioc)*. Na janela que se abre, clique no botão “Browse” e navegue em seu *workspace* até a pasta com o nome do projeto anterior (CAN\_Base). Nesta pasta, selecione o arquivo “CAN\_Base.ioc”. Voltando à janela anterior, note que o campo do nome do projeto foi preenchido com o nome do arquivo selecionado. Mude o nome do projeto para “CAN\_Filtros” e clique no botão “Finish”. Será criado um projeto com o nome novo selecionado, usando uma cópia do arquivo de configuração do outro projeto. Assim, o projeto já inicia configurado como o anterior.

2. Gere o código e sobrescreva os arquivos main.c e stm32h7xx\_it.c com os arquivos do projeto “CAN\_Base”. Boa parte do código do projeto anterior será aproveitada.

3. Abra main.c. Inclua as seguintes definições de macros no escopo /\* USER CODE BEGIN PD \*/

```

#define SFID1 0x11

#define SFID2 0x15

#define TIPO_FILTER 0b00 // 0b00: Intervalo; 0b10: Mascaramento

```

Inclua o seguinte bloco de códigos entre o bloco que contém a chamada de FDCAN2\_AlocaSRamCANSegmentos e o sétimo bloco da função FDCAN2\_Init.

```

{

// Configura filtros de Identificadores para armazenamento no RxFIFO0

uint32_t *FilterAddress;

uint32_t FilterElementW1;

FilterElementW1 = ((TIPO_FILTER << 30U) | //0b00; 0b01 (dual); 0b10 e 0b11 (desabilita)

(0b001 << 27U) | //FDCAN_FILTER_TO_RXFIFO0

(SFID1 << 16U) | // FilterID1

(SFID2)); // FilterID2

/* Calcule o endereço do filtro na RaM de mensagens */

FilterAddress = (uint32_t *) (SRAMCAN_BASE + (0 * 4U)); // offset = FilterIndex

/* Escreve elemento de filtro na SRAMCAN */

*FilterAddress = FilterElementW1;

/* Configura filtragem global */

FDCAN2->GFC = ((0b10 << FDCAN_GFC_ANFS_Pos) | // NonMatchingStd - Reject

(0b10 << FDCAN_GFC_ANFE_Pos) | // NonMatchingExt - Reject

(0b1 << FDCAN_GFC_RRFS_Pos) | // RejectRemoteStd

(0b1 << FDCAN_GFC_RRFE_Pos)); // RejectRemoteExt

}

```

4. Vamos agora estabelecer o código do *loop*. Para distinguir as mensagens, para um identificador iremos enviar as sequências de *bytes* para valores entre 0 e 127. Para o outro identificador, a sequência vai de 128 até 256. Após a linha /\* USER CODE BEGIN 3 \*/, escreva o código:

```

for (uint8_t i=0; i<8; i++) {

TxDATA[i] = idx++;

}

if (indx > 127) indx = 0;

FDCAN2_AddMessageToTxFifoQ (0x11);

HAL_Delay (1000);

for (uint8_t i=0; i<8; i++) {

TxDATA[i] += 128;

}

FDCAN2_AddMessageToTxFifoQ (0x14);

HAL_Delay (1000);

```

Agora enviamos alternadamente os dois conjuntos de mensagens com os IDs 0x11 e 0x14, ambos na faixa de passagem do filtro.

6. Realize o *build* e transfira o código executável para o microcontrolador no modo *debug*. Veja novamente as variáveis TxData e RxData na aba *Live Expressions*.

7. Vamos mudar a faixa do filtro. Mude o valor da macro SFID1 para 0x12. Como a faixa agora inicia em 0x12, as mensagens com *bytes* entre 0 e 127 (ID = 0x11) não irão gerar o evento RFONE, sendo totalmente ignoradas. Realize o *build* e transfira o código executável para o microcontrolador no modo *debug*. Execute o programa e veja o que acontece.

8. Vamos mudar o tipo de filtro, modificando a definição da macro TIPO\_FILTRO de 0b00 ([FDCAN\\_FILTER\\_RANGE](#)) para 0b10 ([FDCAN\\_FILTER\\_MASK](#)). Agora o elemento SFID1 contém o valor base do filtro e o elemento SFID2 contém a máscara. A partir do valor base, apenas os *bits* correspondentes aos *bits* em “1” na máscara serão comparados no filtro. Mude o elemento SFID1 para 0x11 e o elemento SFID2 para 0xFA. Ao combinar o valor base com a máscara, os IDs que irão passar pelo filtro são 0b00010x0x, ou seja, tanto 0x11 quanto 0x14 irão passar. Realize o *build*, transfira o executável para o microcontrolador no modo *debug* e veja o resultado.

9. Mude apenas o elemento SFID2 para 0xFB. Agora os IDs que passam são 0b00010x01. Apenas as mensagens com ID 0x11 irão passar. Compile e execute novamente o programa e confirme esta afirmação.

10. Com base no que você já explorou, em que nível operam os filtros de mensagens? No nível do *hardware* ou de *software* do controlador CAN? Eles realmente impedem a recepção física das mensagens no barramento, ou apenas evitam que essas mensagens, uma vez recebidas, cheguem ao processador? Se você ainda não tem a resposta, não se preocupe: isso será abordado em detalhes no material que você está prestes a ler.

11. O código apresentado no item 3 ilustra a configuração básica da filtragem de mensagens pelo periférico FDCAN. Você consegue identificar a função primária de cada linha de instrução? Se teve dificuldades para decifrá-las, não se preocupe. Voltaremos a essa configuração em detalhes mais adiante.

12. Em um sistema crítico com alta taxa de mensagens, como um barramento automotivo que conecta dezenas de módulos (controle de motor, freios, *airbags*, sistema multimídia, sensores de estacionamento, entre outros), por que a correta configuração dos filtros de *hardware* do protocolo CAN é decisiva para garantir o funcionamento seguro e eficiente do sistema? Ao filtrar mensagens, os filtros reduzem a sobrecarga no barramento, no processador, ou em ambos? Se você ainda não tiver essa resposta, não se preocupe. Vamos explorar em breve essa característica específica do protocolo CAN, que não está presente nos protocolos que vimos anteriormente.

## Projeto de comunicação CAN usando 4 nós

Imagine a possibilidade de criar uma rede de controle que conecta dispositivos de forma ágil e eficiente, utilizando apenas um par de fios trançados. Com o entendimento do protocolo CAN bem estabelecido, você pode visualizar como podemos transmitir tanto sinais de dados quanto comandos de controle, integrando a serialização dos sinais e um sinal de *clock* para a recuperação desses dados no receptor. Neste projeto, vamos explorar a implementação de uma rede de controle CAN composta por múltiplos nós, onde cada bancada funcionará como um nó, enviando e recebendo mensagens que acionam dispositivos físicos e respondem a eventos em tempo real. Essa configuração não só demonstra a eficácia da comunicação entre sensores e atuadores, mas também proporciona uma experiência prática de colaboração. Sugerimos que **quatro duplas** colaborem, com cada grupo contribuindo como um nó de uma rede interconectada. Dessa forma, **cada fileira de quatro bancadas implementará sua própria rede**, proporcionando uma oportunidade única de transformar teoria em prática. Este projeto não apenas estimula a aplicação dos conceitos aprendidos, mas também incentiva a criatividade no *design* de sistemas de controle, permitindo que vocês desenvolvam soluções em um ambiente colaborativo.

Cada nó irá ler um valor de 16 *bits* em um canal do ADC, no qual estará ligado um potenciômetro ou um eixo do *joystick* a uma taxa de 5 leituras por segundo. O valor lido será guardado em uma variável e transmitido pelo barramento CAN com um identificador próprio. Para o valor de 16 *bits* do ADC, serão usados os dois primeiros *bytes*, com o *byte* mais significativo primeiro. Cada nó irá também receber as mensagens dos demais nós com suas leituras dos seus ADCs e guardar os valores em variáveis. A cada meio segundo, o *display* Nokia do nó será atualizado, apresentando em cada linha o valor atual recebido de cada nó, além do valor adquirido de seu próprio ADC.

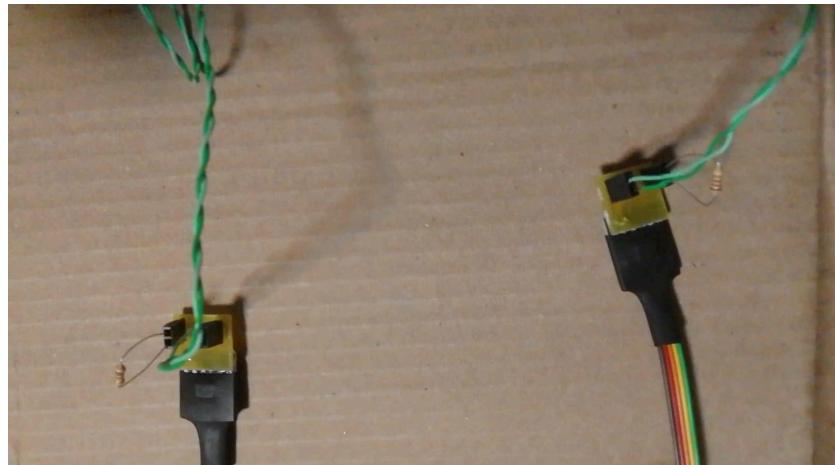

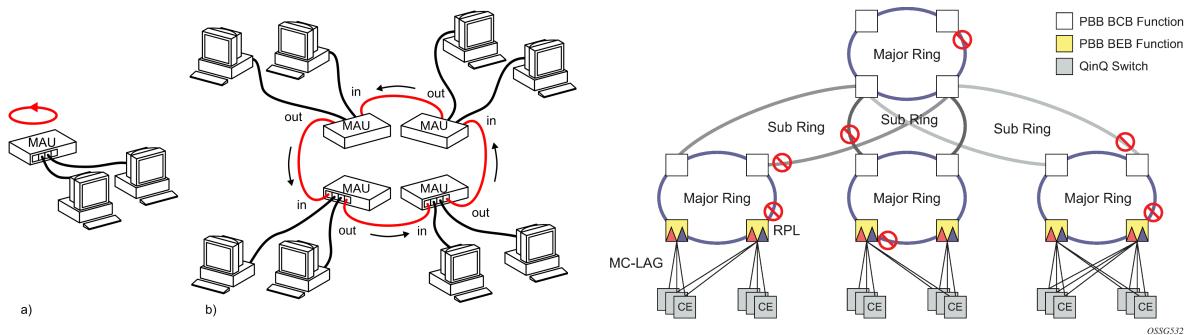

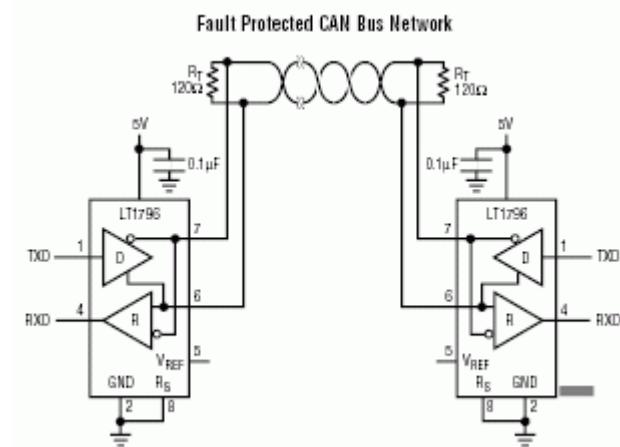

Para que a rede seja implementada corretamente, será necessário implementar a **camada física** da mesma. Esta camada é implementada com o auxílio de **transcievers** [MCP2551](#), que são circuitos que convertem os sinais de transmissão de um controlador CAN (que faz parte do microcontrolador) em níveis lógicos padrão do microcontrolador para sinais **diferenciais** entre duas saídas, ligadas ao par trançado de fios (**CANH** e **CANL**). Os *transcievers* ainda convertem os sinais presentes no par trançado do barramento em níveis lógicos padrão para recepção de um controlador CAN.

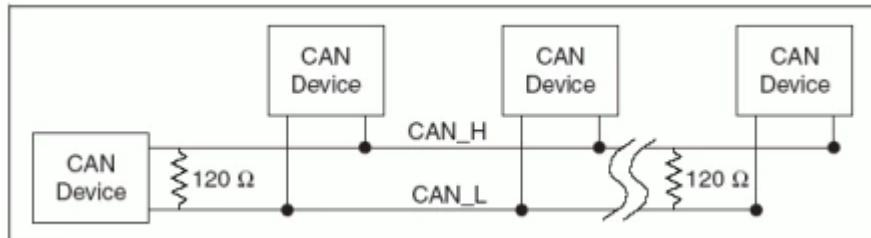

Note que como os *bits* são definidos pela **diferença entre** os pinos CANH e CANL, não importa o potencial entre cada um destes pinos e o GND. Assim, **não é necessário** conectar os GNDs de nós distintos. Porém, como o par trançado se comporta como uma linha de transmissão, é importante que em suas extremidades haja um resistor (entre CANH e CANL) com o mesmo valor da impedância característica do par trançado, no caso  $120\Omega$ , para garantir uma comunicação clara e eficaz entre os nós da rede. Sem terminações adequadas, os sinais enviados podem **refletir** nas extremidades do cabo, gerando distorções, falhas na comunicação e comprometendo a integridade das mensagens.

1. Os alunos deverão retirar no almoxarifado, para cada fileira de bancadas, 4 *transcievers*, 3 trechos de par trançado de fios, e 2 resistores de  $120\Omega$ . Os *transcievers* possuem cabos multi-vias com um conector na ponta, que deve ser ligado no [conector H7 \(CAN2\) da placa de expansão](#). Este conector disponibiliza os sinais de Tx e Rx do controlador CAN, bem como a alimentação de 5V para o *transceiver*.

2. Na placa de cada *transceiver*, foi adaptado um par de *headers* de 2 pinos, sendo cada *header* ligado aos sinais de CANH e CANL do *transceiver*. Para localizar cada nó da rede, vamos usar um número entre 0 e 3. O nó 0 é o mais à esquerda na fileira de bancadas (parede), sendo que o nó 1 é o imediatamente a seu lado e assim em diante. Em um *header* do adaptador no nó 0, introduza os terminais de um resistor de  $120\Omega$ . No outro *header*, introduza as pontas desencapadas de uma das extremidades de um dos trechos de par trançado. Note bem qual fio fica mais perto da placa do *transceiver* (CANL) e qual fica mais perto da borda da placa adaptadora (CANH). Em um *header* do nó 1, introduza as pontas desencapadas da outra extremidade do mesmo trecho de par trançado, mantendo a mesma posição usada no nó 0. No outro *header*, introduza as pontas de uma extremidade de outro par trançado, sendo que a outra extremidade deste par deve ser ligada a um dos *headers* do nó 2, **mantendo a polaridade**. Da mesma forma, o último trecho de par trançado deve ser ligado entre um *header* do nó 2 e um *header* do nó 3, sendo que neste último o *header* sobrante deve ter o outro resistor de  $120\Omega$  conectado. A figura a seguir ilustra a configuração de uma rede com dois nós. Em ambas as placas, os resistores de terminação estão conectados a um *header*, enquanto uma extremidade do par trançado se liga ao *header* do outro nó.

Além das ligações do *transciever*, é necessário ligar um potenciômetro ou um canal do *joystick*. Conecte os extremos do potenciômetro ou os pinos “GND” e “+5V” do *joystick* nos pinos 2 (+3.3V) e 7 (GND) do conector H9 (ADC). O terminal central do potenciômetro ou um dos canais do *joystick* (Vx ou Vy) deve ser ligado ao pino 3 do mesmo conector (PC4). As ligações são as mesmas feitas no roteiro de DAC e ADC.

3. Vamos agora implementar a programação do controlador CAN e da CPU. Devido à sua **complexidade relativa maior que projetos anteriores, o projeto todo foi implementado**

com a interface HAL e disponibilizado no arquivo [CAN\\_Network.zip](#) para importação no STM32CubeIDE. Importe o projeto em todos os computadores da fileira de bancadas. Nos próximos itens, vamos explorar os detalhes de configuração do microcontrolador e do funcionamento do código.

Se optarmos por uma implementação via CMSIS como nos dois projetos anteriores, podemos criar um projeto “CAN\_Network\_CMSIS” a partir do arquivo CAN\_Base.ioc ou CAN\_Filtros.ioc, **sem inicializar os periféricos**. Use a opção do menu *File – New – STM32 Project from an Existing STM32CubeMX Configuration File (.ioc)*. O código completo dessa versão do projeto está no arquivo [CAN\\_Network\\_CMSIS.zip](#).

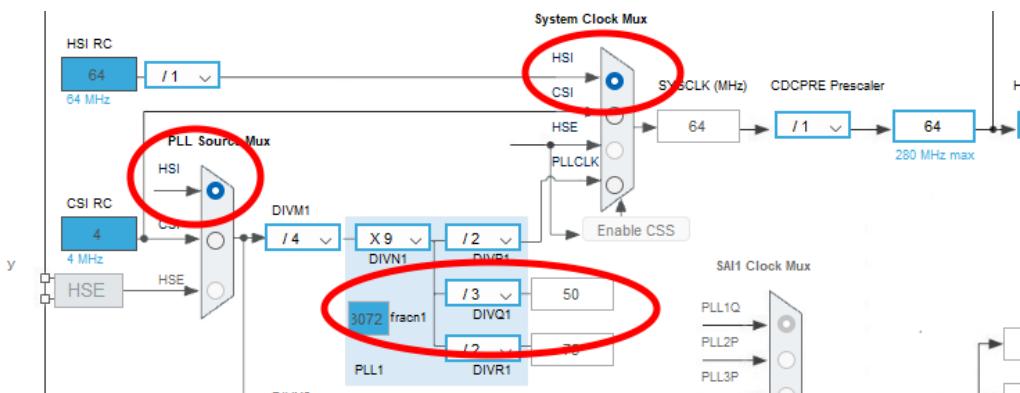

4. Inicialmente, abra o arquivo “CAN\_Network.ioc” para ver a configuração do *CubeMX* em modo gráfico. Aqui vários periféricos foram configurados. O *clock* foi configurado como nos projetos anteriores deste roteiro, porém foi adicionada a configuração para o PLL2, para que este sirva de *clock* para o ADC1. O valor de PLL2P foi definido para 43MHz, pois o valor máximo deste *clock* é abaixo dos 50MHz usados no FDCAN. Assim, não podemos usar a mesma fonte de *clock* para ambos.

A configuração da fonte de *clock* PPL2 para o periférico ADC1 é similar à que fizemos para o FDCAN2, especificamente antes de habilitar os sinais de *clock*. As seguintes instruções podem ser inseridas na inicialização do ADC1, antes do *clock gating*.

{

```

//Configurar a frequência de PLL2 em 43MHz

// Desabilita PLL2

RCC->CR &= ~RCC_CR_PLL2ON;

while (RCC->CR & RCC_CR_PLL2RDY); // Aguarda a desabilitação

// Configura fonte (mantém a existente) e DIVM2

RCC->PLLCKSELR &= ~RCC_PLLCKSELR_DIVM2;

```

```

RCC->PLLCKSELR |= (32U << RCC_PLLCKSELR_DIVM2_Pos) ;

// Configura os divisores e multiplicadores de PLL2

RCC->PLL2DIVR =

((129U - 1U) << RCC_PLL2DIVR_N2_Pos) | // DIVN2

((6U - 1U) << RCC_PLL2DIVR_P2_Pos) | // DIVP2 → Saída P

((2U - 1U) << RCC_PLL2DIVR_Q2_Pos) | // DIVQ2 → Se quiser

Q

((2U - 1U) << RCC_PLL2DIVR_R2_Pos); // DIVR2 → Se quiser

R

// Configura o fator fracionário (não utilizado → zero)

RCC->PLL2FRACR = (0U << RCC_PLL2FRACR_FRACN2_Pos) ;

// Configura faixa de entrada e faixa de VCO

// RGE: Faixa de frequência de entrada → Selecionar adequada

// Suponha faixa 8-16 MHz → RCC_PLLCFG_R_PLL2RGE_1 (consultar manual)

RCC->PLLCFG_R &= ~RCC_PLLCFG_R_PLL2RGE;

RCC->PLLCFG_R |= RCC_PLLCFG_R_PLL2RGE_1; // Faixa 8-16 MHz (exemplo)

// VCO: Faixa de frequência do VCO

// 0 = Medium VCO (150-420 MHz)

// 1 = Wide VCO (192-836 MHz)

RCC->PLLCFG_R &= ~RCC_PLLCFG_R_PLL2VCOSEL; // Medium VCO

// Habilita os divisores desejados (PLL2P no caso)

RCC->PLLCFG_R |= RCC_PLLCFG_R_DIVP2EN;

RCC->PLLCFG_R &= ~(RCC_PLLCFG_R_DIVQ2EN | RCC_PLLCFG_R_DIVR2EN); //

Desabilita Q e R se não usados

// Desabilita o modo fracionário (não usado)

RCC->PLLCFG_R &= ~RCC_PLLCFG_R_PLL2FRACEN;

// Habilita PLL2

RCC->CR |= RCC_CR_PLL2ON;

while (!(RCC->CR & RCC_CR_PLL2RDY)); // Aguarda PLL2 pronto

}

{

// Ativar clock gating de ADC e perifericos associados

// Seleciona ker_ck para FDCAN (pll1_q_ck)

RCC->PLLCFG_R |= RCC_PLLCFG_R_DIVQ2EN_Msk; // habilita pll2_q_ck

RCC->SRDCCIPR &= ~RCC_SRDCCIPR_ADCSEL_Msk; // seleciona a fonte para

ADC

// Habilitar o clock do ADC1

RCC->AHB1ENR |= RCC_AHB1ENR_ADC12EN;

// Configurar PC4 como analog

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOCEN;

GPIOC->MODER |= GPIO_MODE4;

NVIC_SetPriority(ADC_IRQn, 2); // Configura NVIC para interrupcoes do

ADC, prioridade 2

NVIC_EnableIRQ(ADC_IRQn);

}

```

5. O FDCAN2 foi configurado de maneira semelhante aos projetos anteriores, mas com algumas adaptações importantes. Primeiramente, o parâmetro “Auto Retransmission” foi alterado para “Enable”, permitindo que o controlador tente reenviar mensagens em caso de

colisão de barramento, dado que estamos lidando com quatro nós transmitindo informações simultaneamente. Além disso, o *loopback* foi desabilitado.

```

// Defina o modo de operacao (Loopback externo)

FDCAN2->CCCR &= ~(FDCAN_CCCR_TEST |

FDCAN_CCCR_MON |

FDCAN_CCCR_ASM);

FDCAN2->TEST &= ~FDCAN_TEST_LBCK;

// Operacao normal (alterado)

// FDCAN2->CCCR |= FDCAN_CCCR_TEST;

// FDCAN2->TEST |= FDCAN_TEST_LBCK;

```

| Basic Parameters        |              |

|-------------------------|--------------|

| Frame Format            | Classic mode |

| Mode                    | Normal mode  |

| Auto Retransmission     | Enable       |

| Transmit Pause          | Disable      |

| Protocol Exception      | Disable      |

| Nominal Sync Jump Width | 13           |

| Data Prescaler          | 25           |

| Data Sync Jump Width    | 1            |

| Data Time Seg1          | 2            |

| Data Time Seg2          | 1            |

| Message Ram Offset      | 0            |

| Std Filters Nbr         | 1            |

| Ext Filters Nbr         | 0            |

Em segundo lugar, o parâmetro “Rx Fifo0 Elmts Nbr” foi aumentado de 1 para 4, possibilitando o armazenamento de até quatro mensagens na FIFO0 de recepção.

|                         |                    |

|-------------------------|--------------------|

| Rx Fifo0 Elmts Nbr      | 4                  |

| Rx Fifo0 Elmt Size      | 8 bytes data field |

| Rx Fifo1 Elmts Nbr      | 0                  |

| Rx Fifo1 Elmt Size      | 8 bytes data field |

| Rx Buffers Nbr          | 0                  |

| Rx Buffer Size          | 8 bytes data field |

| Tx Events Nbr           | 0                  |

| Tx Buffers Nbr          | 0                  |

| Tx Fifo Queue Elmts Nbr | 1                  |

| Tx Fifo Queue Mode      | FIFO mode          |

| Tx Elmt Size            | 8 bytes data field |

Modificamos FDCAN2\_AlocaSRamCANSegmentos para incluir 4 elementos em vez de 1, visando atender a este quesito. A alteração está detalhada no trecho de código.

```

//MODIFY_REG(FDCAN2->RXF0C, FDCAN_RXF0C_F0S, (1U << FDCAN_RXF0C_F0S_Pos));

MODIFY_REG(FDCAN2->RXF0C, FDCAN_RXF0C_F0S, (4U << FDCAN_RXF0C_F0S_Pos));

/* Endereco inicial de Tx buffer (alterado) */

//Origem += (4U); // Avanca 4 palavras (tamanho fixo de 1 elemento RX

FIFO0)

```

```

Origem += (4U * 4U); // Avança 16 palavras (tamanho fixo de 4 elementos RX

FIFO0)

MODIFY_REG(FDCAN2->TXBC, FDCAN_TXBC_TBSA, (Origem << FDCAN_TXBC_TBSA_Pos));

```

Essa alteração implica ainda que os acessos de escrita na fila TX FIFO precisam ser deslocados para acomodar os 4 quadros de mensagens na fila RX FIFO0. Em FDCAN2\_AddMessageToTxFifoQ, foi feita a seguinte substituição

```

/* Calcula o endereço do buffer TxFIFO/Queue */

//RxFIFO passou de 1 elemento para 4 elementos (alterado)

//TxAddress = (uint32_t *) (SRAMCAN_BASE + (1U+4U)*4U +

//((PutIndex*((FDCAN2->TXBC & FDCAN_TXBC_TFQS) >> FDCAN_TXBC_TFQS_Pos)*4U));

TxAddress = (uint32_t *) (SRAMCAN_BASE + (1U+4U*4U)*4U +

(PutIndex*((FDCAN2->TXBC & FDCAN_TXBC_TFQS) >> FDCAN_TXBC_TFQS_Pos)*4U));

```

Os demais parâmetros permanecem inalterados, incluindo a interrupção do FDCAN2, que continua habilitada com prioridade 1.

Em terceiro lugar, a distinção das mensagens geradas pelos 4 nós é essencial. Nos dois projetos-exemplo anteriores, a configuração *loopback* implicava que o canal TX estava conectado internamente ao canal RX. Isso resultava no empilhamento exclusivo de quadros de mensagem com o mesmo identificador (ID) na fila RX FIFO0. No entanto, neste projeto, ao estar aberto para receber mensagens de uma rede com 4 nós, permite que a fila RX FIFO0 de cada nó empilhe mensagens com IDs variados. Para processar essas mensagens distintamente, é necessário extraír o ID do campo de cabeçalho de cada mensagem. Isso levou a uma modificação mais radical nos códigos:

1. Para garantir o correto armazenamento dos dados enviados pelos 4 nós, a ISR FDCAN2\_IT0\_IRQHandler precisa recuperar o ID e o *payload* de cada nova mensagem recebida. Dessa forma, o processador pode alocar os dados recuperados na posição apropriada do vetor *valor*, que dedica uma posição distinta para cada nó. Assim, foi feita a seguinte alteração em FDCAN2\_IT0\_IRQHandler

```

//Armazenar o payload na posição correspondente do valor (alterado)

//FDCAN2_GetMessageFromRxFifo0 ();

msg_id = FDCAN2_GetMessageFromRxFifo0 ();

PutValueInVector(msg_id);

```

A definição da função PutValueInVector é adicionada no escopo `/* USER CODE BEGIN 0 */` do arquivo main.c

```

void PutValueInVector (uint32_t msg_ID) {

uint8_t p;

p = ((uint8_t)msg_ID) & 0x03;

valor[p] = (RxData[0] * 256) + RxData[1];

}

```

2. Para recuperar o ID da mensagem recebida, a função FDCAN2\_GetMessageFromRxFifo0 necessita de uma atualização. Visando minimizar o impacto no restante do código, decidimos que o ID seja retornado por

essa função é, em seguida, passado para PutValueInVector. É em PutValueInVector que o *payload*, já extraído para RxData, é armazenado na posição do vetor valor que corresponde ao ID.

```

//Retorna o ID da mensagem (alterado)

//void FDCAN2_GetMessageFromRxFifo0 (void) {

uint32_t FDCAN2_GetMessageFromRxFifo0 (void) {

uint32_t GetIndex = 0;

uint32_t *RxAddress;

uint32_t ByteCounter;

uint32_t IdType, Identifier = 0;

//Obter o indice (posicao) da mensagem na RX FIFO

//e correspondente endereço na SRAM CAN (alterado)

//    if ((FDCAN2->RXF0C & FDCAN_RXF0C_F0S) & (FDCAN2->RXF0S &

FDCAN_RXF0S_F0FL)) {

//          //Le mensagens quando FIFO 0 cheia

//          if (((FDCAN2->RXF0S & FDCAN_RXF0S_F0F) >>

FDCAN_RXF0S_F0F_Pos) == 1U)

//          {

//          /* Calcula o indice do elemento no Rx FIFO 0 */

//          GetIndex += ((FDCAN2->RXF0S & FDCAN_RXF0S_F0GI) >>

FDCAN_RXF0S_F0GI_Pos);

//

//          /* Calcula o endereço efetivo da mensagem */

//          RxAddress = (uint32_t *) (SRAMCAN_BASE+(1U)*4 +

//                                      (GetIndex * ((FDCAN2->RXF0C &

FDCAN_RXF0C_F0S) >> FDCAN_RXF0C_F0S_Pos) * 4U));

//

//      }

//  }

/* Rx FIFO 0 está vazio */

if ((FDCAN2->RXF0S & FDCAN_RXF0S_F0FL) == 0U)

{

/* RX FIFO está vazio */

return 0;

}

else

{

//Bytes a serem lidos

ByteCounter = Code2ByteCounter

((FDCAN2->RXESC & FDCAN_RXESC_F1DS) >> FDCAN_RXESC_F1DS_Pos);

/* Verifica se Rx FIFO 0 está cheio e se o modo de sobreescreve

esta ativado */

if (((FDCAN2->RXF0S & FDCAN_RXF0S_F0F) >> FDCAN_RXF0S_F0F_Pos) ==

1U)

{

if (((FDCAN2->RXF0C & FDCAN_RXF0C_F0OM) >>

FDCAN_RXF0C_F0OM_Pos) == ((uint32_t)0x00000001U))

{

/* When overwrite status is on discard first message in FIFO */

GetIndex = 1U;

}

}

}

}

```

```

}

}

/* Calcula o indice do elemento no Rx FIFO 0 */

GetIndex += ((FDCAN2->RXF0S & FDCAN_RXF0S_F0GI) >>

FDCAN_RXF0S_F0GI_Pos);

/* Obtem o tamanho de dados de RX FIFO0 na unidade de 32 bits */

uint8_t data_size = ByteCounter/4;

/* Calcula o endereco efetivo da mensagem

* Cada elemento de RXFIFO0:

* dados (data_size) + header (2 palavras de 32 bits) */

RxAddress = (uint32_t *) (SRAMCAN_BASE+(1U)*4 +

(GetIndex * (2U + data_size) * 4U));

}

{

/* Recuperar o identificador (alterado) */

IdType = *RxAddress & ((uint32_t)0x40000000U);

/* Recuperar o identificador */

if (IdType == ((uint32_t)0x00000000U)) /* Standard ID element */

{

Identifier = ((*RxAddress & ((uint32_t)0x1FFC0000U)) >> 18U);

}

else /* Extended ID element */

{

Identifier = (*RxAddress & ((uint32_t)0x1FFFFFFFU));

}

}

/* Incrementa RxAddress para acessar a segunda palavra do cabecalho */

*/

RxAddress++;

/* Incrementa RxAddress para acessar os campos de dados */

RxAddress++;

/* Retrieve Rx payload */

for (uint8_t i = 0; i < ByteCounter; i++)

{

RxData[i] = ((uint8_t *)RxAddress)[i];

}

// Acknowledge a recepcao, incrementando Get_idx

FDCAN2->RXFOA = GetIndex;

return Identifier;

}

```

6. O ADC foi configurado usando o *CubeMX*, ativando o pino PC4 como o canal 4, e parâmetros no padrão inicial, exceto pelo “*Oversampling Ratio*” igual a 32, o “*Oversampling Right Shift*” igual a “*5 bit shift*” e o “*Sampling Time*” igual a 32.5 ciclos. O tempo de amostragem é alongado para que a carga do capacitor de *sample and hold* possa acontecer integralmente mesmo com uma fonte de resistência relativamente alta. O *oversampling* permite usar um *trigger* para amostrar o mesmo canal várias vezes em sequência e somar os resultados das conversões, sendo que ao final a soma sofre um deslocamento para a direita. No caso, somamos 32 conversões e deslocamos 5 *bits*, dividindo a soma por 32. Assim,

realizamos uma média de conversões, reduzindo o ruído elétrico na entrada do ADC. Por fim, o parâmetro “*External Trigger Conversion Source*” foi mudado para “*Timer 6 Trigger Event*”, para disparar o ADC na atualização do TIM6. A interrupção de ADC foi habilitada com

|                                 |                                                    |

|---------------------------------|----------------------------------------------------|

| Mode                            | Independent mode                                   |

| ADC_Settings                    |                                                    |

| Clock Prescaler                 | Asynchronous clock mode divided by 1               |

| Resolution                      | ADC 16-bit resolution                              |

| Scan Conversion Mode            | Disabled                                           |

| Continuous Conversion Mode      | Disabled                                           |

| Discontinuous Conversion Mode   | Disabled                                           |

| End Of Conversion Selection     | End of single conversion                           |

| Overrun behaviour               | Overrun data preserved                             |

| Left Bit Shift                  | No bit shift                                       |

| Conversion Data Management Mode | Regular Conversion data stored in DR register only |

| Low Power Auto Wait             | Disabled                                           |

prioridade 2.

A configuração direta das funções do periférico ADC1 via registradores segue o mesmo procedimento que temos utilizado.

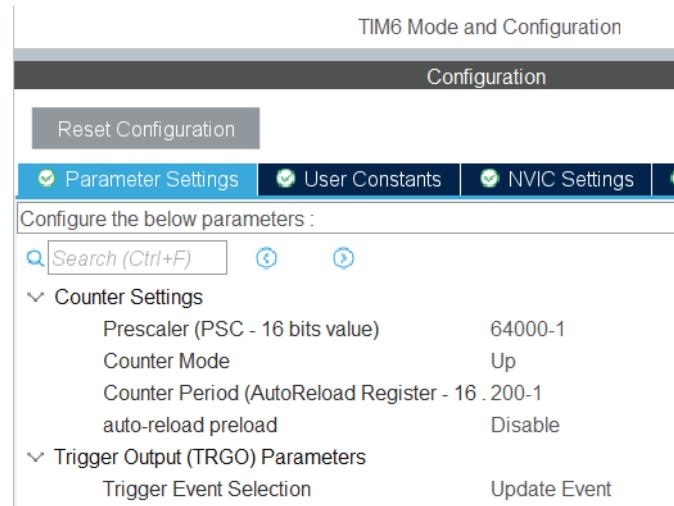

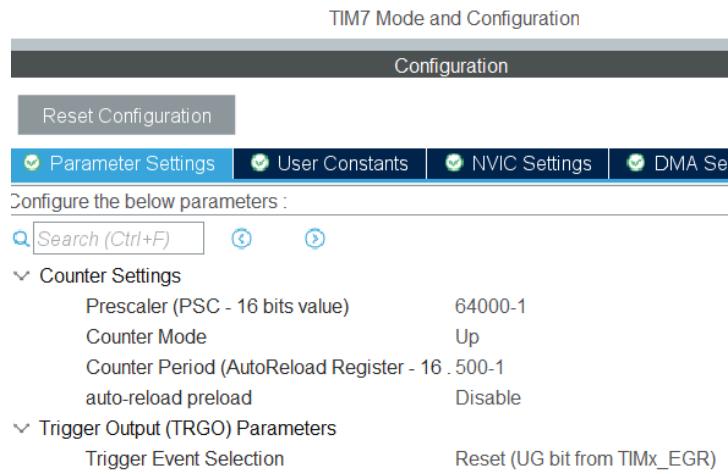

7. O TIM6 foi ajustado com *prescaler* de 64000 e *AutoReload* em 200, gerando assim uma frequência de repetição de *updates* de 5Hz. O parâmetro *Trigger Event Selection* foi modificado para *Update Event*. Assim, o ADC é disparado 5 vezes por segundo via eventos de interconexões internas dos módulos. Não é habilitada a interrupção de *timer*. A esta altura, já dominamos essa configuração utilizando a interface CMSIS.

|                                    |                                                |

|------------------------------------|------------------------------------------------|

| ADC-Regular_ConversionMode         |                                                |

| Enable Regular Conversions         | Enable                                         |

| Enable Regular Oversampling        | Enable                                         |

| Oversampling Right Shift           | 5 bit shift for oversampling                   |

| Oversampling Ratio                 | 32                                             |

| Regular Oversampling Mode          | Oversampling Continued Mode                    |

| Triggered Regular Oversampling     | Single trigger for all oversampled conversions |

| Number Of Conversion               | 1                                              |

| External Trigger Conversion Source | Timer 6 Trigger Out event                      |

| External Trigger Conversion Edge   | Trigger detection on the rising edge           |

8. O TIM7 foi ajustado com *prescaler* de 64000 e *AutoReload* em 500, gerando assim uma frequência de repetição de 2Hz. A interrupção foi habilitada com prioridade 3. Essa interrupção sinaliza o momento de atualizar o *display*. Ao concluir a configuração de todos os componentes necessários, é gerado o código-fonte de inicialização em C através de “*Device Configuration Tool Code Generation*”. O CubeMX cria uma estrutura de dados de inicialização para cada componente, armazenando os valores configurados. Em seguida, ele insere no arquivo `main.c` chamadas às funções HAL correspondentes a cada componente, seguindo o padrão de nomenclatura `HAL_x_Init` e passando as respectivas estruturas de dados como argumento. Essa abordagem garante uma inicialização organizada e consistente dos componentes, além de facilitar a manutenção e melhorar a legibilidade do código.

9. O programa principal inclui a biblioteca “*Nokia\_5110*” usada em roteiro anterior para apresentar as linhas de texto. Ele ainda define as macros **ID**, **IDBASE** e **IDMASK**, sendo que a primeira deve definir um valor diferente para cada nó (**número do nó na rede**), entre 0 e 3,

e as outras duas são as mesmas em todos os nós, para definir o filtro de identificadores. **O código completo está disponível no Moodle.**

10. O código usa as mesmas variáveis para os *headers* e dados de transmissão e de recepção via CAN que foram usadas nos projetos anteriores. Ele ainda define um vetor de 4 elementos de 16 *bits* sem sinal para guardar os 4 valores dos ADCs: índice 0 para o nó 0, índice 1 para nó 1, e assim em diante.

11. O programa inicialmente configura o *display* e escreve “CAN DEMO” na primeira linha, esperando 5 segundos e apagando o *display*. Depois, inicia o CAN com parâmetros idênticos aos demais projetos, sendo que o identificador da mensagem é IDBASE mais o número do nó. Assim, os identificadores dos 4 nós serão 0xA0, 0xA1, 0xA2 e 0xA3. O filtro de identificador é definido com base 0xA0 (0b0000 1010 0000) e máscara 0x7FC (0b111 1111 1100), o que habilita identificadores de 11 *bits* com o valor binário igual a 0b000 1010 00XX. Os dois primeiros *bytes* de dados serão o valor do ADC (*Byte* mais significativo primeiro), enquanto que os demais serão sempre 0xAA. Por fim, o programa habilita o ADC e os *timers*.

12. A função *callback*<sup>1</sup> de conversão de ADC concluída, equivalente à ISR `ADC_IRQHandler`, coloca o *flag* `adcnovo` em 1. A função *callback* de *update* de TIM7, equivalente à ISR `TIM7_IRQHandler`, coloca a *flag* `update` em 1. A primeira *flag* indica que o valor novo do ADC deve ser escrito no vetor de valores (no índice que corresponde a seu número de nó) e a segunda indica que o *display* deve ser atualizado.

13. A função *callback* de evento da FIFO de recepção do controlador CAN, equivalente à rotina de serviço `FDCAN2_IT0_IRQHandler`, recupera a mensagem recebida, extrai o número do nó transmissor a partir do identificador, e guarda o valor recebido nos dois primeiros *bytes* na posição correspondente do vetor de valores.

14. No *loop* principal do programa, inicialmente é verificado se a *flag* de valor novo no ADC foi setada, e em caso positivo é montado o quadro de dados da mensagem CAN, e a mesma é transmitida. Além disso, o valor é guardado na posição correspondente ao número do nó do vetor de valores. Depois, verifica-se se a *flag* de atualização do *display* foi setada, e em caso positivo o *display* é atualizado.

Para demonstrar que o nó transmissor de uma mensagem não a recebe de volta em uma operação normal, realizamos uma pequena modificação no fluxo principal. Além das adaptações habituais do ambiente HAL (em inglês, *Hardware Abstraction Layer*) e CMSIS (em inglês, *Cortex Microcontroller Software Interface Standard*), optamos por armazenar o

---

<sup>1</sup> A ISR atua como um “gatilho” rápido para a ocorrência de um evento, e o *callback* implementado no nível de abstração HAL é a função que “reage” a esse gatilho, processando as informações e realizando as ações necessárias em um ambiente mais flexível e seguro, evitando que a ISR fique muito longa e bloquee outras interrupções ou o fluxo principal do programa.

valor lido em uma variável local, em vez de guardá-lo na posição do vetor “valor” de valores correspondente ao número do nó.

O código foi inserido no escopo `/* USER CODE BEGIN 3 */`

```

if(leADCFlag()) {

Stop_Conv();

//    valor[ID] = HAL_ADC_GetValue(&hadc1);

uint16_t data = leADCAmostra();

Start_Conv();

//    TxData[0] = data / 256;

//    TxData[1] = data % 256;

TxData[0] = data >> 8; // computo alternativo

TxData[1] = data & 0x00FF;

FDCAN2_AddMessageToTxFifoQ (IDBASE + ID);

}

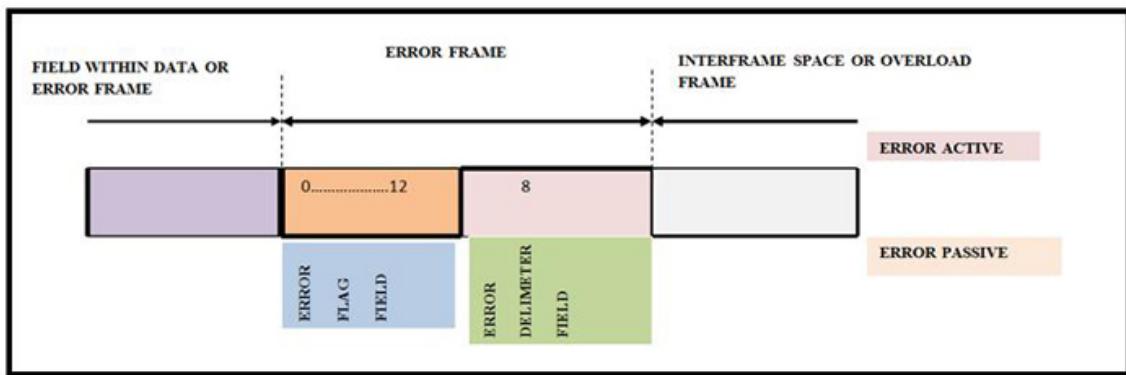

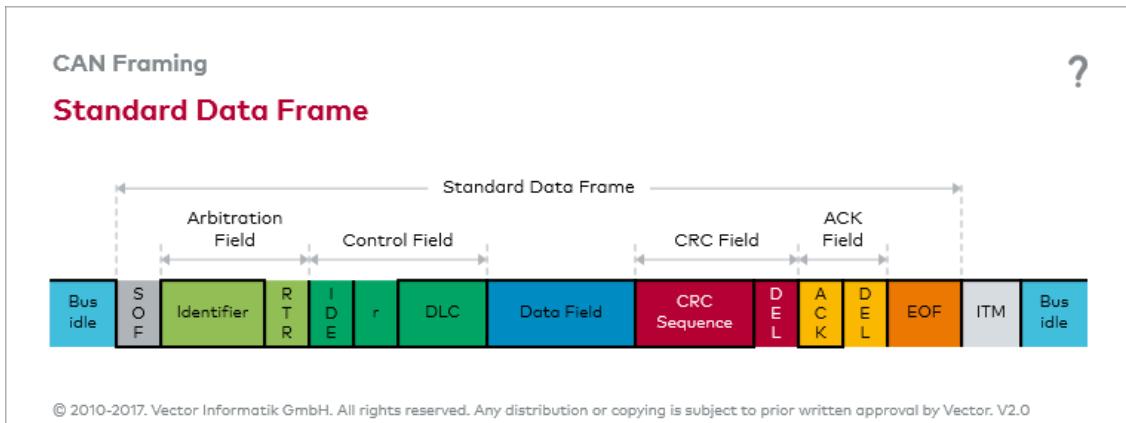

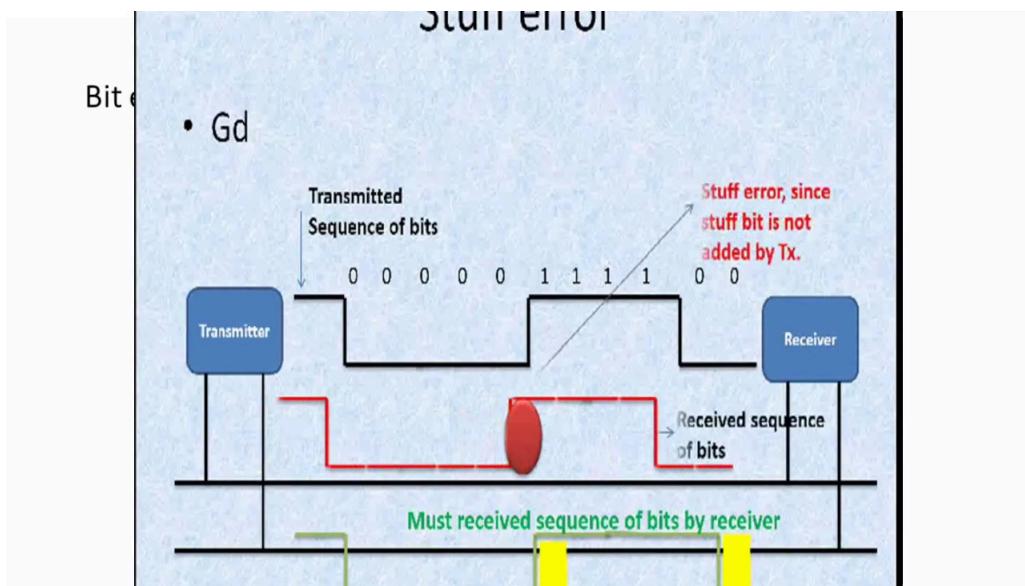

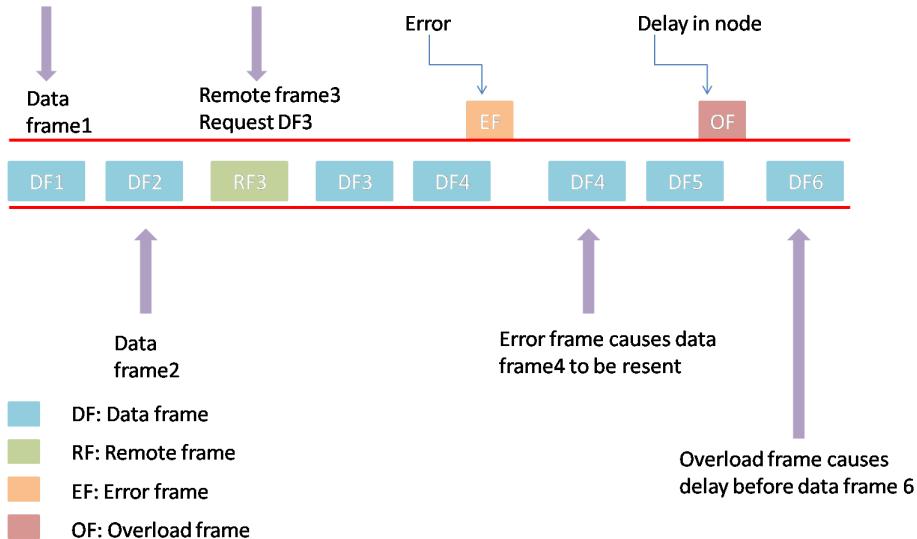

```