# **DISCIPLINA EA701**

## **Introdução aos Sistemas Embarcados**

### **ROTEIRO 12: Integração de HDL em Sistemas Embarcados: Da Teoria à Prática.**

**Níveis de Abstração de *Hardware*, Dispositivos Lógicos Programáveis (PLD), Linguagem de Descrição de *Hardware* (VHDL), Modelagem Gráfica Abstrata UML, Modelagem Comportamental (Sequencial) com Máquinas de Estados (FSM) e Máquinas de Estados e Caminho de Dados (FSMD).**

**Profs. Antonio A. F. Quevedo e Wu Shin-Ting**

**FEEC / UNICAMP**

**Revisado e modificado em junho de 2025 por Ting com auxílio do Chatgpt

Revisado em novembro de 2024**

This work is licensed under Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International. To view a copy of this license, visit <https://creativecommons.org/licenses/by-nc-sa/4.0/>

|                                                                                  |           |

|----------------------------------------------------------------------------------|-----------|

| <b>INTRODUÇÃO</b>                                                                | <b>2</b>  |

| <b>PROJETOS-EXEMPLO</b>                                                          | <b>5</b>  |

| Projeto 1: Usando o ambiente EDA Playround e simulando um circuito combinacional | 5         |

| Projeto 2: Descrevendo e simulando um circuito sequencial                        | 16        |

| Projeto 3: Criando um controlador na arquitetura FSMD                            | 26        |

| <b>FUNDAMENTOS TEÓRICOS</b>                                                      | <b>40</b> |

| NÍVEIS DE ABSTRAÇÃO DE HARDWARE                                                  | 41        |

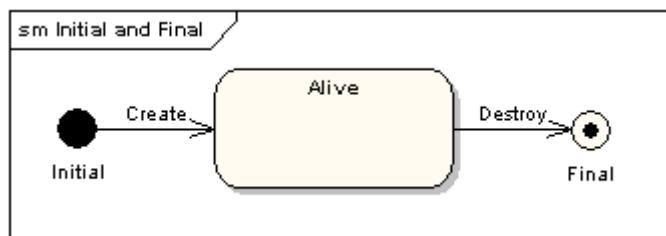

| MÁQUINA DE ESTADOS FINITOS                                                       | 45        |

| Tabelas de transição de estados                                                  | 48        |

| UML: Uma linguagem gráfica                                                       | 48        |

| DISPOSITIVOS DE LÓGICA PROGRAMÁVEL                                               | 54        |

| Captura esquemática                                                              | 59        |

| Linguagem de descrição de hardware                                               | 60        |

| VHDL                                                                             | 62        |

| Estrutura básica                                                                 | 63        |

| Tipos de dados                                                                   | 64        |

| Operadores                                                                       | 65        |

| Instruções concorrentes                                                          | 67        |

| Instruções sequenciais                                                           | 69        |

| Pacotes e bibliotecas                                                            | 71        |

| Banco de testes                                                                  | 71        |

| Exemplos                                                                         | 72        |

| Correspondências entre esquemáticos e VHDLs                                      | 79        |

| FSMD: UMA METODOLOGIA PARA O PROJETO DE CIRCUITOS DEDICADOS                      | 80        |

| Projeto de um processador dedicado                                               | 87        |

## INTRODUÇÃO

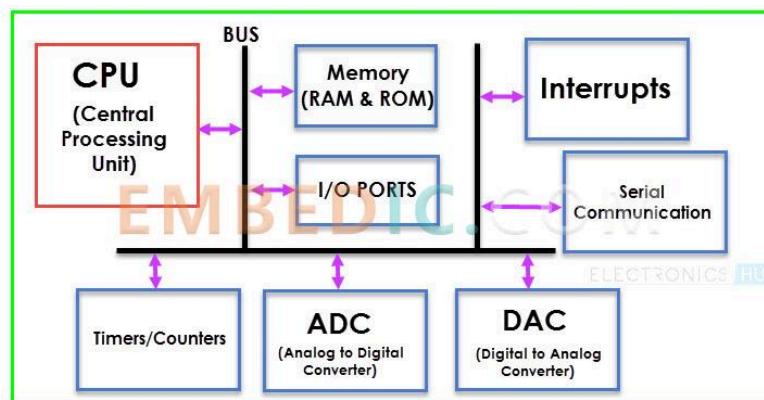

No universo dos sistemas embarcados, a intersecção entre *hardware* e *software* é fundamental para o sucesso de projetos inovadores. Nesse cenário, a programabilidade dos microcontroladores se destaca como um diferencial, permitindo personalizar funcionalidades do *hardware* por meio de *software* como vimos nos Roteiros anteriores, adaptando dispositivos a uma ampla gama de aplicações com flexibilidade e agilidade. Essa capacidade de reconfiguração dinâmica torna possível implementar algoritmos de controle, comunicação e processamento de sinais diretamente no dispositivo, acelerando o desenvolvimento e reduzindo custos com prototipagem.

No entanto, há mecanismos eletrônicos que permanecem intrinsecamente dependentes de soluções a nível de *hardware*, mesmo no estado-da-arte da tecnologia. Exemplos notáveis incluem conexões do tipo *wired-and*, comumente utilizadas em barramentos de comunicação

como o I2C, como vimos no Roteiro 10, e a lógica de arbitragem baseada em *bits* dominantes e recessivos, típica do protocolo CAN, apresentada no Roteiro 11. Tais técnicas exploram características elétricas dos circuitos, como impedância e níveis de tensão, que não podem ser emuladas de forma confiável apenas via *software*, exigindo um projeto de *hardware* específico e dedicado. Outro exemplo é o combate a ruídos eletromagnéticos (em inglês, *Electromagnetic Interference* - EMI, *Radio Frequency Interference* - RFI) em sinais de entrada dos microcontroladores, mostrados no Roteiro 8. Como esses ruídos são fenômenos físicos (ondas eletromagnéticas ou correntes parasitas que se acoplam aos sinais), sua atenuação exige intervenção no nível físico do sinal, sendo amplamente tratada por *hardware* na maioria dos sistemas eletrônicos.

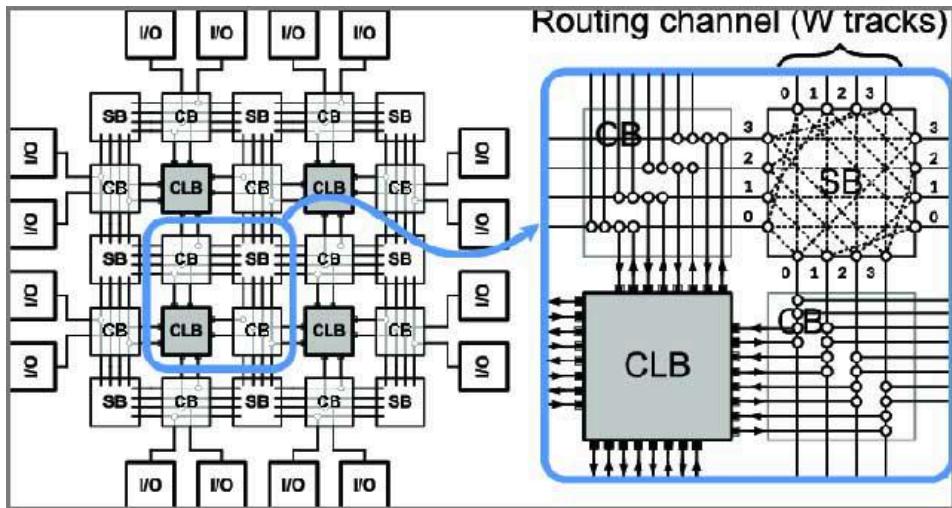

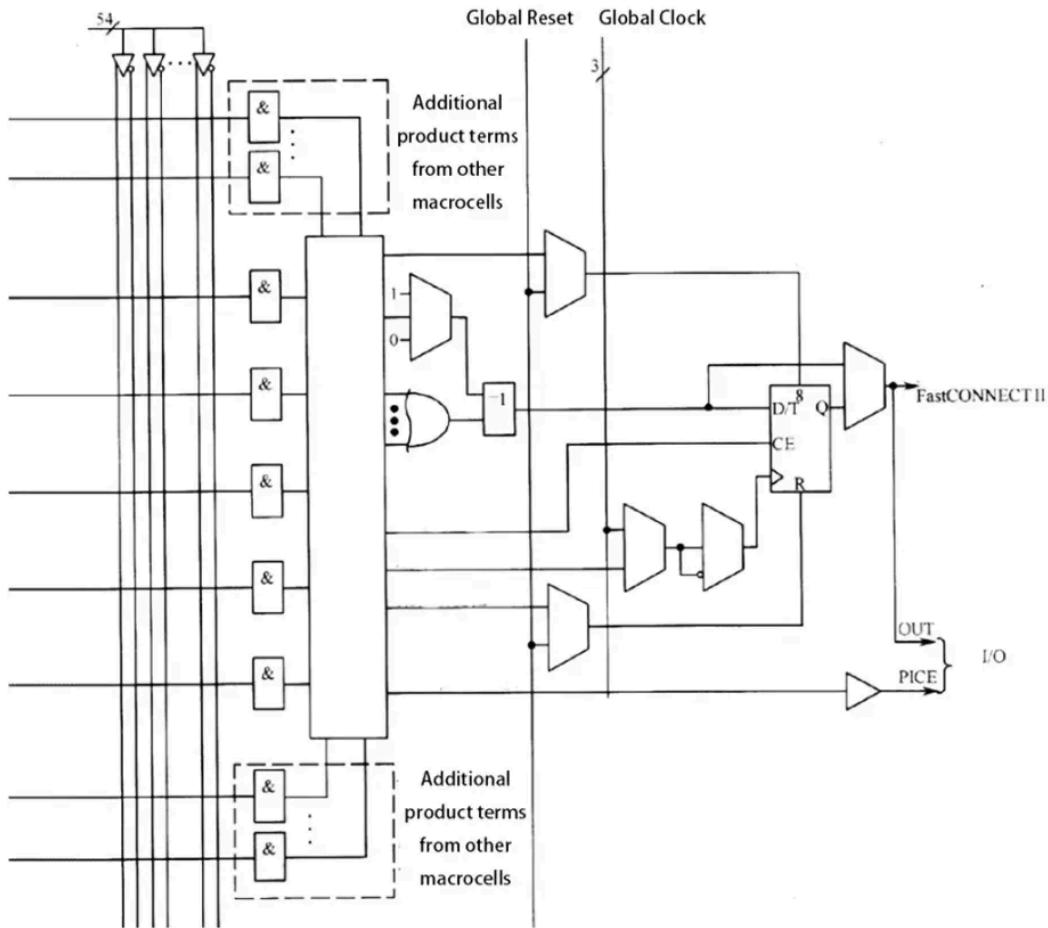

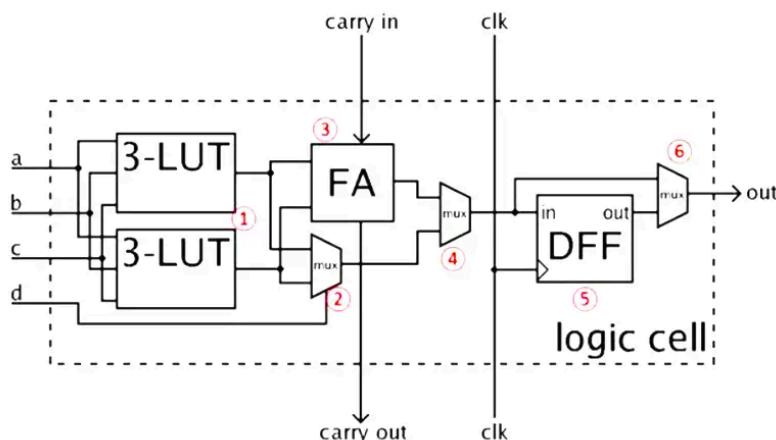

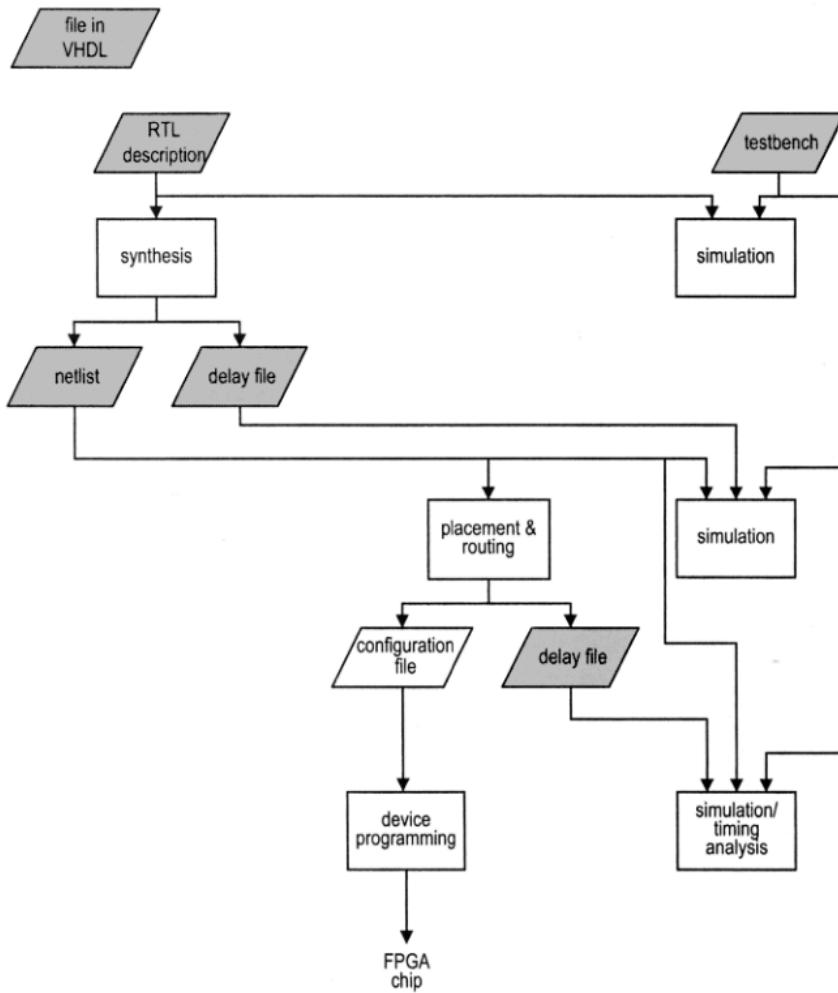

Nesse contexto, a linguagem HDL (do inglês *Hardware Description Language*) emerge como uma ferramenta essencial para a descrição e implementação de circuitos digitais em dispositivos de lógica programável do estado da arte, como FPGAs e ASICs. Dispositivos de Lógica Programável (em inglês, *Programmable Logic Devices* - PLDs) são componentes eletrônicos que permitem aos *designers* configurar sua lógica interna, em vez de serem fabricados para uma função fixa específica. Isso oferece uma incrível flexibilidade no desenvolvimento de *hardware*, permitindo que a funcionalidade de um *chip* seja definida ou alterada por meio de “programação”. Os PLDs modernos, como as FPGAs (do inglês *Field-Programmable Gate Arrays*), consistem em uma matriz de blocos lógicos configuráveis e interconexões programáveis, o que lhes permite implementar virtualmente qualquer circuito digital. Já os ASICs (do inglês *Application-Specific Integrated Circuits*) são circuitos integrados projetados para uma aplicação específica e são fabricados sob medida para uma função particular, oferecendo o máximo em desempenho e eficiência, mas com custos de desenvolvimento e fabricação muito mais altos e sem a flexibilidade de reprogramação. A figura que segue ilustra a lógica interna de um FPGAs. Ela é composta por um conjunto de blocos lógicos reconfiguráveis (em inglês, *Configurable Logic Block* - CLB), interconectados por uma rede programável de roteamento formada pelos blocos de conexão (em inglês, *Connection Block* - CB) e blocos de chaveamento (em inglês, *Switch Block* - SB) elementos de memória. Essa configuração é definida e carregada no dispositivo por meio de uma HDL, como VHDL (do inglês *Very high speed integrated circuit Hardware Description Language*) ou Verilog.

Fonte: [WELLPCB](#)

Assim, a HDL abre as portas para o futuro da engenharia digital, onde o conceito de “desenhar” um circuito vai além da simples montagem de componentes físicos e esquemáticos. Ela oferece novas perspectivas no *design* e na implementação de sistemas eletrônicos avançados, permitindo que engenheiros descrevam o comportamento e a estrutura dos PLDs de forma abstrata, facilitando o *design*, a verificação e a síntese para diferentes plataformas de *hardware*. A capacidade de modelar o comportamento do *hardware* de forma precisa permite que engenheiros e desenvolvedores criem soluções que não apenas atendam aos requisitos funcionais, mas que também sejam otimizadas em termos de desempenho, eficiência e compatibilidade elétrica, inclusive para lidar com essas exigências que só podem ser resolvidas no domínio físico dos circuitos. Ao longo deste semestre, vimos que, com a crescente complexidade dos sistemas embarcados, especialmente através do uso de microcontroladores avançados como o STM32, a integração entre *software* e *hardware* se torna cada vez mais complementar. Enquanto o STM32 oferece recursos robustos de processamento, temporização e controle periférico, o uso de HDL permite aos projetistas definir e implementar, de forma altamente personalizada, funções específicas de *hardware*, como interfaces de comunicação e controle de sinais críticos.

Essa abordagem integrada possibilita a maximização das capacidades do sistema, explorando o melhor dos dois mundos: a flexibilidade do *software* e a precisão do *hardware*. Assim, é possível desenvolver soluções embarcadas cada vez mais robustas, eficientes e adaptadas às exigências do ambiente real. Neste roteiro, vamos apresentar uma visão introdutória sobre o potencial da modelagem de *hardware* e sua sinergia com a programação de microcontroladores. Nossa objetivo é explorar a perspectiva do **co-projeto**, usando exemplos práticos e discutindo aplicações reais. Queremos destacar como a descrição de *hardware* se torna um elemento cada vez mais relevante no desenvolvimento de sistemas embarcados robustos e eficientes.

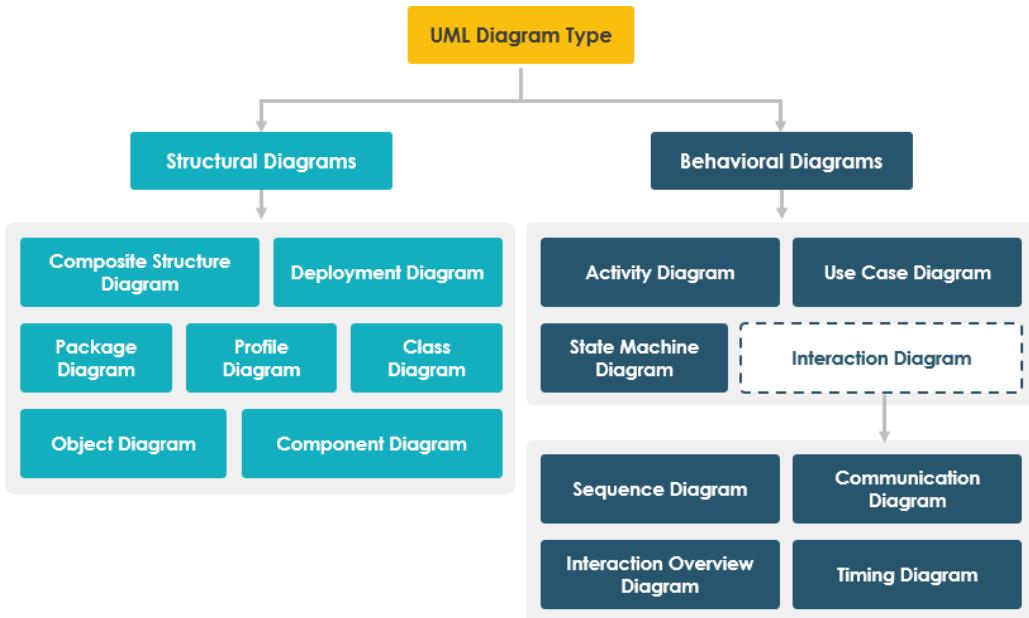

Este roteiro guiará você por uma introdução ao co-projeto de sistemas embarcados, destacando a integração entre o design de hardware e software para alcançar soluções mais

eficientes e otimizadas. Começaremos com os níveis de abstração de *hardware*, desde o nível de portas lógicas até o nível de sistema, estabelecendo uma base sólida para compreender a hierarquia do projeto digital. Em seguida, apresentaremos os dispositivos lógicos programáveis (PLDs), discutindo suas características, aplicações e papéis no desenvolvimento de *hardware* configurável. A seguir, introduziremos a linguagem VHDL, explorando sua sintaxe e uso para a descrição comportamental e estrutural de circuitos digitais, além de sua íntima relação com máquinas de estados. Para auxiliar na modelagem e na comunicação entre equipes multidisciplinares, abordaremos a UML (do inglês *Unified Modeling Language*) como ferramenta complementar ao projeto de *hardware*. Daremos continuidade com o estudo do FSDM (do inglês *Finite State Machine Design Method*), uma abordagem fundamental para o controle sequencial em circuitos digitais, especialmente em sistemas embarcados.

Devido a limitações de infraestrutura, nossos projetos de *hardware* se restringirão a simulações. No entanto, com o conhecimento que você adquiriu nos roteiros anteriores, essas simulações serão suficientes pra demonstrar que os sinais físicos gerados, como os enviados pelo microcontrolador e analisados por um analisador lógico, são integráveis no nível de simulação.

## PROJETOS-EXEMPLO

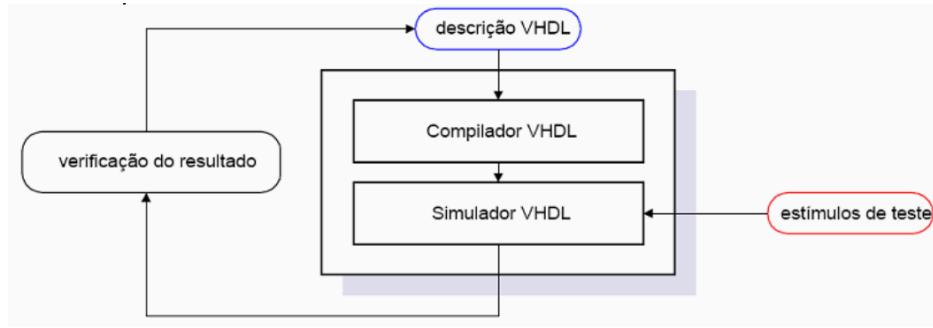

Esta seção apresenta projetos-exemplo que combinam a modelagem gráfica de sistemas digitais utilizando UML (do inglês, *Unified Modeling Language*) e a descrição de *hardware* com VHDL. A abordagem explora como UML pode ser empregada para documentar e organizar funcionalmente o *design* de circuitos digitais, enquanto o VHDL traduz essas especificações em implementações sintetizáveis para dispositivos PLDs, como FPGAs ou ASICs. Além disso, os projetos são desenvolvidos e testados em um ambiente de simulação *online*, como o EDA Playground, permitindo validação prática e aprendizado interativo.

### Projeto 1: Usando o ambiente EDA Playground e simulando um circuito combinacional

Em vez de se preocupar com a construção física de circuitos utilizando componentes discretos como transistores, portas lógicas e resistores, já imaginou poder sintetizar um controlador dedicado, como um conversor ADC ou um periférico UART, utilizando apenas uma linguagem que descreve o comportamento lógico e funcional do circuito? E, a partir dessa descrição, deixar que um sintetizador transforme essa representação em um circuito físico real? Este projeto combinacional de um **decodificador 3 para 8** tem como objetivo apresentar o VHDL como uma ferramenta para descrever, simular e sintetizar circuitos digitais (*hardware*) em dispositivos lógicos programáveis, como FPGAs.

É importante destacar que a descrição feita em VHDL não se limita a um modelo teórico: ela é convertida em um circuito combinacional real, com comportamento físico equivalente ao de um circuito construído com portas lógicas e conexões entre elas. Assim, quando é especificada uma rota da entrada até a saída, o sinal percorre todos os caminhos possíveis, como água fluindo em uma rede de canalização, propagando-se pelos fios e portas internas do dispositivo. Essa propagação de sinais não ocorre instantaneamente: existe um tempo de propagação associado a cada estágio do circuito, que corresponde ao intervalo necessário para que uma mudança na entrada se reflita na saída. Esse fator é crucial no projeto digital, pois influencia diretamente o desempenho do circuito e deve ser considerado tanto na simulação quanto na síntese. Em sistemas mais complexos, o tempo de propagação afeta o *timing* global e pode limitar a frequência máxima de operação do sistema. Essa natureza física e paralela dos circuitos se reflete diretamente na forma como o código VHDL deve ser interpretado. **Diferentemente das linguagens de programação tradicionais, onde a execução segue uma ordem sequencial de comandos, em uma linguagem de descrição de hardware, as instruções não são executadas em sequência, mas representam estruturas que operam simultaneamente.** Cada declaração no código HDL descreve um componente ou comportamento que será sintetizado como parte de um sistema de *hardware* operando em paralelo. Assim, a síntese do sistema a partir do código HDL gera uma arquitetura composta por **módulos paralelos e interconectados**, não uma linha de execução sequencial.

Esse comportamento evidencia uma das diferenças fundamentais entre a linguagem de programação de um microcontrolador e uma linguagem de descrição de *hardware* como o VHDL. Ao programar um microcontrolador, os sinais e caminhos de execução já estão predefinidos pela arquitetura interna do *chip*: o programador atua sobre registradores, periféricos e instruções de controle de fluxo, sem alterar a estrutura física do *hardware*. Por outro lado, ao usar uma linguagem de descrição de *hardware*, o desenvolvedor é responsável por definir os próprios sinais, conexões e caminhos lógicos que constituirão fisicamente o circuito. Isso implica que uma especificação incorreta em VHDL pode resultar em comportamentos de *hardware* totalmente erráticos ou até perigosos, uma vez que o erro está na própria definição estrutural do circuito — não apenas na lógica de controle. Diferentemente de *bugs* em *software*, que geralmente se manifestam como falhas previsíveis ou reinicializações, erros em *hardware* descrito incorretamente podem gerar conflitos elétricos, falhas de sincronização ou resultados lógicos imprevisíveis, com impactos potencialmente mais severos.

O [EDA Playground](#) é uma plataforma *online* gratuita para desenvolvimento, simulação e compartilhamento de códigos relacionados a *design* e verificação de circuitos digitais, especialmente voltados para a área de *Electronic Design Automation* (EDA). A plataforma é amplamente utilizada para experimentar linguagens de descrição de *hardware* como *SystemVerilog*, *Verilog*, e *VHDL*. Com o EDA Playground, é possível escrever e simular códigos diretamente no navegador, sem a necessidade de instalar ferramentas locais.

É possível ainda escolher ferramentas de simulação entre várias disponíveis, incluindo *Synopsys VCS*, *Cadence Incisive*, e *Mentor Graphics ModelSim*, que são simuladores

amplamente utilizados na indústria. Pode-se usar bibliotecas e modelos prontos para testes e verificação, bem como compartilhar projetos facilmente com colegas, professores ou em apresentações, já que ele gera um *link* público para seu código e resultados de simulação. É uma ferramenta valiosa para aprendizado e prototipagem rápida, principalmente para quem deseja aprender ou *praticar design* e verificação de circuitos digitais sem precisar configurar um ambiente local de desenvolvimento EDA.

**Para realizar as simulações em VHDL do roteiro, será necessário criar uma conta na plataforma, pois o acesso aos simuladores comerciais (os gratuitos não funcionam bem com o VHDL) só é dado para portadores de contas.** Além disso, a conta permite guardar os *Playgrounds* (que é o nome dado aos projetos de simulação), bem como compartilhá-los através de *links*. Abaixo está um guia passo-a-passo para criar uma conta e um novo *Playground* devidamente configurado para uma simulação VHDL.

**IMPORTANTE:** Preferencialmente, abra uma janela privativa no navegador (“Open a New Private Window”). Após feito o *login* na conta, parece que o *logout* não funciona muito bem. Em uma janela normal, sua conta ficará disponível para outros. Com a janela privativa, o acesso da conta é “esquecido” pelo navegador, demandando novo *login*.

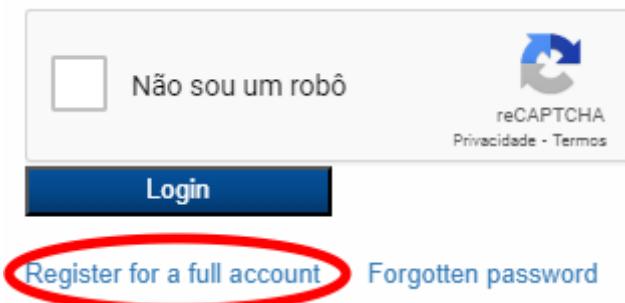

1. Acesse o site <https://www.edaplayground.com>. Na frente da página principal, abrirá uma janela de boas-vindas sugerindo a criação de uma conta. **NÃO** realize o login com Google! Para poder usar as melhores ferramentas de simulação e síntese, será necessário criar uma conta com um email institucional, e o e-mail da Unicamp serve perfeitamente para esta finalidade. Desça a janela até o final. Logo abaixo do botão de *Login* há um *link* chamado “Register for a full account”.

2. Na página que se abre, informe seus dados para a conta, começando com o e-mail institucional (o da DAC), e criando uma senha, além do nome da instituição (“University of Campinas”), nome, cidade e país. Se for obrigatório o *Job Title*, pode-se preencher com “Student”. No final da página, selecione o *Captcha* e clique no botão “I Agree”.

3. Após fornecer os dados, a página informa que o email deve ser verificado. Feche a página, vá ao seu email e clique no *link* de verificação. A página do EDA Playground abrirá

novamente, já logada em sua conta. Quando for entrar outra vez, na página inicial basta fornecer o email e a senha e depois confirmar o *Captcha*.

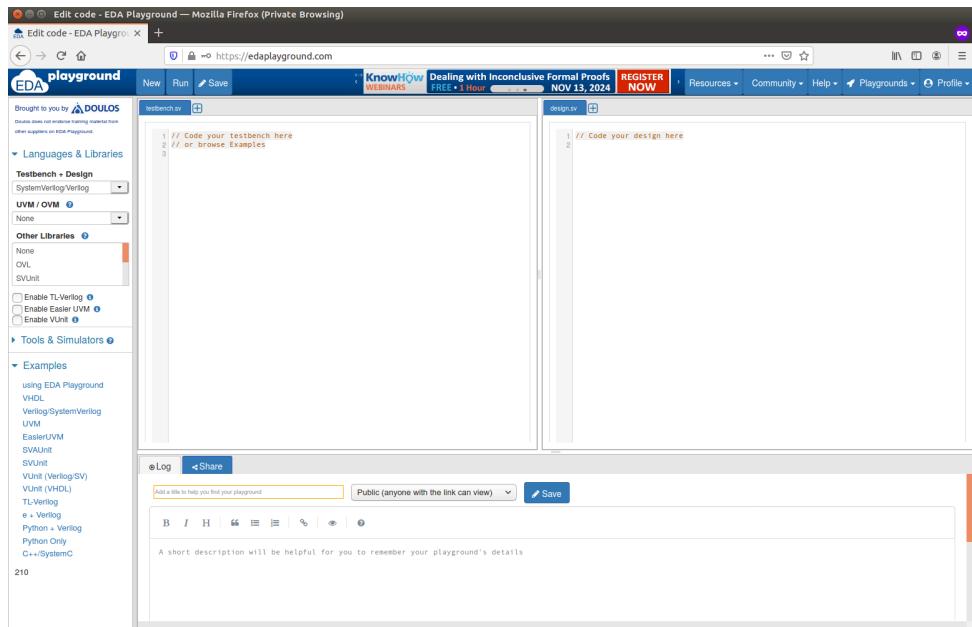

4. O painel principal tem em sua parte central duas janelas de edição. A janela da esquerda é para o arquivo de *testbench* (que determina as condições de simulação e fornece os sinais nas entradas do *hardware* simulado). A janela da direita é para o arquivo principal com a descrição do *hardware*. Os comentários iniciais nos textos das janelas descrevem suas finalidades.

5. Na barra superior, há alguns botões. Os mais importantes são: *New* (novo projeto), *Run* (executar simulação), *Save* (guardar projeto), “Playgrounds” (acessa a lista de projetos) e “Profile” (configura o perfil). Vamos inicialmente em “Profile”. Na página que se abrir, marque a caixa “Open EPWave waveforms on a separate page after run”. Esta opção faz com que as formas de onda simuladas sejam abertas em outra aba no navegador, e não por cima da janela principal. Depois clique no botão “Save Details” para salvar a configuração e, na parte superior, no botão “New” para voltar à tela principal.

6. No painel à esquerda, estão as opções gerais para a simulação. Inicialmente, expanda o menu ***Languages & Libraries***. A opção ***Testbench + Design*** define a linguagem de descrição que será utilizada, sendo que o padrão é o Verilog. Selecione a opção “**VHDL**” e note que os textos nas janelas de edição mudam. Agora os comentários seguem o padrão VHDL e já foi incluída a biblioteca padrão. As demais opções podem permanecer inalteradas, mas é necessário adicionar informação no campo ***Top entity***. Este campo determina qual é a entidade VHDL que ocupa o topo da hierarquia. Em cada uma de nossas simulações, será criada uma entidade para o *testbench*, que será o topo da hierarquia de testes do projeto. Basta copiar o nome (que se segue à palavra chave *entity*) e colar no campo do painel à esquerda. O nome de entidade que vamos projetar é `decodificador_3para8` e a sua arquitetura de banco de testes será denominada `decodificador_3para8_tb`.

```

1 -- Code your testbench here

2 library IEEE;

3 use IEEE.std_logic_1164.all;

4

5 entity tb_decodificador_3para8 is

6 end tb_decodificador_3para8;

7

8 architecture Behavioral of tb_decodificador_3para8 is

9 signal entrada : STD_LOGIC_VECTOR(2 downto 0) := "000";

10 signal enable : STD_LOGIC := '0';

11 signal saida : STD_LOGIC_VECTOR(7 downto 0);

12

13 -- Instancia o módulo do decodificador

14 component decodificador_3para8

15     Port (

16         entrada : in STD_LOGIC_VECTOR(2 downto 0);

17         enable : in STD_LOGIC;

18         saida : out STD_LOGIC_VECTOR(7 downto 0)

19     );

20 end component;

21

```

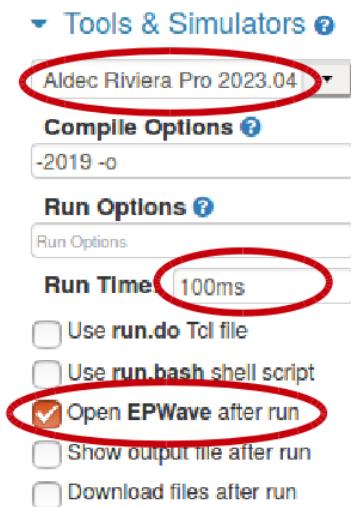

7. Agora expanda o menu **Tools & Simulators**. O primeiro item é um *dropdown* com a palavra “Select...”. Clique nele para selecionar o simulador a ser usado. Nas simulações deste roteiro, foi usado o **Aldec Riviera Pro 2023.04**. Mantenha as demais opções no padrão, exceto a **Run Time**, que deve ser ajustada para o tempo total de simulação, e a caixa **Open EPWave after run**, que indica que após a simulação deve-se abrir a aba com as formas de onda.

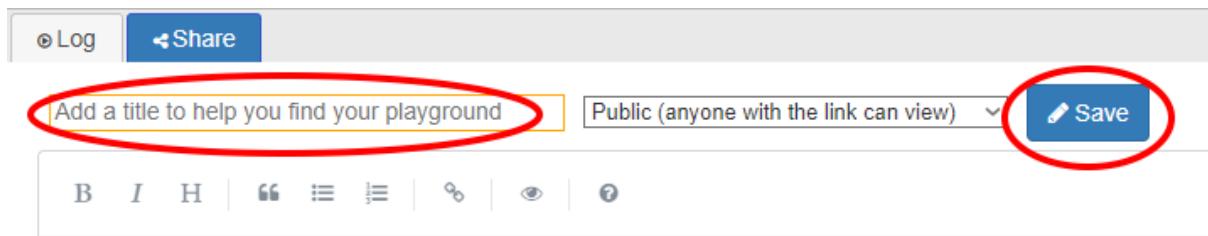

8. Com as configurações ajustadas, pode-se gravar o *Playground*. No painel central inferior, na aba “Share”, há um campo para escrever o nome do *Playground*. Escreva “decodificador\_3para8”, clicando-se logo depois no botão “Save”.

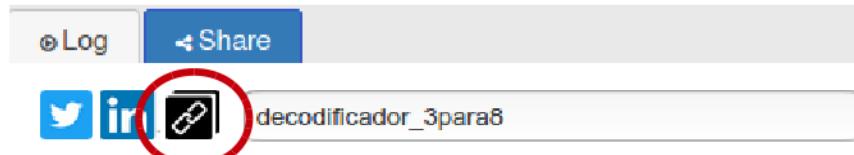

Após isso, aparecem no mesmo painel ícones de redes sociais e um ícone com uma corrente, para compartilhar o *Playground*. O ícone da corrente copia o *link* da página do *Playground* para a área de transferência.

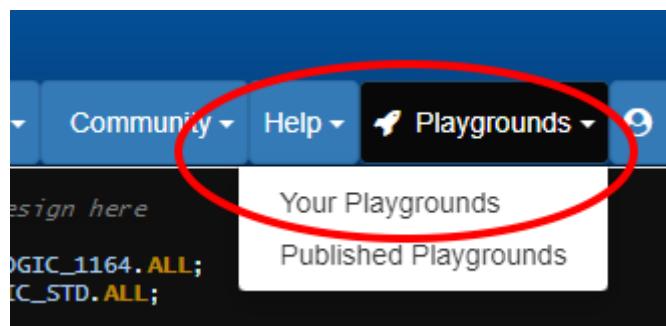

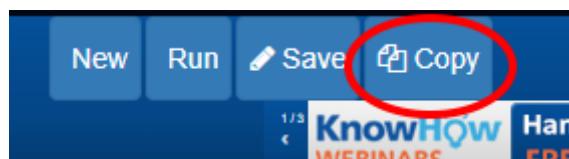

Qualquer pessoa, estando logada em sua própria conta, pode abrir o *link* e clicar no botão “Copy” do menu superior para guardar uma cópia do *Playground* original em sua própria conta. Todos os *Playgrounds* gravados podem ser acessados através do botão “Playgrounds”, opção “Your Playgrounds”.

9. Neste ponto, deve-se criar o código do VHDL (*design.vhd*) e do *testbench*. Na janela da **direita** coloque o primeiro código, que descreve um decodificador de 3 para 8 linhas com *enable*. Neste decodificador, todas as linhas permanecem em nível alto exceto aquela cujo número corresponde ao valor binário das 3 entradas. Caso o *enable* tenha o valor baixo, todas as saídas permanecem em nível alto.

```

-- Code your design here

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

```

entity decodificador\_3para8 is

```

Port (

entrada : in STD_LOGIC_VECTOR(2 downto 0); -- Entrada de 3 bits

enable : in STD_LOGIC;                      -- Sinal de habilitação

saída : out STD_LOGIC_VECTOR(7 downto 0) -- Saída de 8 bits

);

end decodificador_3para8;

```

```

architecture Behavioral of decodificador_3para8 is

begin

process(entrada, enable)

begin

if enable = '1' then

case entrada is

when "000" => saída <= "11111110";

when "001" => saída <= "11111101";

when "010" => saída <= "11111011";

when "011" => saída <= "11110111";

when "100" => saída <= "11101111";

when "101" => saída <= "11011111";

when "110" => saída <= "10111111";

when "111" => saída <= "01111111";

when others => saída <= "11111111";

end case;

else

saída <= "11111111"; -- Saída 1 quando enable é 0

end if;

end process;

end Behavioral;

```

Na janela da **esquerda** coloque o código do *testbench*. Neste código é criada uma sequência de valores nas entradas digitais para cobrir todas as possibilidades. A duração de cada grupo de valores é de 15ms.

```

-- Code your testbench here

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity tb_decodificador_3para8 is

end tb_decodificador_3para8;

architecture Behavioral of tb_decodificador_3para8 is

signal entrada : STD_LOGIC_VECTOR(2 downto 0) := "000";

signal enable : STD_LOGIC := '0';

signal saída : STD_LOGIC_VECTOR(7 downto 0);

```

```

-- Instancia o módulo do decodificador

component decodificador_3para8

Port (

entrada : in STD_LOGIC_VECTOR(2 downto 0);

enable : in STD_LOGIC;

saida  : out STD_LOGIC_VECTOR(7 downto 0)

);

end component;

begin

uut: decodificador_3para8 Port map (

entrada => entrada,

enable => enable,

saida => saida

);

-- Estímulo de teste

process

begin

-- Ativa o enable e verifica todas as entradas

enable <= '1';

wait for 15 ms; entrada <= "000";

wait for 15 ms; entrada <= "001";

wait for 15 ms; entrada <= "010";

wait for 15 ms; entrada <= "011";

wait for 15 ms; entrada <= "100";

wait for 15 ms; entrada <= "101";

wait for 15 ms; entrada <= "110";

wait for 15 ms; entrada <= "111";

-- Desativa o enable e observa a saída zerada

wait for 15 ms; enable <= '0';

entrada <= "000";

-- Finaliza a simulação

wait for 15 ms;

wait;

end process;

end Behavioral;

```

São 10 possibilidades testadas, portanto o tempo de simulação deve ser ajustado em 100ms. O nome da “Top entity” deve ser “tb\_decodificador\_3para8”. Depois, pode-se salvar tudo,

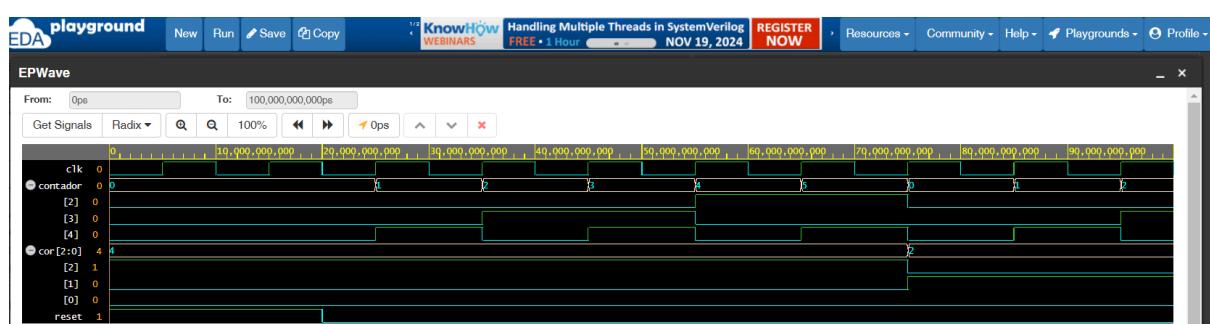

clicando no botão “Save”, e usar o botão “Run” no lado esquerdo da aba superior para simular o projeto. Após concluir a simulação (caso não haja erros), abre-se nova aba com as formas de onda.

**Obs:** Caso use um navegador com bloqueador de *pop-ups*, será necessário permitir os *pop-ups* para o site [www.edaplayground.com](http://www.edaplayground.com).

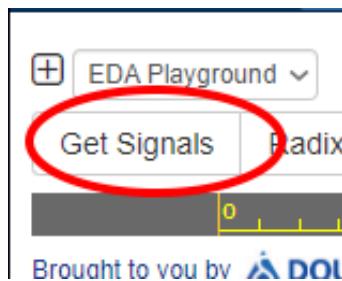

10. Na janela das formas de onda, os sinais podem aparecer ou não. Caso não apareçam os sinais, será necessário selecionar os sinais a serem apresentados. Clique no botão “Get Signals” e na janela que se abre, à esquerda (*Scope*) selecione o nome da entidade do *testbench*. Os nomes dos sinais do *testbench* vão aparecer. Clique no botão “Append All”, para incluir todos os sinais.

Há ainda um segundo nome no *Scope*: .UUT (do inglês *Unit Under Test*). O conjunto de sinais da entidade do *testbench* se refere às portas de entrada e saída externas do *design* de nível superior, permitindo que monitoremos como o circuito interage com o ambiente simulado em um nível macro. Já o conjunto .DUT oferece acesso a **todos os sinais internos e externos** da instância do projeto que está sendo testada. Essa capacidade de visualizar os sinais internos do .UUT, ou .DUT (do inglês *Device Under Test*), é fundamental para **identificar e diagnosticar problemas** que não são visíveis apenas pelas portas externas, permitindo uma análise granular e a validação detalhada do comportamento de cada componente interno do seu projeto. A relevância reside na habilidade de alternar entre uma visão de alto nível do sistema e uma inspeção minuciosa dos seus componentes, otimizando o processo de verificação do *hardware*.

Depois use as ferramentas de *zoom* (lupas) e cursores de tempo (CTRL-Click).

Os sinais podem ser apagados (selecionar a linha do sinal e clina em ‘x’ laranja) e podem ter sua ordem modificada. Os agrupamentos de sinais podem ser expandidos para os sinais individuais e vice-versa. A interface é bastante intuitiva.

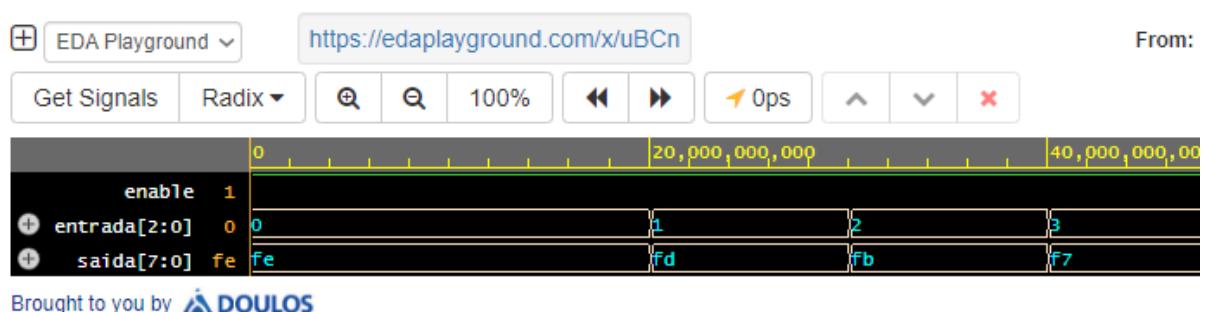

11. As formas de onda exibidas na imagem do item 10 não mostram todas as 10 possibilidades de saída. Quais (re)configurações seriam necessárias para exibir todas as saídas possíveis?

12. Se tentarmos interpretar a descrição em HDL do item 9 sob a ótica de um programador acostumado a microcontroladores, poderíamos supor, equivocadamente, que o sinal de saída será atualizado apenas após alguns ciclos de relógio, talvez dois ou três, após a “execução” de uma instrução que compara o valor da variável enable com ‘1’.

```

architecture Behavioral of decodificador_3para8 is

begin

process(entrada, enable)

begin

if enable = '1' then

case entrada is

when "000" => saida <= "11111110";

when "001" => saida <= "11111101";

when "010" => saida <= "11111011";

when "011" => saida <= "11110111";

when "100" => saida <= "11101111";

when "101" => saida <= "11011111";

when "110" => saida <= "10111111";

when "111" => saida <= "01111111";

when others => saida <= "11111111";

end case;

else

saida <= "11111111"; -- Saída 1 quando enable é 0

end if;

end process;

end Behavioral;

```

Esse raciocínio faz sentido em linguagens imperativas como C, onde há uma sequência clara de execução passo a passo. No entanto, no contexto de uma HDL, essa leitura deve ser completamente diferente. Aqui, não existe uma linha de execução sequencial tradicional. O código HDL descreve um comportamento estrutural e paralelo que será fisicamente sintetizado em lógica digital. Em vez de “executar” instruções, estamos descrevendo como o circuito será construído — e esse circuito reage continuamente às mudanças nas entradas, propagando sinais de acordo com as conexões definidas.

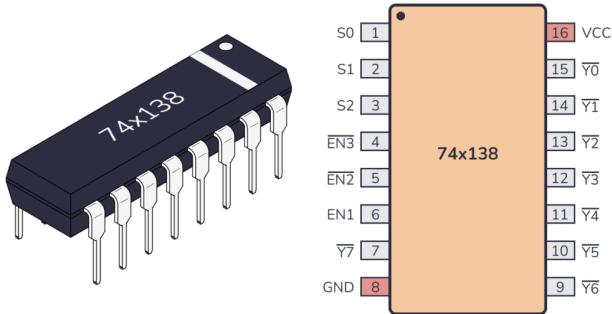

Para entender melhor, imagine que essa descrição seja sintetizada em um circuito combinacional semelhante a um decodificador [74138](#). Nesse cenário, a lógica é implementada fisicamente com portas lógicas conectadas de forma fixa. O que acontece com o valor de saída tão logo os sinais de entrada mudam? São necessários ciclos de execução? Como os resultados se propagam pelas portas lógicas até atingir a saída? Com esse novo olhar, observe atentamente as formas de onda geradas pelo simulador. Quando a saída 0b11111110 é ativada ao colocarmos 0b000 na entrada? Isso reflete o comportamento típico de um circuito combinacional: as saídas respondem automaticamente às entradas, dentro dos limites físicos do tempo de propagação.

Fonte: [buildelectroniccircuits](http://buildelectroniccircuits.com)

**Portanto, para interpretar corretamente sistemas descritos em HDL, é essencial abandonar o modelo mental sequencial de execução e adotar uma perspectiva de ativação simultânea e reatividade contínua. Isso é o que diferencia fundamentalmente uma linguagem de descrição de *hardware* de uma linguagem de programação para microcontroladores.**

13. No *testbench* de especificação de testes, modifique o intervalo dos sinais de 15ms para 10ms. Em seguida, execute a simulação (“Run”) e compare as formas de onda geradas neste teste com as do teste anterior. Como os valores dos parâmetros de teste podem afetar nos resultados de simulação? Como os valores dos parâmetros de teste podem afetar os resultados da simulação?

Note que os valores dos parâmetros definidos no *testbench* controlam os **estímulos de entrada** que o dispositivo sob teste (DUT) ou a unidade sob teste (UUT) recebe.

14. No arquivo de especificação do circuito, *design.vhd*, modifique a saída nas linhas 23 e 24 conforme indicado na seguinte figura. Em seguida, execute a síntese e a simulação (“Run”) e compare as formas de onda geradas neste teste com as do teste anterior. Como a descrição do comportamento de um circuito afeta os resultados da simulação?

A descrição do comportamento de um circuito em uma linguagem de descrição de *hardware* (HDL), como VHDL, é a definição literal de como seu *hardware* funcionará. Qualquer alteração nessa descrição altera diretamente a lógica que o simulador (e posteriormente o *hardware* físico) irá implementar.

```

18      case entrada is

19        when "000" => saida <= "11111110";

20        when "001" => saida <= "11111101";

21        when "010" => saida <= "11111011";

22        when "011" => saida <= "11110111";

23        when "100" => saida <= "11100011";

24        when "101" => saida <= "11011001";

25        when "110" => saida <= "10111111";

26        when "111" => saida <= "01111111";

27        when others => saida <= "11111111";

```

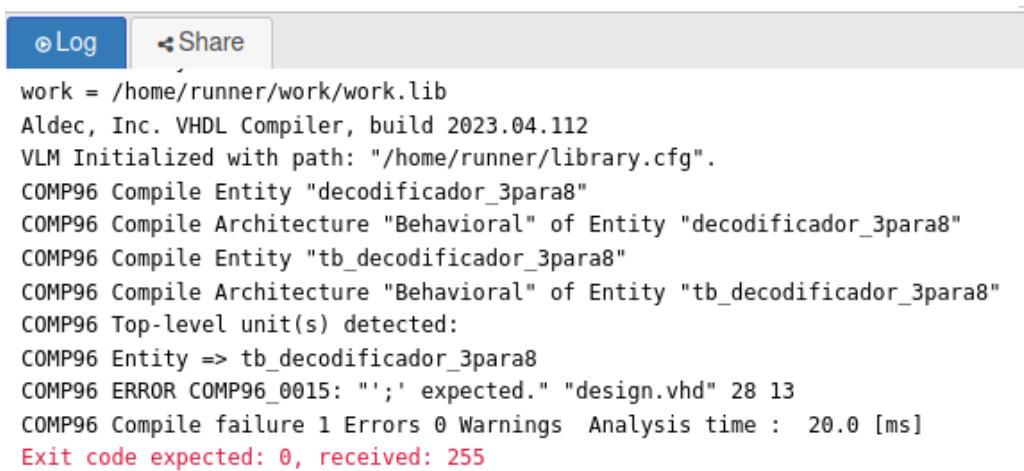

15. Ao compilar os arquivos VHDL, o EDA *Playground* verifica a sintaxe do código e gera mensagens de erro que auxiliam na localização e correção de falhas. Apague ";" no final da linha 27 do design.vhd na janela direita

```

25      when "110" => saida <= "10111111";

26      when "111" => saida <= "01111111";

27      when others => saida <= "11111111";

28  end case;

29 else

```

Execute a síntese do código ("Run") e observe as mensagens geradas na aba "Log". Você consegue identificar a fonte do erro através do *log* do sintetizador?

The screenshot shows the Aldec VHDL Compiler log window. The tabs at the top are 'Log' (which is selected) and 'Share'. The log output is as follows:

```

work = /home/runner/work/work.lib

Aldec, Inc. VHDL Compiler, build 2023.04.112

VLM Initialized with path: "/home/runner/library.cfg".

COMP96 Compile Entity "decodificador_3para8"

COMP96 Compile Architecture "Behavioral" of Entity "decodificador_3para8"

COMP96 Compile Entity "tb_decodificador_3para8"

COMP96 Compile Architecture "Behavioral" of Entity "tb_decodificador_3para8"

COMP96 Top-level unit(s) detected:

COMP96 Entity => tb_decodificador_3para8

COMP96 ERROR COMP96_0015: ';' expected. "design.vhd" 28 13

COMP96 Compile failure 1 Errors 0 Warnings Analysis time : 20.0 [ms]

Exit code expected: 0, received: 255

```

## Projeto 2: Descrevendo e simulando um circuito sequencial

Diferentemente das linguagens de programação tradicionais, onde a execução segue uma ordem sequencial de comandos, em uma linguagem de descrição de *hardware*, as instruções não são executadas em sequência, mas representam estruturas que operam simultaneamente. No projeto *decodificador\_3para8*, cada declaração no código VHDL descreve um componente ou comportamento que será sintetizado como parte de um sistema de *hardware* operando em paralelo. Assim, a síntese do sistema a partir do código VHDL gera uma arquitetura composta por módulos paralelos e interconectados, não uma linha de execução sequencial.

Essa forma de pensar é essencial para compreender o **círcuito combinacional**, onde as saídas dependem exclusivamente do estado atual das entradas. No entanto, o mundo digital que nos cerca, como processadores, controladores, memórias e interfaces, vai muito além disso. Esses sistemas não apenas reagem a sinais de entrada, mas evoluem ao longo do tempo, armazenam estados e tomam decisões com base em eventos passados. Para isso, eles dependem de uma estrutura fundamental: o circuito sequencial. Diante dessa transição do comportamento puramente combinacional para o comportamento com memória e evolução temporal, surge um novo desafio: como usar HDL para descrever e sintetizar circuitos sequenciais, que respondem não só às entradas atuais, mas também ao histórico de sinais, controlados por um sinal de relógio (*clock*)? A partir do que aprendemos sobre circuitos combinacionais,

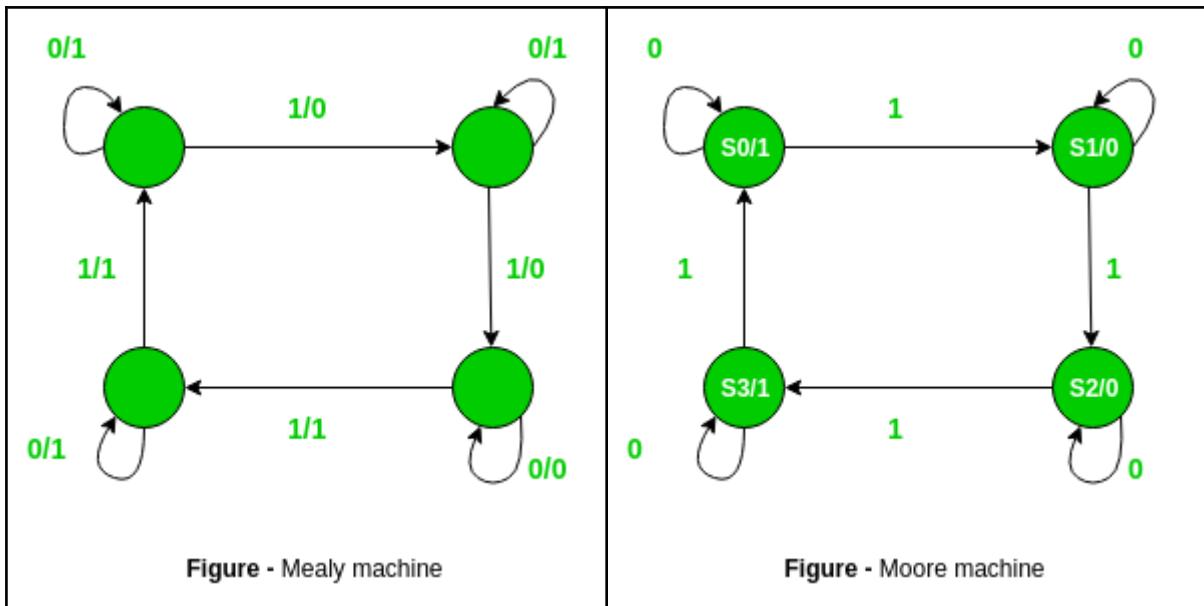

projetamos agora, em VHDL, um circuito sequencial simples: um **detector de sequência de 6 bits**, implementado como uma máquina de estados finitos (FSM).

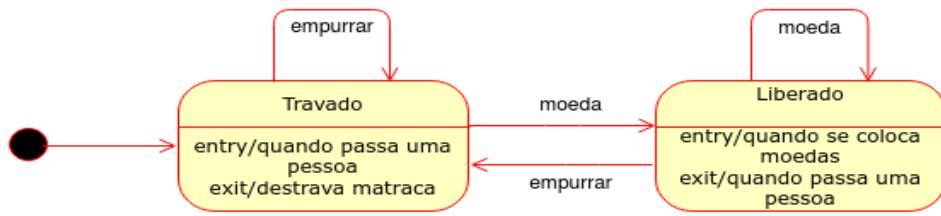

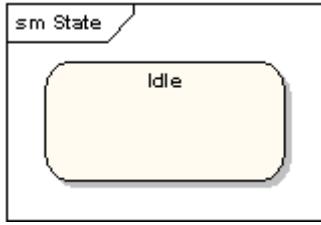

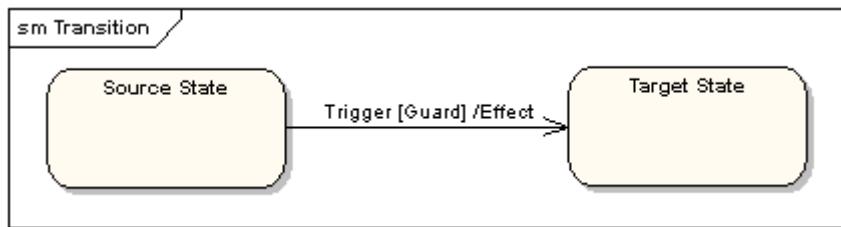

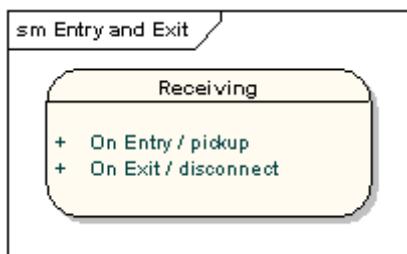

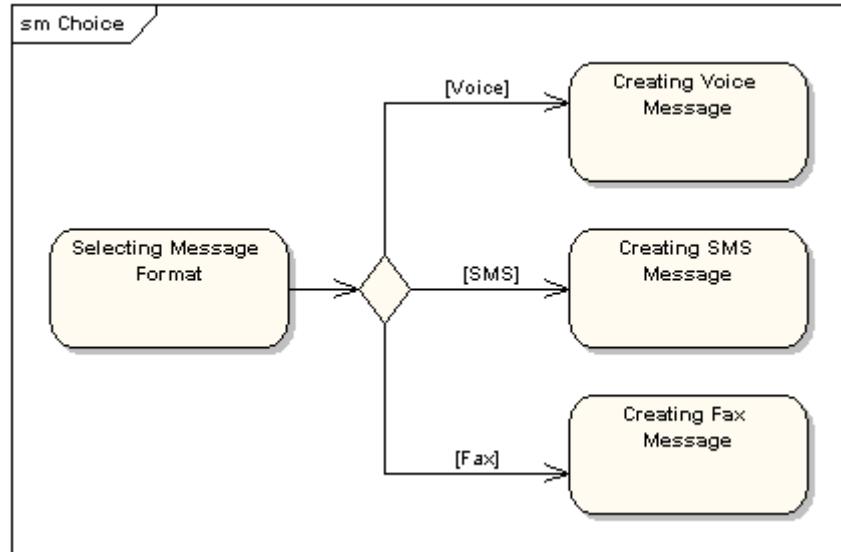

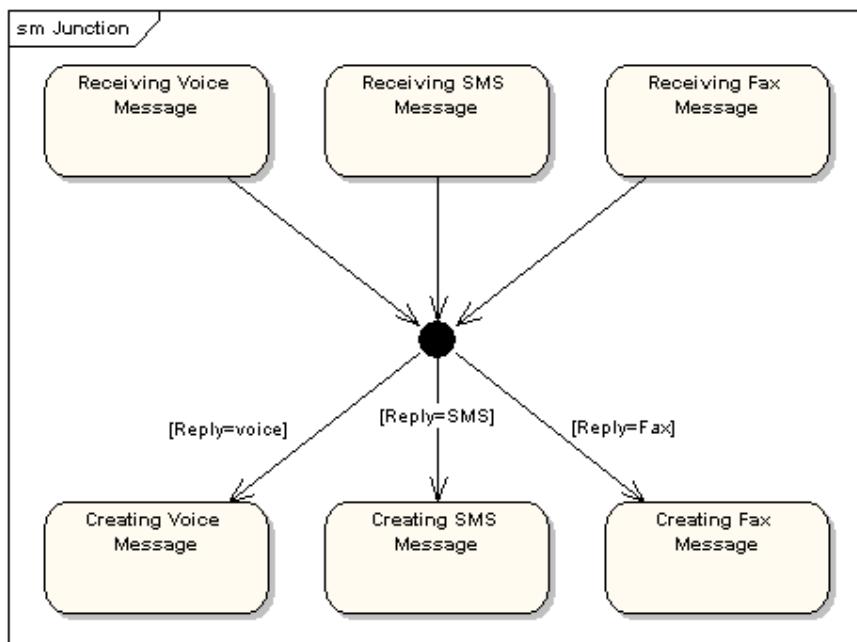

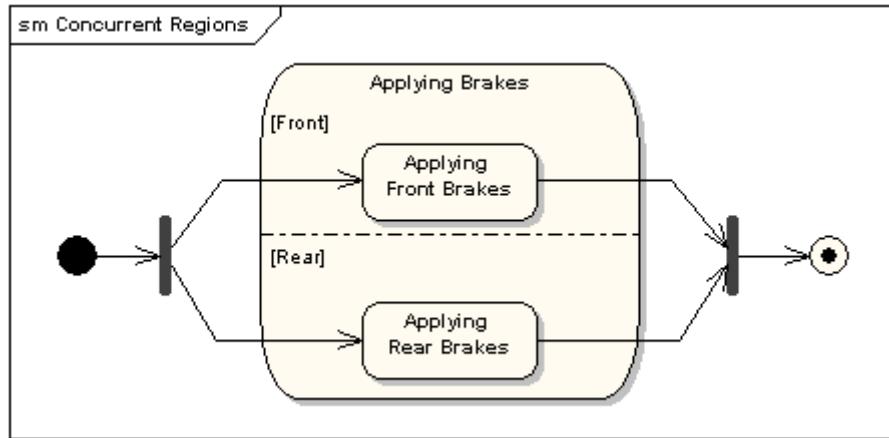

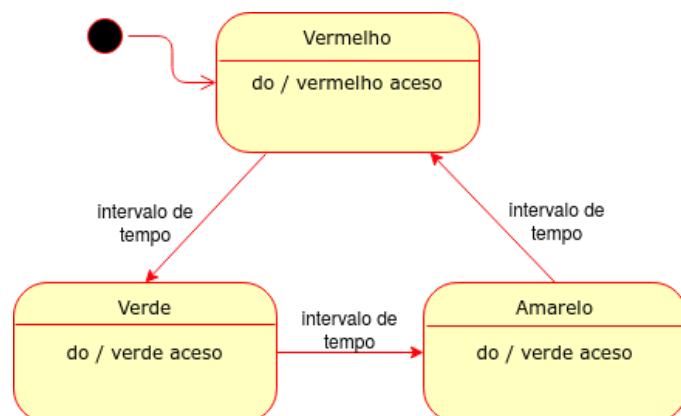

Para lidar com essa nova complexidade de forma estruturada e compreensível, podemos recorrer a uma abordagem complementar de modelagem. A combinação de UML (do inglês *Unified Modeling Language*) e VHDL nos permite modelar e implementar máquinas de estados em circuitos físicos reais. Por meio da UML, criamos diagramas de máquina de estados que representam de forma concisa e intuitiva os diferentes estados do sistema e suas transições, facilitando a compreensão e a comunicação entre os membros da equipe de projeto. Uma vez que a máquina de estados está claramente definida, o VHDL entra em cena para descrever a lógica do circuito de maneira estruturada e sintetizável. O próprio VHDL oferece recursos nativos para a implementação de máquinas de estados, como a possibilidade de descrever estados, transições e comportamentos associados em processos sensíveis ao *clock*, o que facilita a tradução direta de modelos abstratos em circuitos digitais confiáveis. Assim, conseguimos criar uma descrição precisa do sistema, viabilizando sua construção física sem a necessidade de lidar diretamente com os detalhes elétricos de baixo nível.

O aplicativo draw.io, agora conhecido como [diagrams.net](#), é uma ferramenta *online* gratuita para criação de diagramas e gráficos. Ela oferece um editor gráfico intuitivo que permite a criação de uma ampla gama de diagramas, como fluxogramas, diagramas de rede, organogramas, diagramas de processos, além de ser frequentemente usada para criar diagramas da UML. Embora o draw.io ofereça suporte para muitos tipos de diagramas UML, sua compatibilidade não é 100%, o que significa que alguns elementos e padrões da UML podem não ser totalmente precisos ou disponíveis. O aplicativo é baseado em navegador e também permite o salvamento e compartilhamento de diagramas em várias plataformas, como *Google Drive*, *OneDrive* e localmente.

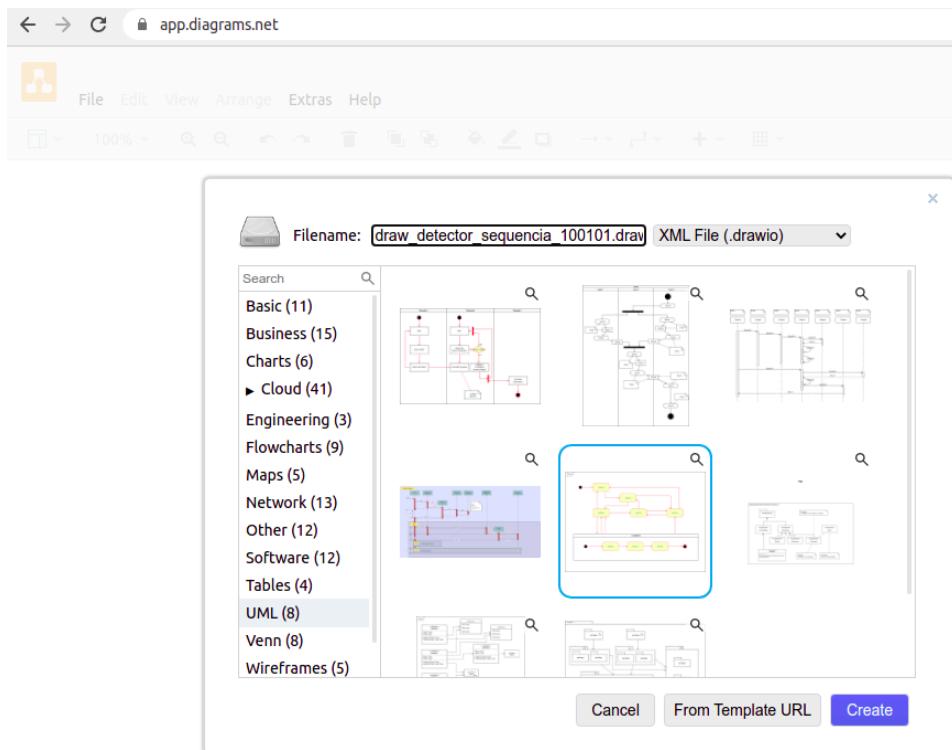

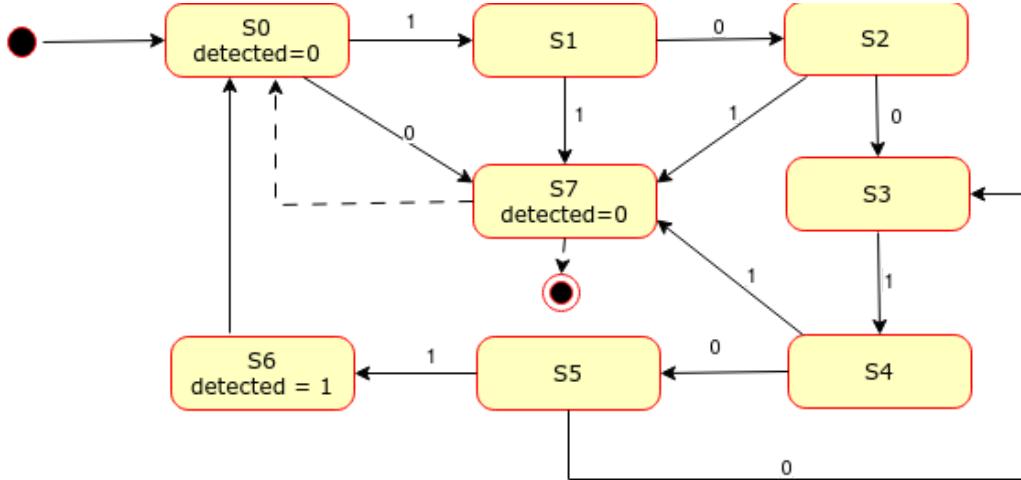

Para ilustrar a aplicação combinada de UML e VHDL no desenvolvimento de um circuito sequencial, vamos representar primeiro uma **máquina de estados** correspondente ao **detector de sequência de 6 bits "100101"**. Utilizamos o draw.io, acessando o [link](#) para iniciar seu diagrama e escolher onde salvá-lo.

Ao escolher um dispositivo de armazenamento, novos menus *popup* aparecerão para você atribuir um nome ao projeto (por exemplo, `draw_detector_sequencia_100101.drawio`), especificar o local de armazenamento, criar um arquivo de armazenamento no local selecionado (por exemplo, `draw_detector_sequencia_100101.drawio`), e se quiser, escolher um *template* para o seu projeto. Neste caso, foi selecionado um *template* de diagrama de máquina de estados da UML para reaproveitar os componentes já incluídos.

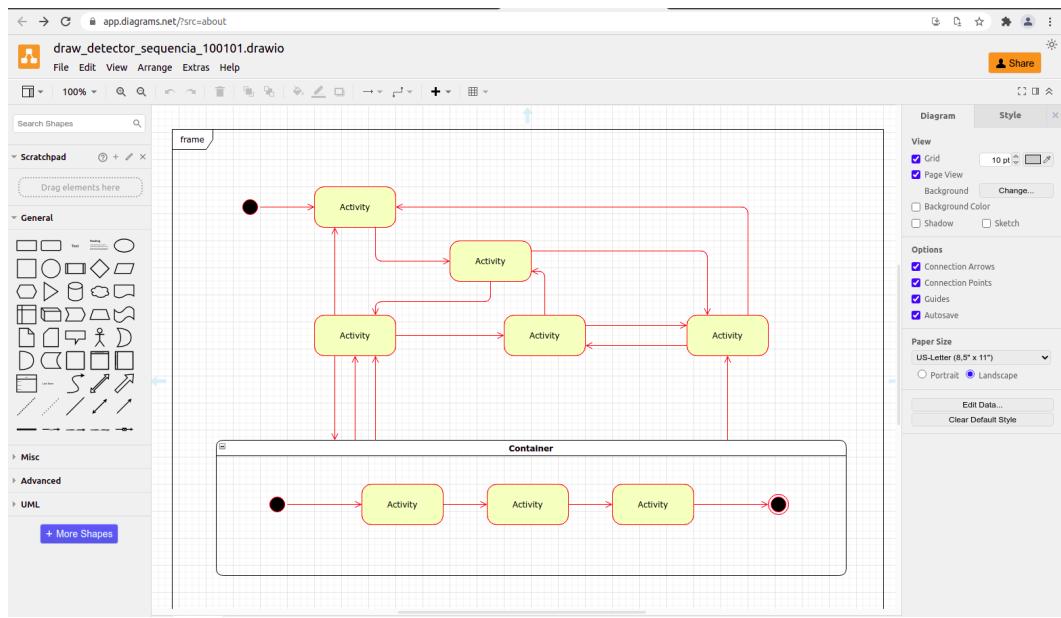

Abre-se então uma nova tela com o *template* selecionado no meio da tela. No centro da interface está o editor gráfico, onde o diagrama é desenhado e editado. À esquerda, há uma barra de ferramentas que contém uma variedade de elementos gráficos que podem ser arrastados para o editor. Esses elementos incluem formas básicas (como retângulos, círculos, etc.), conexões, ícones e outros objetos que podem ser inseridos no diagrama com um simples clique ou arraste. À direita, a aba permite configurar a aparência e o estilo dos elementos gráficos selecionados. É possível ajustar propriedades como cor, tamanho, fonte, borda e outros aspectos visuais de cada objeto inserido, além de realizar configurações mais avançadas.

Observe que o diagrama está “embutido” em um `frame`. Para editá-lo, clique uma vez sobre o `frame` e, em seguida, pressione o botão direito do *mouse* para abrir o menu de contexto. Selecione a opção “Delete” para liberar os elementos gráficos e permitir a edição.

Utilizando os recursos disponíveis no editor, foi criado o diagrama de máquina de estados do projeto. Para salvar o arquivo, abra o menu *dropdown* “File” na barra superior. Ao selecionar a opção “Save As...”, o sistema permitirá que você escolha o local para salvar o arquivo. Já ao escolher “Export as...”, serão apresentadas diferentes opções de formatos para exportação.

Em seguida, é apresentado um menu de opções para a imagem a ser salva.

Segue abaixo o diagrama de máquina de estados implementado no projeto `detector_sequencia_100101`, que apresenta duas transições indefinidas para o estado S7. As linhas pontilhadas indicam as possíveis alternativas de transição que o sistema pode seguir ao estar no estado S7.

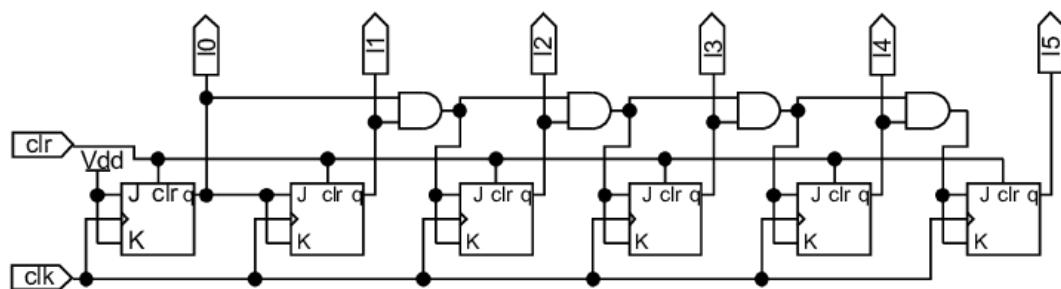

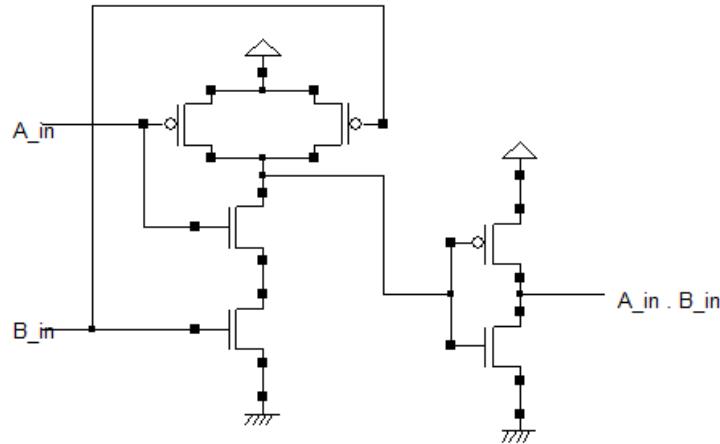

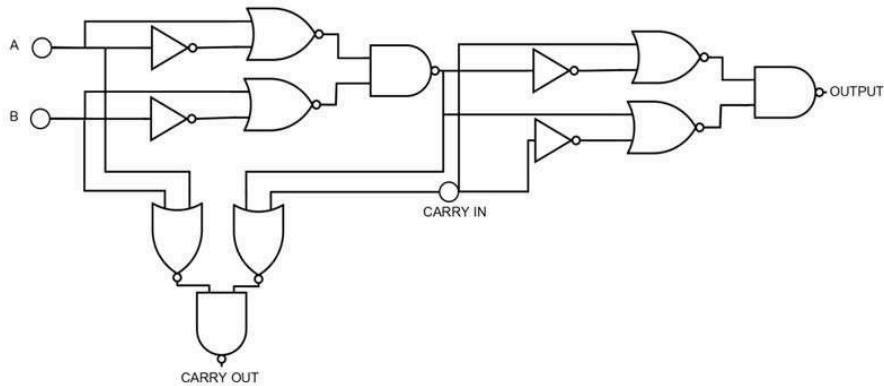

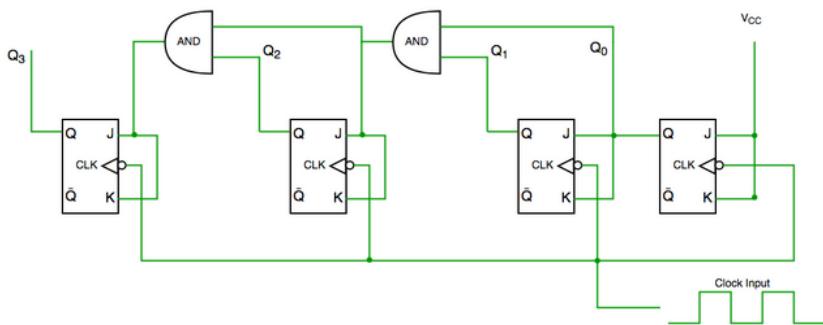

Vamos transformar o nosso diagrama de máquina de estados em um circuito sequencial físico de detecção de sequência de *bits*. Para isso, a maneira mais clara e direta é através de um esquemático gráfico, que ilustra como o diagrama de estados modelado pode ser realizado em *hardware*. O diagrama a seguir ilustra a implementação desse detector, utilizando um total de 12 componentes discretos: seis *flip-flops* JK e seis portas AND. A cada pulso de *clock*, um novo *bit* de entrada é inserido no primeiro *flip-flop*, enquanto os *bits* anteriores se deslocam para os *flip-flops* subsequentes. Dessa forma, os seis *flip-flops* armazenam continuamente os últimos seis *bits* recebidos. Um bloco de lógica combinacional, então, compara o conteúdo desses *flip-flops* com a sequência desejada ("100101") e ativa uma saída (*detect* = '1') quando a correspondência é encontrada.

Fonte: [ResearchGate](#)

Alternativamente, podemos sintetizar o mesmo diagrama de estados em um PLD, como uma FPGA, utilizando um Ambiente de Desenvolvimento Integrado (em inglês, *Integrated Development Environment*) como o [Intel Quartus Prime](#). Esses ambientes são projetados para projetar, simular, sintetizar e implementar circuitos lógicos em PLDs. O Quartus Prime suporta tanto diagramas esquemáticos quanto as linguagens de descrição de *hardware* mais populares, Verilog e VHDL. Isso significa que ele é capaz de traduzir tanto representações gráficas quanto descrições textuais em circuitos lógicos prontos para serem implementados em um PLD. Por exemplo, o esquemático do detector que acabamos de ver é suficiente para que o IDE gere o circuito necessário na FPGA.

Agora, vamos explorar a descrição textual desse detector sem o sinal `clr`, mas utilizando a linguagem VHDL, que também pode ser implementada em uma FPGA através de um IDE.

1. Crie um novo projeto no EDA Playground usando o botão “New”. Configure o projeto como no projeto anterior, atribuindo à “Top entity” o nome `tb_detector_sequencia_100101`.

2. Na janela à direita, escreva a descrição do detector da sequência de *bits* "100101", que é uma tradução direta e textual do que está representado graficamente no diagrama de estados.

-- Code your design here

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity detector_sequencia_100101 is

Port (

clk : in STD_LOGIC; -- Sinal de clock

bit_in : in STD_LOGIC; -- Entrada do bit a ser verificado

detected : out STD_LOGIC -- Saída que vai para 1 durante um ciclo de clock quando a

sequência "100101" é detectada

);

end detector_sequencia_100101;

```

```

architecture Behavioral of detector_sequencia_100101 is

```

```

-- Definindo os estados do detector

type state_type is (S0, S1, S2, S3, S4, S5, S6);

signal state : state_type := S0;

begin

process(clk)

begin

if rising_edge(clk) then

case state is

when S0 =>

if bit_in = '1' then

state <= S1;

end if;

detected <= '0';

when S1 =>

if bit_in = '0' then

state <= S2;

else

state <= S1;

end if;

```

```

detected <= '0';

when S2 =>

if bit_in = '0' then

state <= S3;

else

state <= S1;

end if;

detected <= '0';

when S3 =>

if bit_in = '1' then

state <= S4;

else

state <= S0;

end if;

detected <= '0';

when S4 =>

if bit_in = '0' then

state <= S5;

else

state <= S1;

end if;

detected <= '0';

when S5 =>

if bit_in = '1' then

state <= S6;

detected <= '1'; -- Sequência "100101" detectada, saída em 1 por um ciclo

else

state <= S3;

detected <= '0';

end if;

when S6 =>

detected <= '0'; -- Reseta a saída após um ciclo

state <= S0; -- Reinicia a sequência

end case;

end if;

end process;

end Behavioral;

```

Essencialmente, cada estado ( $S_i$ ) do diagrama corresponde a um *flip-flop* JK na nossa implementação com componentes discretos. A lógica AND, realizada pelas portas lógicas, é descrita usando a declaração sequencial `if ... then ... end if` em VHDL. As transições entre os estados são coordenadas pela borda de subida do sinal de relógio (`clk`), o que é expresso pela condicional `if rising_edge(clk) then ... end if`. É essa

lógica sequencial sensível à borda do *clock* que é responsável pela inferência de *flip-flops* na síntese do circuito pelo sintetizador VHDL. Dentro da declaração sequencial *case*, cada transição de estado do *flip-flop* é detalhada em um ramo específico *when*, que, por sua vez, contém o bloco combinacional da porta lógica correspondente.

3. Na janela à **esquerda**, adicione um código da *testbench*:

-- Code your testbench here

library IEEE;

use IEEE.STD\_LOGIC\_1164.ALL;

```

entity tb_detector_sequencia_100101 is

end tb_detector_sequencia_100101;

```

```

architecture Behavioral of tb_detector_sequencia_100101 is

```

```

signal clk : STD_LOGIC := '0';

```

```

signal bit_in : STD_LOGIC := '0';

```

```

signal detected : STD_LOGIC;

```

-- Instancia o módulo do detector

```

component detector_sequencia_100101

```

```

Port (

```

```

clk : in STD_LOGIC;

```

```

bit_in : in STD_LOGIC;

```

```

detected : out STD_LOGIC

```

```

);

```

```

end component;

```

```

begin

```

```

uut: detector_sequencia_100101 Port map (

```

```

clk => clk,

```

```

bit_in => bit_in,

```

```

detected => detected

```

```

);

```

-- Gera o clock de 10ns

```

clk_process : process

```

```

begin

```

```

clk <= '0';

```

```

wait for 5 ns;

```

```

clk <= '1';

```

```

wait for 5 ns;

```

```

end process;

```

-- Estímulo de teste

```

process

begin

-- Aplica a sequência "100101" com outros bits entre as tentativas

wait for 10 ns; bit_in <= '1';

wait for 10 ns; bit_in <= '0';

wait for 10 ns; bit_in <= '0';

wait for 10 ns; bit_in <= '1';

wait for 10 ns; bit_in <= '0';

wait for 10 ns; bit_in <= '1'; -- Sequência "100101" detectada, 'detected' vai a 1 por um

ciclo

wait for 10 ns; bit_in <= '0'; -- Reinicia a sequência

wait for 10 ns; bit_in <= '1';

wait for 10 ns; bit_in <= '0';

wait for 10 ns; bit_in <= '0';

wait for 10 ns; bit_in <= '1';

wait for 10 ns; bit_in <= '0';

wait for 10 ns; bit_in <= '1'; -- Sequência "100101" detectada novamente, 'detected' vai a

1 por um ciclo

-- Finaliza a simulação

wait for 1000 ns;

wait;

end process;

end Behavioral;

```

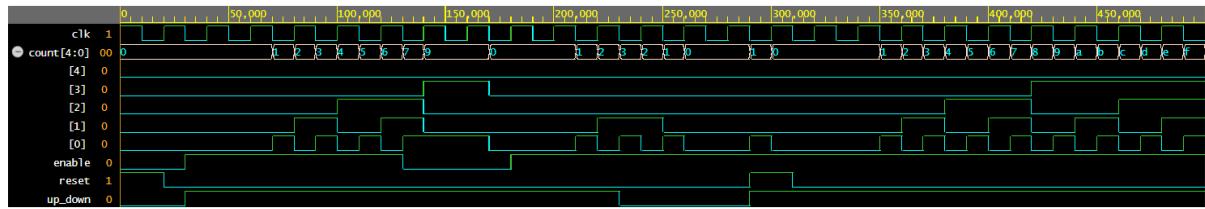

4. Ajuste o tempo de execução para 200ns e renomeie a “Top entity” para `tb_detector_sequencia_100101`. Em seguida, execute a simulação, analise as formas de onda e responda:

- Os sinais de saída reagem imediatamente às entradas, desconsiderando os atrasos de propagação?

- Em quais instantes o sinal de saída muda de estado?

- Como o comportamento do circuito está vinculado ao sinal de clock?

- É possível observar como os estados internos se modificam ao longo do tempo?

Agora, compare esse comportamento com o circuito combinacional `decodificador_3para8`. No circuito sequencial, o tempo, marcado pelo `clk`, tem um papel essencial na evolução do sistema. Isso nos leva a uma reflexão: o tempo pode afetar a lógica de um circuito? Em outras palavras, será que um mesmo circuito pode apresentar um comportamento logicamente diferente quando consideramos apenas relações puras entre sinais, em contraste com quando introduzimos a dimensão temporal e estados internos?

5. Os elementos em uma descrição VHDL que caracterizam um circuito sequencial, em contraste com um combinacional, são aqueles que implicam a existência de memória (estado) e sincronismo (*clock*). Ao comparar a descrição do projeto combinacional `decodificador_3para8` com a do `detector_sequencia_100101`, notamos que, embora ambos empreguem o bloco `process` com uma lista de sinais de sensibilidade, **três elementos adicionais** são cruciais para caracterizar o `detector_sequencia_100101` como um circuito sequencial. Quais são esses três elementos, excluindo a criação de um tipo personalizado para os identificadores de estado?

6. Quais alterações você faria na descrição `detector_sequencia_100101.vhd` para que a sequência seja reiniciada no estado S0 sempre que um dígito que não faça parte da sequência for detectado?

7. Qual valor você configuraria no campo de “Run Time” do EDA *Playground* para visualizar a simulação completa das duas sequências de *bits*?

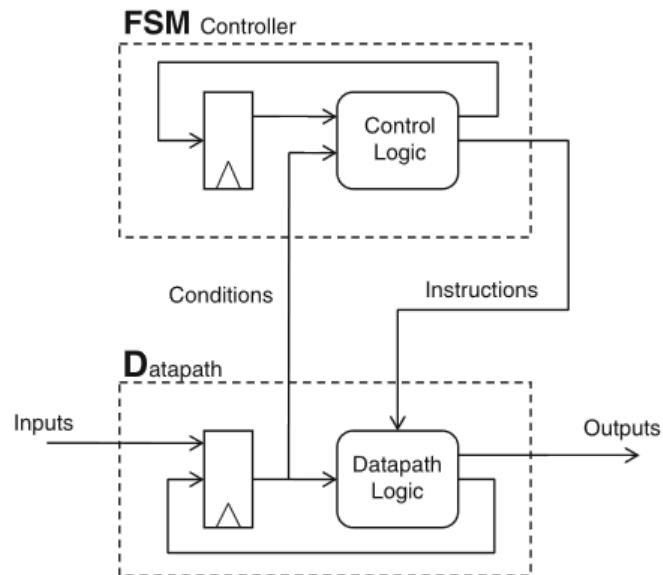

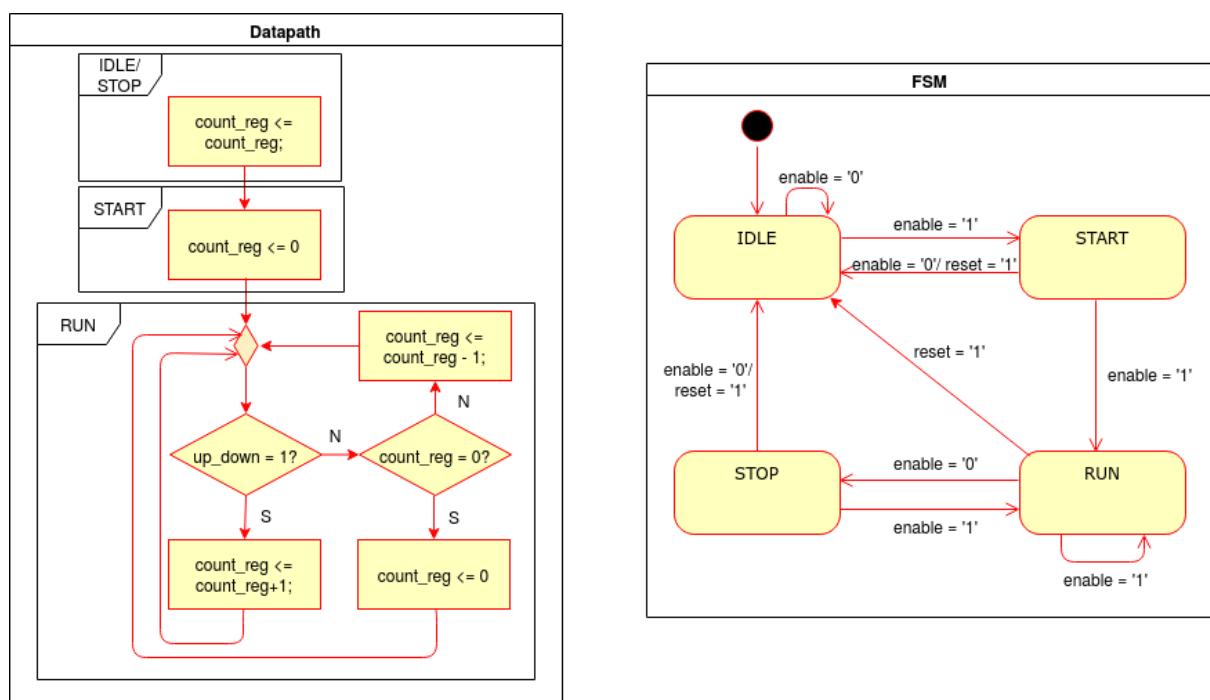

### Projeto 3: Criando um controlador na arquitetura FSMD

No Roteiro 10, exploramos a configuração e operação do módulo SPI integrado ao microcontrolador STM32H7A3. Agora, imagine como seria projetar um módulo SPI semelhante em uma FPGA, modelando-o em nível de transferência de registradores (em inglês, *Register Transfer Level*) ou em nível de máquina de estados finitos com caminho de dados (em inglês, *Finite State Machine with Datapath – FSMD*), usando a linguagem VHDL. Desafie-se a dar esse próximo passo: como criar um módulo SPI capaz de converter dados paralelos do núcleo em sinais seriais síncronos, conforme o [protocolo SPI](#)? Para isso, vamos aproveitar os recursos da FPGA e a flexibilidade da linguagem VHDL, que permite descrever o sistema em diferentes níveis, adaptando a complexidade do modelo às necessidades do projeto.

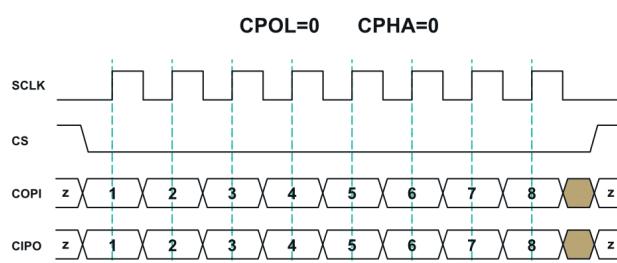

**Sem perda de generalidade, vamos assumir que o nosso controlador SPI será apenas *master* e irá operar apenas no modo 0 (CPOL = CPHA = 0), transmitindo o *bit* mais significativo primeiro. O sinal \CS não é gerado pelo controlador, ficando a cargo de uma GPIO do microcontrolador. A taxa de transmissão de dados será dada pelo *clock* fornecido ao controlador (o prescaler não será implementado aqui), sendo que a quantidade de *bits* por segundo será metade da frequência do *clock*.**

Note que com algumas modificações este controlador pode ter mais flexibilidade, por exemplo operando em outros modos. A taxa de transmissão depende apenas de um *prescaler* facilmente implementado. Este controlador pode ser facilmente incorporado a um microcontrolador, e geralmente é dessa forma que se projetam os módulos internos de microcontroladores, como o que foi usado nesta disciplina.

Neste projeto [MasterSPI](#), vocês serão desafiados a analisar os resultados gerados pela solução proposta e validá-los com os resultados esperados. O foco inicial será entender os resultados práticos da implementação, ajudando a desenvolver uma visão crítica sobre o funcionamento do sistema. No entanto, é essencial que complementem essa análise com a leitura detalhada da última seção “Projeto de um Processador Dedicado”. Essa seção fornece o embasamento teórico e a fundamentação técnica que explicam como o projeto foi desenvolvido até a etapa de descrição do circuito em VHDL. Compreender esse desenvolvimento é importante para entender os princípios que guiaram a criação da solução, e assim, proporcionar uma visão mais profunda sobre a construção de sistemas digitais em FPGA.

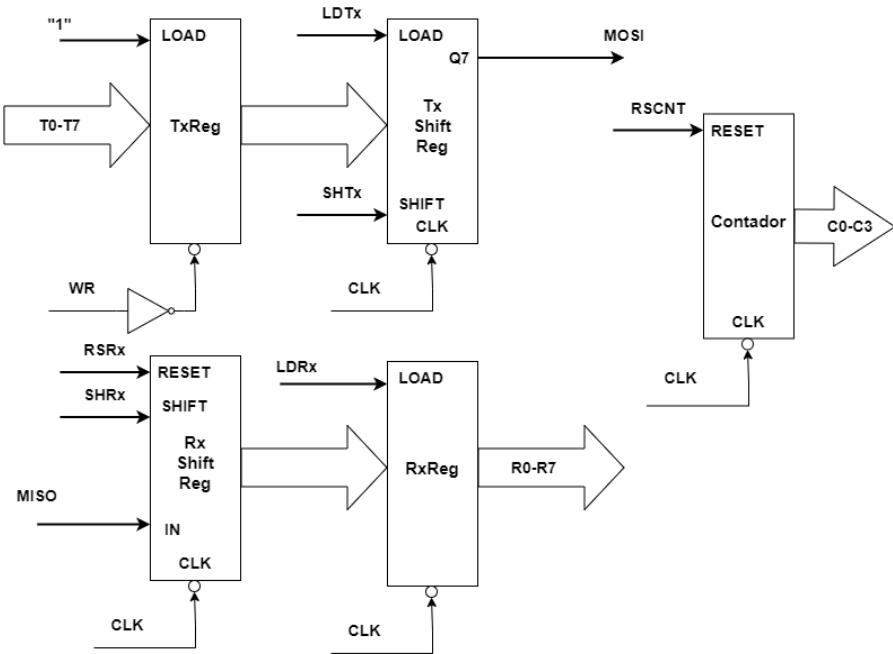

1. Inicialmente, vamos definir os sinais externos ao controlador SPI. Temos uma interface com o microcontrolador e a interface no padrão SPI. Pelo lado da interface com o microcontrolador, o controlador SPI terá uma entrada de dados de 8 bits para transmissão TxD (**T7-T0**) e uma saída de dados de 8 bits para o dado recebido RxD (**R7-R0**). Além disso, terá um sinal de entrada **WR** (*WRite*), cuja borda de subida inicia a transmissão do dado, e um sinal de saída **TCPLT** (*Transfer Complete*), gerado pela FSM, que vai para 1 quando a transmissão / recepção de byte acabou, indo para 0 no início da nova transferência. Há ainda uma entrada *clock* que determina o sincronismo dos elementos. Pelo lado da interface SPI, temos os sinais de dados **MOSI** e **MISO**, ligados diretamente ao *datapath*, e o sinal **SCK**, gerado pela FSM.

```

220

221 -- ENTIDADE SUPERIOR QUE ENGLOBA TODAS AS OUTRAS

222 library IEEE;

223 use IEEE.STD_LOGIC_1164.ALL;

224

225 entity MasterSPI is

226   Port (

227     clk : in STD_LOGIC;

228     WR : in STD_LOGIC;

229     MISO : in STD_LOGIC;

230     TxD : in STD_LOGIC_VECTOR (7 downto 0);

231     RxD : out STD_LOGIC_VECTOR (7 downto 0);

232     TCPLT : out STD_LOGIC;

233     MOSI : out STD_LOGIC;

234     SCK : out STD_LOGIC

235   );

236 end entity MasterSPI;

237

```

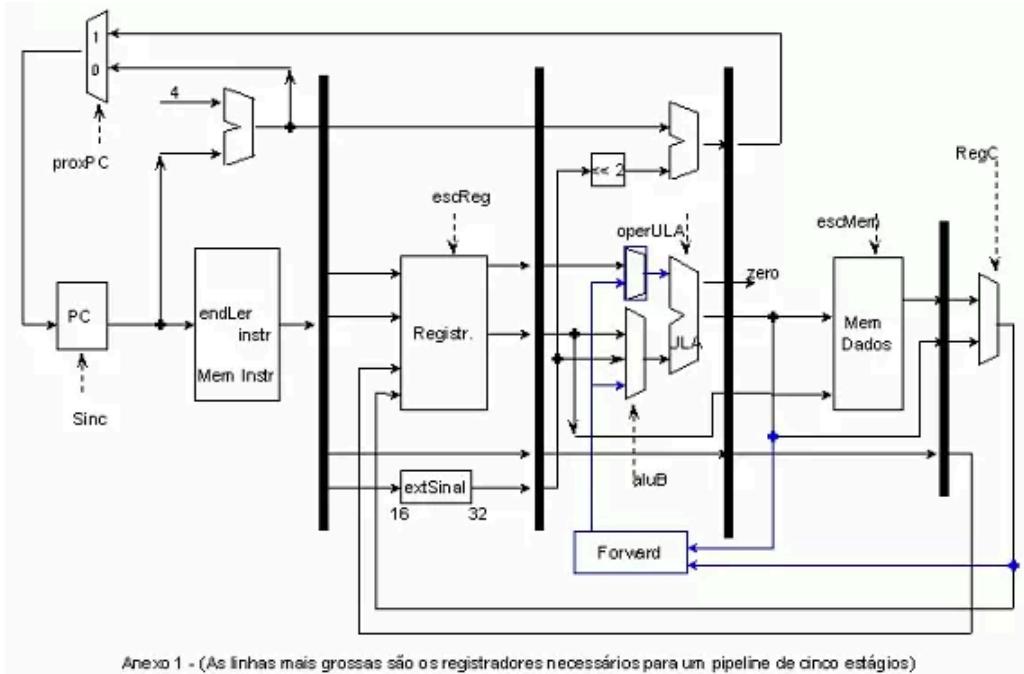

2. A entidade principal MasterSPI interconecta cinco entidades menores: TxReg, TxShiftReg, RxShiftReg, RxReg e Contador. Essa conexão revela o fluxo de dados entre elas, por meio de uma descrição estrutural de blocos que contêm registradores e lógica combinacional. Essa abordagem é uma característica essencial do nível de abstração RTL, onde o **caminho de dados** (em inglês, *datapath*) é explicitamente implementado. É

importante notar que os sinais MISO e MOSI, que fazem parte da interface física SPI, estão incluídos diretamente nesse fluxo do *datapath*.

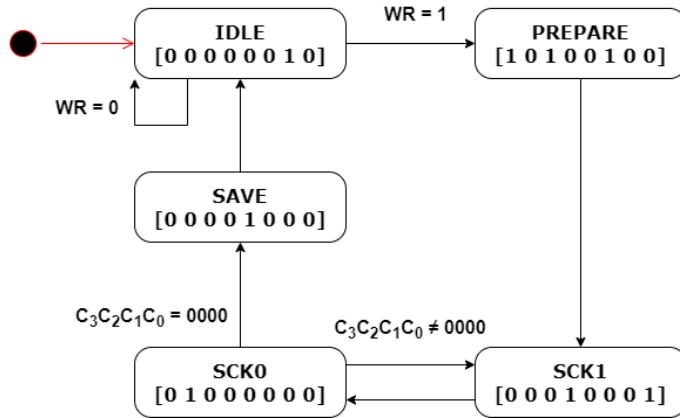

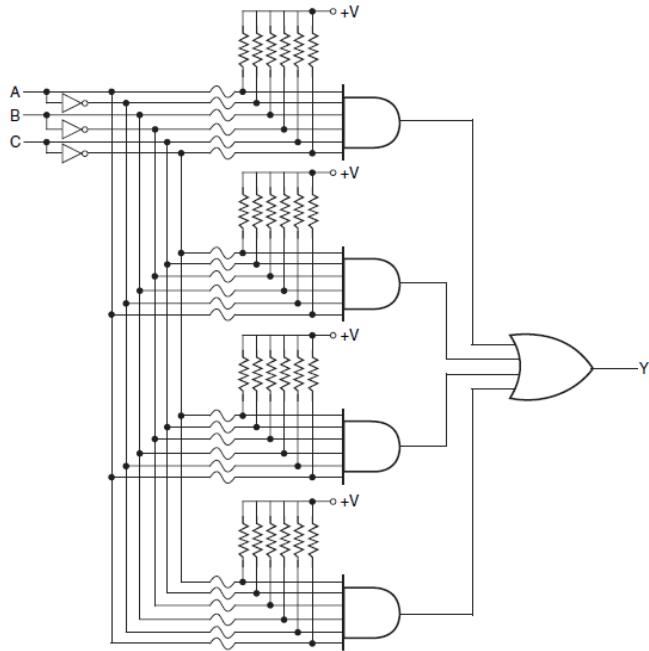

3. Há uma sexta entidade, a *StateMachine*, que atua como a unidade de controle principal. Ela é uma **máquina de estados finitos** (em inglês, *Finite State Machine*) pura, gerenciando as transições entre seus dois sinais de estado, *state* e *next\_state*, através de uma lógica de transição interna e as entradas *WR* e *Z*. Essa *StateMachine* gera um vetor de controle de 8 bits (*output*), que é mapeado para o sinal *Ctrl\_internal* da entidade *MasterSPI*. Os bits desse vetor controlam diretamente todos os elementos do *datapath* previamente especificados no *MasterSPI*. Eles são: *LDTx*, *SHTx*, *RSRx*, *SHRx*, *LDRx* e *RSCNT*. Além desses, a FSM também é responsável por gerar os sinais externos *TCPLT* (do inglês *Transfer Complete*) e *SCK* (do inglês *Serial Clock*). Esses sinais estão organizados em um vetor com 8 sinais na seguinte ordem (do bit mais significativo para o menos significativo) na descrição:

**[LDTx, SHTx, RSRx, SHRx, LDRx, RSCNT, TCPLT, SCK]**

A figura abaixo mostra o diagrama de estados da FSM implementada na entidade *StateMachine* em VHDL.

Saídas: [LDTx, SHTx, RSRx, SHRx, LDRx, RSCNT, TCPLT, SCK]

Todos os elementos do *datapath* são síncronos, ou seja, os sinais de controle (LDRx, LDTx, SHTx, SHRx, RSRx, RSCNT) são processados na borda de **descida** do *clock*. Os sinais de controle são ativos em nível alto. A FSM, por sua vez, usa *flip-flops* sensíveis à borda de **subida** do *clock*. Assim, a cada ciclo de *clock*, primeiro a FSM atualiza o estado (borda de subida) e depois o *datapath* processa os sinais de controle (borda de descida).

4. Pelo lado da transmissão, temos no caminho de dados um registrador comum de 8 bits (**TxReg**), que recebe o dado a ser transmitido. Ele é carregado na borda de **subida** de *clock*, sendo que o *clock* deste registrador é ligado ao sinal **WR** (a única exceção no *datapath*, todos os outros elementos são ligados ao *clock* do controlador, respondendo a borda de descida), sendo sua entrada **LOAD** mantida em 1. Quando **WR** vai a 1, o dado a ser transmitido é imediatamente carregado no registrador de entrada, e na próxima borda de subida do *clock* o estado é atualizado. Se este registrador usasse o mesmo *clock* dos demais, mesmo que respondendo na borda de subida, seria necessário um estado adicional para concluir a carga do dado no registrador. Esta é uma estratégia usada para reduzir o número de estados necessários, porém deve ser usada com cautela.

Temos ainda um *shift register* do tipo paralelo-serial (**TxShiftReg**), que recebe o dado de transmissão paralelo e o serializa, com a carga do dado paralelo sendo comandada pelo sinal interno **LDTx** e o deslocamento de um *bit* à esquerda sob comando do sinal interno **SHTx**. Sua saída Q<sub>7</sub> (*bit* mais significativo) fornece o sinal **MOSI** da interface SPI.

5. Pelo lado da recepção, temos no caminho de dados inicialmente um *shift register* do tipo serial-paralelo (**RxShiftReg**), cuja entrada serial é o sinal **MISO** da interface SPI. Seu *reset* é controlado pelo sinal interno **RSRx** e a carga do *bit* de entrada para a saída Q<sub>0</sub> e deslocamento dos demais *bits* à esquerda é controlada pelo sinal interno **SHRx**.

Temos ainda um registrador simples que armazena o resultado da transferência e conversão serial-paralelo (**RxReg**), cuja carga de dados é comandada pelo sinal interno **LDRx**. Note que quando falamos em comandos, estes só são executados na borda de descida do *clock* do sistema.

Finalmente, há um contador de 4 bits ( $C_0-C_3$ ) com seu *reset* controlado pelo sinal interno **RSCNT**. Este contador irá contar o número de *bits* transferidos.

6. Em relação à máquina de estados, segue-se uma descrição detalhada de cada estado:

- Estado **IDLE**: apenas o sinal **TCPLT** está ativo, e o controlador aguarda um sinal **WR** para iniciar a transferência bidirecional. Quando o sinal chega, muda para o estado **PREPARE**.

- Estado **PREPARE**: Ocorre uma preparação para o início da transferência. Na transição de **IDLE** para **PREPARE**, **TxReg** foi carregado com o dado a ser transmitido. Agora os sinais **LDTx**, **RSRx** e **RSCNT** são ativados, para carregar **TxShiftReg** com o dado a ser transmitido, zerar **RxShiftReg** e zerar o contador de *bits*. No próximo evento de *clock*, o estado muda para **SCK1**.

- Estado **SCK1**: Já temos o *bit* mais significativo da transmissão em **MOSI**, e, considerando que o sinal **\CS** estava ativo antes do início da transmissão, o *bit* mais significativo da recepção já foi colocado em **MISO**. É o momento de amostrar o primeiro *bit*, portanto o sinal **SCK** deve ter uma borda de subida. O sinal **SHRx** é ativado para carregar o primeiro *bit* da recepção em **RxShiftReg** e o sinal **SCK** vai para o valor 1. Note que na borda de descida, como o contador foi zerado mas o sinal de *reset* não está mais ativo, o contador passa a ter o valor 1. No próximo evento de *clock*, o estado muda para **SCK0**.

- Estado **SCK0**: É hora de mudar os *bits* em **MOSI** e **MISO**. O sinal **SHTx** é ativado, fazendo **TxShiftReg** deslocar um bit à esquerda, colocando o próximo *bit* em **MOSI**. O sinal **SCK** vai ao valor 0, sinalizando ao dispositivo *slave* que o *bit* em **MISO** deve ser trocado. Aqui existe uma decisão. Considere inicialmente que o valor do contador é 1. Se o valor do contador for diferente de zero, o próximo evento de *clock* muda o estado para **SCK1**. Aqui o contador é novamente incrementado, passando a ter o valor 2. Note que o valor do contador corresponde ao número de transições de **SCK** (tanto bordas de subida quanto de descida), e portanto para 8 *bits* devemos contar 16 transições.

- Os estados **SCK1** e **SCK0** se alternam enquanto o contador de transições avança até 15, que corresponde à última borda de subida (estado **SCK1**), e logo depois sofre um *overflow*, retornando ao valor zero na próxima transição (entrando no estado **SCK0**). Neste momento, como o valor do contador é igual a zero, a FSM, em vez de mudar para **SCK1** novamente, passa para o estado **SAVE**. Note que na primeira vez que a FSM entra no estado **SCK0**, o valor do contador já é 1, mudando para 2 antes da próxima borda de subida do *clock*, quando ocorre o teste de condição. Assim, apenas quando as 16 transições de **SCK** terminarem, o contador terá novamente o valor zero.

- Estado **SAVE**: Carrega o conjunto de *bits* recebidos em **MISO** no registrador **RxReg**, ativando o sinal **LDRx**. Depois, retorna a **IDLE**, colocando **TCPLT** em 1 novamente e completando a transferência

7. Acesse o [link do EDA Playground](#), onde foi criado o projeto completo do controlador, denominado **MasterSPI**. Use o botão *Copy* para criar uma cópia em sua própria conta, e

navegue até seu próprio *Playground*, abrindo a cópia local. A seguir, vamos analisar a estrutura do arquivo de *design* e do arquivo de *testbench*.

8. Inicialmente são definidas as bibliotecas. A definição vale para a primeira entidade encontrada. Quando há várias entidades em um mesmo arquivo, as bibliotecas usadas devem ser definidas para cada entidade, e assim pode-se perceber a redefinição das bibliotecas para cada entidade definida no arquivo.

```

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.ALL;

```

9. Logo depois aparece a definição de **TxReg**.

```

4 -- ELEMENTOS DO DATAPATH

5 -- Entidade TxReg

6 entity TxReg is

7     Port (

8         clk : in STD_LOGIC;

9         Tx_load : in STD_LOGIC;

10        Tx_in : in STD_LOGIC_VECTOR(7 downto 0);

11        Tx_out : out STD_LOGIC_VECTOR(7 downto 0);

12    );

13 end entity TxReg;

14

15 architecture Behavioral of TxReg is

16 begin

17     process(clk)

18     begin

19         if rising_edge(clk) then

20             if Tx_load = '1' then

21                 Tx_out <= Tx_in;

22             end if;

23         end if;

24     end process;

25 end architecture Behavioral;

```

A descrição está dividida em duas seções principais. A primeira, `entity TxReg`, define a interface externa do módulo, equivalente às portas de entrada e saída no esquemático apresentado no item 2. Isso inclui as entradas de dados `Tx_in` (correlacionadas a T0-T7 no esquemático), o sinal de clock `clk` (WR), o sinal de controle `Tx_load` (LOAD), e os sinais de saída `Tx_out`. Já a seção `architecture Behavioral` descreve o comportamento interno do `TxReg` como um registrador paralelo de 8 *bits* com carga síncrona habilitada.

Pela descrição, o comportamento é paralelo porque todos os 8 *bits*, representados pelo tipo de dados `STD_LOGIC_VECTOR(7 downto 0)`, são carregados e lidos simultaneamente através da atribuição `Tx_out <= Tx_in`. Ele é síncrono porque sua operação de carga é controlada pelo sinal de clock `clk`. Por fim, é habilitado porque o sinal de controle `Tx_load` (correspondente a LOAD no esquemático) determina quando essa carga pode ocorrer. Internamente, o sintetizador VHDL interpreta essa descrição para inferir oito *flip-flops D* (ou JK, dependendo das otimizações), um para cada *bit*, todos controlados pelo mesmo *clock* e sinal de habilitação de carga `Tx_load`.

De forma análoga, segue-se a descrição de RxReg com a mesma estrutura e lógica.

10. Em seguida, temos a descrição do registrador TxShiftReg que tem como interface externa 8 *bits* de entrada paralela D e 1 *bit* de saída Q7 (MOSI no esquemático do item 2), além do sinal de clk (CLK), sinal de carga LOAD (LDTx) e um sinal de habilitação do deslocamento dos *bits* SHIFT (SHTx).

```

52 -- Entidade TxShiftReg

53 library IEEE;

54 use IEEE.STD_LOGIC_1164.ALL;

55

56 entity TxShiftReg IS

57     Port (

58         clk    : IN STD_LOGIC;           -- Clock de entrada

59         LOAD   : IN STD_LOGIC;          -- Sinal de carga

60         SHIFT  : IN STD_LOGIC;          -- Sinal de deslocamento

61         D      : IN STD_LOGIC_VECTOR(7 downto 0); -- Dados de entrada paralelos

62         Q7    : OUT STD_LOGIC;          -- Bit de saída (Dados mais significativo)

63     );

64 end entity TxShiftReg;

65

66 architecture Behavioral of TxShiftReg is

67     -- Registrador interno de 8 bits iniciando com zero

68     signal reg : STD_LOGIC_VECTOR(7 downto 0):= (others => '0');

69 begin

70     process(clk)

71     begin

72         if falling_edge(clk) then

73             -- Carga paralela quando LOAD está em '1'

74             if LOAD = '1' then

75                 reg <= D;

76             -- Deslocamento à esquerda quando SHIFT está em '1'

77             elsif SHIFT = '1' then

78                 reg <= reg(6 downto 0) & '0'; -- Desloca à esquerda e insere '0' no bit menos

79                 significativo

80             end if;

81         end if;

82     end process;

83

84     -- Saída do bit mais significativo

85     Q7 <= reg(7);

86 end architecture Behavioral;

```

A seção architecture Behavioral detalha o comportamento de um registrador de deslocamento de 8 *bits*, operando de forma síncrona sob o controle de um sinal de *clock* clk. A funcionalidade central do circuito reside na lógica de controle de carga e deslocamento, implementada no processo sequencial process. O sinal reg, declarado como signal reg : STD\_LOGIC\_VECTOR(7 downto 0) := (others => '0'), atua como registrador de 8 *bits*, armazenando dados temporários. O sintetizador VHDL infere um registrador para reg ao detectar uma atribuição sequencial (reg <= D) controlada pelo teste de borda de *clock*, if falling\_edge(clk) then. Essa condição assegura que as operações sobre reg ocorram sincronizadamente na borda de descida do sinal de *clock*, garantindo o funcionamento correto do circuito síncrono.

Quando o sinal LOAD está ativo, o conteúdo do barramento de entrada D é carregado no reg de forma paralela. Se LOAD não estiver ativo e o sinal SHIFT estiver, o valor em reg é deslocado um *bit* para a esquerda (utilizando reg(6 downto 0)), com a inserção de um '0' no *bit* menos significativo (através da concatenação pela direita, &'0') para que o

sintetizador gere uma entrada válida de 8 *bits* para *reg* em cada pulso de *clock*. A utilização da declaração sequencial *if ... then ... elsif ...* estabelece uma prioridade implícita para o sintetizador VHDL: a carga paralela sempre acontece antes do deslocamento. Por fim, a saída *Q7* reflete o valor do *bit* mais significativo de *reg* após o próximo ciclo de *clock*.

11. Após a descrição do TxShiftReg, temos o RxShiftReg. Este componente possui como entradas os sinais *clk* (correspondente a CLK no esquemático do item 2), RESET (RSRx), SHIFT (SHRx), e D (MISO). Sua única saída é o sinal *Q* (R0-R7), um barramento de 8 *bits*.

```

87 -- Entidade RxShiftReg

88 library IEEE;

89 use IEEE.STD_LOGIC_1164.ALL;

90

91 entity RxShiftReg IS

92     Port (

93         clk : IN STD_LOGIC;           -- Clock de entrada

94         RESET : IN STD_LOGIC;        -- Sinal de reset

95         SHIFT : IN STD_LOGIC;        -- Sinal de deslocamento

96         D : IN STD_LOGIC;           -- Entrada serial

97         Q : OUT STD_LOGIC_VECTOR(7 downto 0) -- Saída paralela

98     );

99 end entity RxShiftReg;

100

101 architecture Behavioral of RxShiftReg is

102     signal reg : STD_LOGIC_VECTOR(7 downto 0); -- Registrador interno de 8 bits

103     begin

104         process(clk)

105             begin

106                 if falling_edge(clk) then

107                     -- Se RESET estiver ativo, zera o registrador

108                     if RESET = '1' then

109                         reg <= (others => '0');

110                     -- Realiza o deslocamento à esquerda se SHIFT estiver ativo

111                     elsif SHIFT = '1' then

112                         reg <= reg(6 downto 0) & D; -- Desloca à esquerda e insere o bit de entrada 'D'

113                         no bit menos significativo

114                         end if;

115                     end if;

116                 end process;

117                 -- Atribuição da saída paralela ao registrador interno

118                 Q <= reg;

119             end architecture Behavioral;

```

A seção *architecture Behavioral* descreve um registrador de deslocamento de 8 *bits*, operando de forma síncrona com o sinal de relógio. Sua funcionalidade principal é controlada pelos sinais de RESET e SHIFT. Como na descrição de TxShiftReg, o sinal *reg* atua como um registrador de 8 *bits*, armazenando dados temporários. Dentro do processo sensível ao *clk* (*process(clk)*), as operações ocorrem na borda de descida do *clock*. Se o sinal RESET estiver ativo ('1'), o registrador *reg* é zerado. Caso contrário, se SHIFT estiver ativo ('1'), o conteúdo de *reg* é deslocado um *bit* para a esquerda (*reg(6 downto 0)*) com o *bit* da entrada D sendo inserido na posição menos significativa (através da concatenação pela direita *&D*). A saída *Q* reflete continuamente o valor completo de 8 *bits* armazenado em *reg*. Após 8 pulsos de *clock* com SHIFT ativo e RESET inativo, um *byte* completo da entrada D será carregado serialmente no registrador, ficando disponível na saída *Q*.

12. Na sequência, temos a descrição de Counter4Bit (Contador no esquemático do item 2). A interface externa deste contador inclui o sinal de entrada clk (CLK), o sinal RESET (RSCNT) e dois sinais de saída C de 4 bits (C0-C3) e Z de 1 bit.

```

120 -- Entidade Contador de 4 bits

121 library IEEE;

122 use IEEE.STD_LOGIC_1164.ALL;

123 use IEEE.STD_LOGIC_UNSIGNED.ALL;

124

125 entity Counter4Bit IS

126     PORT (

127         clk      : IN STD_LOGIC;           -- Clock de entrada

128         RESET   : IN STD_LOGIC;           -- Sinal de reset

129         C       : OUT STD_LOGIC_VECTOR(3 downto 0); -- Saída do contador de 4 bits

130         Z       : OUT STD_LOGIC;           -- Saída que indica quando o contador está em 0

131     );

132 end entity Counter4Bit;

133

134 architecture Behavioral of Counter4Bit is

135     signal count : STD_LOGIC_VECTOR(3 downto 0) := "0000"; -- Contador interno de 4 bits,

136     inicializado em 0

137     begin

138         process(clk)

139         begin

140             if falling_edge(clk) then

141                 -- Se RESET estiver ativo, zera o contador

142                 if RESET = '1' then

143                     count <= "0000";

144                 else

145                     -- Incrementa o contador

146                     count <= count + 1;

147                 end if;

148             end if;

149         end process;

150         -- Atribuição da saída do contador

151         C <= count;

152         -- Atribuição da saída Z, que indica se o contador está em zero

153         Z <= '1' when count = "0000" else '0';

154     end architecture Behavioral;

```

A seção architecture Behavioral descreve um contador síncrono de 4 bits. Ele utiliza um sinal interno chamado count, inicializado em 0000, para armazenar o valor atual da contagem. Sua operação é sincronizada pela borda de descida do sinal de clock (clk). Se o sinal RESET estiver ativo ('1'), o contador é zerado. Caso contrário, o valor de count é incrementado em um a cada pulso de clock. A saída C reflete o valor atual de 4 bits do contador. Além disso, há uma saída Z que se torna '1' apenas quando o contador está em 0000, indicando que ele atingiu zero, e '0' em qualquer outro estado.

13. O último componente do controlador, não presente explicitamente no esquemático do item 2, é a entidade StateMachine. Ela é responsável por implementar o diagrama de estados mostrado no mesmo item. Em sua interface externa, a StateMachine recebe o sinal de clk e o sinal Z, que indica o término de um ciclo de contagem de 16 pulsos pelo contador. Há também o sinal WR, utilizado para carregar um byte a ser transmitido. Por fim, a StateMachine possui uma saída de 8 bits, output (referenciada como R0-R7 no esquemático do item 2), que corresponde ao vetor de sinais de controle [LDTx, SHTx, RSRx, SHRx, LDRx, RSCNT, TCPLT, SCK] detalhado no mesmo item.

```

155 -- ENTIDADE DA MAQUINA DE ESTADOS FINITOS

156 library IEEE;

157 use IEEE.STD_LOGIC_1164.ALL;

158

159 entity StateMachine is

160     Port ( clk      : in STD_LOGIC;

161            WR       : in STD_LOGIC;

162            Z        : in STD_LOGIC;

163            output   : out STD_LOGIC_VECTOR(7 downto 0)

164        );

165 end entity StateMachine;

```

```

166

167 architecture Behavioral of StateMachine is

168     -- Definindo os estados

169     type state_type is (IDLE, PREPARE, SCK1, SCK0, SAVE);

170     signal state, next_state : state_type;

171

172     -- Definindo o vetor de saída

173     signal out_reg : STD_LOGIC_VECTOR(7 downto 0);

174

175 begin

176     -- Processo de máquina de estados

177     process(clk)

178     begin

179         if rising_edge(clk) then

180             state <= next_state;

181         end if;

182     end process;

183

184     -- Atribuindo a saída para o vetor de saída

185     output <= out_reg;

186

187     -- Definindo a lógica de transição de estados e geração das saídas

188     process(state, WR, Z)

189     begin

190         case state is

191             when IDLE =>

192                 out_reg <= "00000010"; -- Saída inicial no estado IDLE

193                 if WR = '1' then

194                     next_state <= PREPARE;

195                 else

196                     next_state <= IDLE;

197                 end if;

198

199             when PREPARE =>

200                 out_reg <= "10100100"; -- Valor de saída no estado PREPARE

201                 next_state <= SCK1; -- Transição incondicional para SCK1

202

203             when SCK1 =>

204                 out_reg <= "00010001"; -- Valor de saída no estado SCK1

205                 next_state <= SCK0; -- Transição incondicional para SCK0

206

207             when SCK0 =>

208                 out_reg <= "01000000"; -- Valor de saída no estado SCK0

209                 if Z = '1' then

210                     next_state <= SAVE; -- Transição para SAVE se Z = 1

211                 else

212                     next_state <= SCK1; -- Transição para SCK1 se Z = 0

213                 end if;

214

215             when SAVE =>

216                 out_reg <= "00001000"; -- Valor de saída no estado SAVE

217                 next_state <= IDLE; -- Transição incondicional para IDLE

218

219             when others =>

220                 out_reg <= "00000010"; -- Valor de saída por padrão (IDLE)

221                 next_state <= IDLE; -- Retorna para IDLE em caso de erro

222         end case;

223     end process;

224 end architecture Behavioral;

```

A seção `architecture Behavioral` descreve uma máquina de estados finita que controla uma sequência de operações baseada em seus estados internos e entradas externas. O sinal `out_reg` atua como um registrador de 8 *bits* para armazenar o vetor de sinais de controle em cada estado. Sincronizada pela borda de subida do `clock`, a máquina transita entre cinco estados (IDLE, PREPARE, SCK1, SCK0, SAVE). Em cada estado, ela gera um vetor de controle de 8 *bits* (`out_reg`). As transições são determinadas por sinais de entrada como WR (para iniciar uma operação a partir do estado IDLE) e Z (para sinalizar a conclusão de um ciclo no estado SCK0), ou são incondicionais, guiando o fluxo da sequência. A saída `output` espelha o vetor de controle gerado.

Note a descrição de dois processos concorrentes, `process(clk)` e `process(state, WR, Z)`, para representar a máquina de estados finitos. Essa é uma prática de *design* muito comum e altamente recomendada, conhecida como "*Two-Process FSM*":

- `process(clk)` é um **processo puramente síncrono** de registrador de estados, sensível apenas ao sinal de `clk` e responsável por registrar o próximo estado (`next_state`) no estado atual (`state`) na borda ativa do `clock` (neste caso, `rising_edge(clk)`).

- `process(state, WR, Z)` é um **processo** sensível às mudanças nos sinais de entrada que determinam o próximo estado (`state, WR, Z`). Como não é sensível ao `clock`, a lógica dentro dele é **combinacional**. Ele é responsável por calcular o `next_state` (lógica de transição de estados) com base no `current_state` (`state`) e nas entradas (`WR, Z`) e gerar os valores de saída (`out_reg`) com base no estado corrente (`state`).

Essa separação ajuda o sintetizador a inferir de forma mais eficiente os *flip-flops* para o estado e a lógica combinacional para as transições e saídas, resultando em um *hardware* mais otimizado em termos de área e *timing*, além de reduzir a probabilidade de criar lógica com *glitches* ou caminhos de *timing* problemáticos que podem surgir quando a lógica de registrador e a lógica combinacional estão emaranhadas.

14. Após as definições das 6 entidades que compõem o controlador (5 no *datapath* mais a FSM), temos a definição da entidade que engloba todos os itens, denominada `MasterSPI`. Sua porta, apresentada no item 1, apresenta todos os sinais de entrada e saída do controlador. Na arquitetura, inicialmente devem ser declarados os **componentes** a serem usados. Cada componente é semelhante aos **protótipos** das funções em C, descrevendo sua interface com os demais elementos do código.

```

243 architecture RTL of MasterSPI is

244     -- Declara componente TxReg

245     component TxReg

246         Port (

247             clk    : in STD_LOGIC;

248             Tx_load : in STD_LOGIC;

249             Tx_in  : in STD_LOGIC_VECTOR(7 downto 0);

250             Tx_out : out STD_LOGIC_VECTOR(7 downto 0);

251         );

252     end component;

253

254     -- Declara componente TxShiftReg

255     component TxShiftReg

256         Port (

257             clk      : IN STD_LOGIC;

258             LOAD    : IN STD_LOGIC;

259             SHIFT   : IN STD_LOGIC;

260             D       : IN STD_LOGIC_VECTOR(7 downto 0);

261             Q7      : OUT STD_LOGIC

262         );

263     end component;

264

265     -- Declara componente RxShiftReg

266     component RxShiftReg

267         Port (

268             clk      : IN STD_LOGIC;

269             RESET   : IN STD_LOGIC;

270             SHIFT   : IN STD_LOGIC;

271             D       : IN STD_LOGIC;

272             Q       : OUT STD_LOGIC_VECTOR(7 downto 0)

273         );

274     end component;

275

276     -- Declara componente RxReg

277     component RxReg

278         Port (

279             clk    : in STD_LOGIC;

280             Rx_load : in STD_LOGIC;

281             Rx_in  : in STD_LOGIC_VECTOR(7 downto 0);

282             Rx_out : out STD_LOGIC_VECTOR(7 downto 0);

283         );

284     end component;

285

286     -- Declara componente contador de bits

287     component Counter4Bit

288         Port (