# **DISCIPLINA EA701**

## **Introdução aos Sistemas Embarcados**

### **ROTEIRO 3: Varredura (*Polling*) e Interrupção**

**VARREDURA, PROCESSAMENTO DE INTERRUPÇÕES, PILHAS,

CONTROLADOR DE INTERRUPÇÕES VETORIZADAS ANINHADAS

(NVIC), CONTROLADOR DE INTERRUPÇÕES E EVENTOS

ESTENDIDO (EXTI),

CONTROLADOR DE CONFIGURAÇÃO DO SISTEMA (SYSCFG).**

**Profs. Antonio A. F. Quevedo e Wu Shin-Ting**

**FEEC / UNICAMP**

**Revisado em fevereiro de 2025 por Ting com auxílio do Chatgpt**

**Revisado em agosto de 2024**

This work is licensed under Creative Commons

Attribution-NonCommercial-ShareAlike 4.0 International. To view a copy of this

license, visit <https://creativecommons.org/licenses/by-nc-sa/4.0>

|                                                        |           |

|--------------------------------------------------------|-----------|

| <b>INTRODUÇÃO</b>                                      | <b>2</b>  |

| <b>PROJETOS-EXEMPLO</b>                                | <b>3</b>  |

| Um projeto de GPIO com Polling                         | 3         |

| Um Projeto de GPIO com Interrupção                     | 11        |

| <b>FUNDAMENTOS TEÓRICOS</b>                            | <b>19</b> |

| CARACTERÍSTICAS BÁSICAS DE SINAIS DIGITAIS             | 20        |

| POLLING                                                | 20        |

| EXCEÇÕES E INTERRUPÇÕES                                | 21        |

| Ciclo de Interrupção                                   | 23        |

| Prioridade de Atendimento                              | 27        |

| ESTRUTURA DE DADOS: PILHAS                             | 29        |

| <b>STM32H7A3: INTERRUPÇÕES/EXCEÇÕES ANINHADAS</b>      | <b>33</b> |

| Controlador de Interrupções Aninhadas (NVIC)           | 35        |

| Controlador de interrupções e eventos estendido (EXTI) | 39        |

| Controlador de Configuração do Sistema (SYSCFG)        | 43        |

## INTRODUÇÃO

A interface mais simples de um microcontrolador com o mundo exterior é através de sinais digitais básicos (níveis alto e baixo) em seus pinos, seja com o microcontrolador produzindo estes sinais (Saídas) ou lendo os sinais digitais provindos de outros elementos do sistema digital (Entradas), sempre através de seus pinos físicos. O módulo interno que gerencia esta comunicação digital básica é denominado **GPIO** (do inglês *General Purpose Input/Output*, ou Entrada/Saída de Uso Geral). Nos primeiros testes, configuramos o pino PB0 como uma saída digital, ativando e configurando o módulo GPIOB correspondente. Controlamos o estado do pino utilizando o registrador de controle GPIOB\_BSRR para definir os níveis lógicos ou o registrador de dados GPIOB\_ODR para “escrever” o estado do pino.

Neste roteiro, expandiremos o uso do GPIO para incluir entradas digitais e exploraremos dois métodos amplamente utilizados para monitorar o estado de sinais ou módulos externos ao núcleo do processador: **polling** e **interrupção**. O *polling* envolve a verificação contínua de um evento de interesse por meio de comandos, para determinar se o fluxo de execução deve ser interrompido. Por outro lado, a interrupção permite que o processador desvie automaticamente o fluxo de execução assim que um evento relevante ocorre. Além disso, abordaremos a programação dos periféricos do microcontrolador para implementar ambos os métodos. Também discutiremos a importância da estrutura de dados chamada **pilha** no gerenciamento do tratamento de interrupções.

Nos dois primeiros roteiros, exploramos como configurar microcontroladores para enviar sinais a dispositivos externos, com foco específico no controle de LEDs. Para que um microcontrolador seja realmente útil, ele precisa interagir com o mundo externo através de seus pinos, tanto recebendo quanto respondendo a sinais gerados por dispositivos externos. Ao longo deste curso, veremos que os microcontroladores possuem pinos com as mais diversas funções, permitindo **comunicação bidirecional** com o ambiente externo. Neste roteiro, daremos início às interações digitais básicas, abordando a entrada de sinais digitais gerados por um botão de acionamento. Um dos principais desafios ao lidar com esses sinais é sua **natureza assíncrona** em relação ao sinal de relógio do microcontrolador, além da imprevisibilidade de quando esses sinais ocorrem. Antes de aprofundarmos nos detalhes técnicos, vamos apresentar duas soluções práticas amplamente utilizadas através de dois projetos-exemplo para você ter um entendimento claro como essas soluções funcionam.

## PROJETOS-EXEMPLO

Já parou para pensar como seu computador, com seu ritmo de trabalho ditado por um relógio, consegue lidar com eventos inesperados do mundo exterior? Imagine um clique do *mouse*, um toque na tela, um sinal da internet, ou um pressionamento numa tecla do teclado. Como o processador “escuta” e “entende” esses eventos que surgem sem aviso, num ritmo completamente diferente do seu? No mundo digital, os eventos assíncronos são a regra, não a exceção. Eles acontecem a qualquer momento, independentemente do “tic-tac” do processador.

### Um projeto de GPIO com *Polling*

Como usar o CMSIS, abordado no Roteiro 2, para programar o microcontrolador STM32H7A3 da placa NUCLEO-144, de forma que o LED verde alterne seu estado apenas quando o botão azul (entrada digital) for pressionado, em vez de alternar automaticamente? Pode parecer simples, mas esse conceito é fundamental para qualquer sistema embarcado interativo. Afinal, é assim que dispositivos reagem ao toque de um usuário, sensores e comandos externos. Vamos juntos entender como programar o microcontrolador, passo-a-passo, para monitorar o botão via *polling*, explorar os desafios dessa abordagem e fazer com que o microcontrolador responda às interações do mundo real.

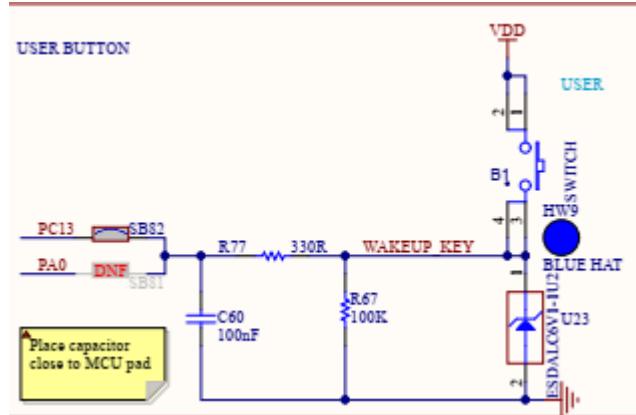

Vamos usar o pino PC13 como entrada, pois ele está ligado ao botão azul na placa, como se pode ver no trecho do esquemático oficial da placa, reproduzido abaixo:

À esquerda, existem *jumpers* que determinam se o botão é ligado no pino PC13 ou no PA0, sendo que o padrão da placa é o PC13. O resistor de 100k mantém o pino PC13 em nível lógico baixo, até que o botão seja pressionado. O resistor de 330R e o capacitor de 100nF evitam o fenômeno de *bounce*, ou “repique” dos contatos mecânicos do botão, que faz com que um pressionamento seja reconhecido como múltiplas transições entre os níveis alto e baixo na entrada digital. Este fenômeno será melhor estudado quando trabalharmos com entrada de teclado matricial. Assim, ao se pressionar o botão, o pino PC13 vai ao nível lógico alto, e ao se soltar o botão o pino retorna ao nível lógico baixo.

1. Crie o projeto “Toggle\_Polling” [da mesma forma](#) que o projeto com CMSIS do Roteiro 2. Lembre-se de selecionar “Empty” na opção “Targeted Project Type” e de adicionar as pastas com os arquivos de suporte, além de colocar o “include” para o arquivo de cabeçalho. Adicione os caminhos que contêm os arquivos de cabeçalho “stm32h7a3xxq.h” e “core\_cm7.h”

2. Vamos repetir a configuração do pino PB0 para o LED verde, e vamos incluir a configuração do PC13 como entrada. No [Manual de Referência](#), vemos que o bit 2 do registrador RCC\_AHB4ENR habilita o GPIOC. Assim, podemos setar (colocar em “1”) os bits 1 e 2 deste registrador simultaneamente para ativar GPIOB e GPIOC usando códigos binários:

`RCC_AHB4ENR |= 0x00000006;`

ou usando a interface CMSIS:

```

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN_Msk |

RCC_AHB4ENR_GPIOCEN_Msk;

```

Na sequência, os registradores de GPIOB são configurados como no projeto do Roteiro 2, para que se possa ligar e desligar o LED verde. Para a entrada do *push-button*, vamos configurar o pino 13 de GPIOC como entrada digital. Os registradores de GPIOC são idênticos aos de GPIOB. Assim, só é necessário configurar o registrador GPIOC\_MODER para que o pino 13 funcione como entrada. No [Manual de Referência](#), pode-se ver que os dois bits de configuração de um pino precisam estar em “0” para que o pino seja configurado como entrada. Para o pino 13, os bits correspondentes são o 27 e o 26. Assim, a instrução de configuração fica:

`GPIOC_MODER &= 0xF3FFFFFF;`

Se usarmos a interface CMSIS, basta saber o número do pino, que é 13

```

GPIOC->MODER &= ~(GPIO_MODE13_Msk);

```

Por fim, para ler o nível lógico de um pino de entrada, basta ler o registrador GPIOC\_IDR (*Input Data Register*). O *bit* 13 será “0” quando o pino PC13 está em nível lógico baixo, e “1” quando o pino está no nível lógico alto. Para que possamos monitorar o estado deste pino, é necessário realizar repetidas leituras do valor do IDR dentro de um *loop*. Este processo é denominado **Polling**.

3. Dentro da função *main*, escreva o seguinte código:

```

int main(void) {

uint8_t status = 0;

RCC->AHB4ENR |= 0x00000006; // Habilita GPIOB e GPIOC

GPIOB->MODER |= 0x00000001; // PB0 como saída digital

GPIOB->MODER &= 0xFFFFFFF0;

GPIOB->OTYPER &= 0xFFFFFFFF; // PB0 como push-pull

GPIOC->MODER &= 0xF3FFFFFF; // PC13 como entrada digital

GPIOB->ODR &= 0xFFFFFFFF; // PB0 = 0

/* Loop forever */

for(;;) { // Fazendo Polling

if(GPIOC->IDR & (1 << 13)) { // PC13 = 1

if(status) { // LED está On

GPIOB->ODR &= 0xFFFFFFFF; // LED Off

status = 0;

} else { // LED está Off

GPIOB->ODR |= 0x00000001; // LED On

status = 1;

}

while(GPIOC->IDR & (1 << 13));

}

}

}

```

Note o teste feito no início do *loop for* infinito. O valor de IDR é lido e é feita uma máscara AND com todos os *bits* em “0”, exceto o *bit* 13. A expressão “`(1 << 13)`” significa que o valor “1” sofre um deslocamento de 13 *bits* para a esquerda (em binário, corresponde a 0010 0000 0000 0000). O valor resultante será zero se o *bit* 13 do IDR estiver em “0”, ou o valor “0x2000” se o *bit* 13 estiver em “1”. Ou seja, o código dentro do *if* só será executado caso o botão esteja pressionado, pois valores zero são interpretados no *if* como “falso” e qualquer valor diferente de zero é interpretado como “verdadeiro”.

Alternativamente, o CMSIS disponibiliza macros para as máscaras de *bits* que podem ser usadas para setar ou limpar *bits* dos registradores, geralmente denominadas **campos de bits**. Estas máscaras estão definidas também no arquivo “stm32h7a3xxq.h”, e usam sempre o

sufixo “\_Msk”. Para o *bit* 13 do `GPIOx_IDR`, existe a máscara `GPIO_IDR_ID13_Msk`. Faça uma busca (Ctrl+F) pelo nome da máscara no arquivo “`stm32h7a3xxq.h`”. A definição para esta máscara é “`(0x1UL << GPIO_IDR_ID13_Pos)`”. Ou seja, o valor “1” expresso como “*Unsigned Long*” (UL, tipo de dados de 32 *bits* sem sinal), com um deslocamento de *bits* à esquerda de um valor definido por “`GPIO_IDR_ID13_Pos`”. Na linha imediatamente acima, encontramos a definição de “`GPIO_IDR_ID13_Pos`”, que é “`(13U)`”, ou seja, o valor 13 sem sinal. Assim, a máscara corresponde à expressão “`(1 << 13)`” usada originalmente. Portanto, os dois comandos “`while(GPIOC->IDR & (1 << 13));`” e “`while(GPIOC->IDR & GPIO_IDR_ID13_Msk);`” são equivalentes.

Dentro do *if*, a variável *status* é verificada. Esta variável segue o estado do LED: valor “1” se o LED está aceso e valor “0” se o LED está apagado. Assim, o estado do LED é invertido. Após ao inversão do estado do LED, existe um *loop* do tipo **while**. Este *loop* permanece em execução enquanto a condição lógica entre parênteses for verdadeira. No programa acima, o *loop while* atualiza a leitura do botão, só permitindo a continuidade da execução do programa quando o mesmo for solto (entrada em nível baixo). Veja que não há o “abre-efecha colchetes” neste *loop*, apenas um ponto-e-vírgula após a declaração do *while*. Isto indica que nenhuma instrução será executada enquanto o programa não sair do *loop*, exceto as existentes dentro da condição de teste (no caso, a leitura do registrador e a máscara AND). Este laço de espera é crucial para evitar que o LED alterne repetidamente entre os estados enquanto o botão estiver pressionado. Sem esse laço, o LED poderia passar por várias transições rápidas, em vez de realizar apenas uma mudança de estado quando o botão é pressionado e solto. Vamos entender esta última afirmação mais adiante.

4. Realize o *Build* e o *Debug*. Execute o programa e veja o estado do LED se invertendo a cada pressão do botão.

5. Adicione um *breakpoint* na linha “`if(status)`”. Veja que o programa apenas atinge o *breakpoint* quando o botão é pressionado. A partir daí, execute o programa passo a passo (tecla F6 ou botão “Step Over”) e veja o comportamento do programa.

6. Remova o *breakpoint* do item anterior, e acrescente as seguintes linhas:

```

uint32_t d; (logo abaixo a declaração da variável “status”)

```

```

for (d = 0; d < 16000000; d++); (logo após a linha “for (;;) {“)

```

Faça o *Build* e o *Debug* e execute o programa. Veja o que acontece ao se pressionar o botão. Veja o que acontece ao se manter o botão pressionado por vários segundos. O LED está respondendo às ações sobre o botão como esperado? Por quê isto acontece? Este é um dos principais problemas do *polling* que discutiremos mais adiante.

7. Substitua a linha de comando “`for (d = 0; d < 16000000; d++);`” pela chamada da função “`espera (16000000)`”, conforme implementada no Roteiro 2. O código

atualizado, que utiliza a interface CMSIS, deve se parecer com o exemplo abaixo. Após realizar a alteração, faça o *Build* e transfira o código para o microcontrolador em modo *Debug*.

```

int main(void)

{

// Inicializa GPIOB (PB0) e GPIOC (PC13)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN_Msk | RCC_AHB4ENR_GPIOCEN_Msk;

// PB0 como saída digital

GPIOB->MODER &= ~(GPIO_MODER_MODE0_Msk);

GPIOB->MODER |= GPIO_MODER_MODE0_0;

GPIOB->OTYPER &= ~GPIO_OTYPER_OT0_Msk; // PB0 como push-pull

// PC13 como entrada digital

GPIOC->MODER &= ~(GPIO_MODER_MODE13_Msk);

// Inicializa PB0 apagado

GPIOB->ODR &= ~GPIO_ODR_OD0_Msk;

uint8_t status=0;

/* Loop forever */

for(;;) {

espera (16000000);

if (GPIOC->IDR & GPIO_IDR_ID13_Msk) {

if (!status) {

GPIOB->ODR |= GPIO_ODR_OD0_Msk; // PB0 = 1

status = 1;

} else {

GPIOB->ODR &= ~GPIO_ODR_OD0_Msk; // PB0 = 0

status = 0;

}

while (GPIOC->IDR & GPIO_IDR_ID13_Msk);

}

}

}

```

Compare as instruções usando as macros da interface CMSIS

```

GPIOB->MODER &= ~(GPIO_MODER_MODE0_Msk);

GPIOB->MODER |= GPIO_MODER_MODE0_0;

```

com as instruções apresentadas no Roteiro 2 usando endereços dos registradores:

```

GPIOB_MODER&=0xFFFFFFF;

GPIOB_MODER|=0x00000001;

```

Ambos os conjuntos de instruções são equivalentes. Para verificar isso, você pode rastrear as macros definidas no arquivo de cabeçalho “stm32h7a3xxq.h”. No editor da perspectiva C/C++, você pode consultar essas macros passando o *mouse* sobre elas.

|                              |                                 |

|------------------------------|---------------------------------|

| #define GPIO_MODER_MODE0_Pos | (0U)                            |

| #define GPIO_MODER_MODE0_Msk | (0x3UL << GPIO_MODER_MODE0_Pos) |

|                              | /*!< 0x00000003 */              |

| #define GPIO_MODER_MODE0     | GPIO_MODER_MODE0_Msk            |

| #define GPIO_MODER_MODE0_0   | (0x1UL << GPIO_MODER_MODE0_Pos) |

|                              | /*!< 0x00000001 */              |

Substituindo as macros pelas suas definições, recursivamente até alcançar as macros-folha, como faz o pré-processador:

$$\sim(\text{GPIO\_MODER\_MODE0\_Msk}) = \sim(0x3\text{UL} \ll \text{GPIO\_MODER\_MODE0\_Pos}) \\ = \sim(0x3\text{UL} \ll 0\text{U}) = \sim(0x3\text{UL}) = 0xFFFFFFF$$

$$\text{GPIO\_MODER\_MODE0\_0} = (0x1\text{UL} \ll \text{GPIO\_MODER\_MODE0\_Pos}) \\ = (0x1\text{UL} \ll 0) = 0x1\text{UL}$$

obtemos os valores reais que o compilador interpretará. Neste caso, o valor da macro `GPIO_MODER_MODE0_0` é `0x1UL`, ou seja, “1”.

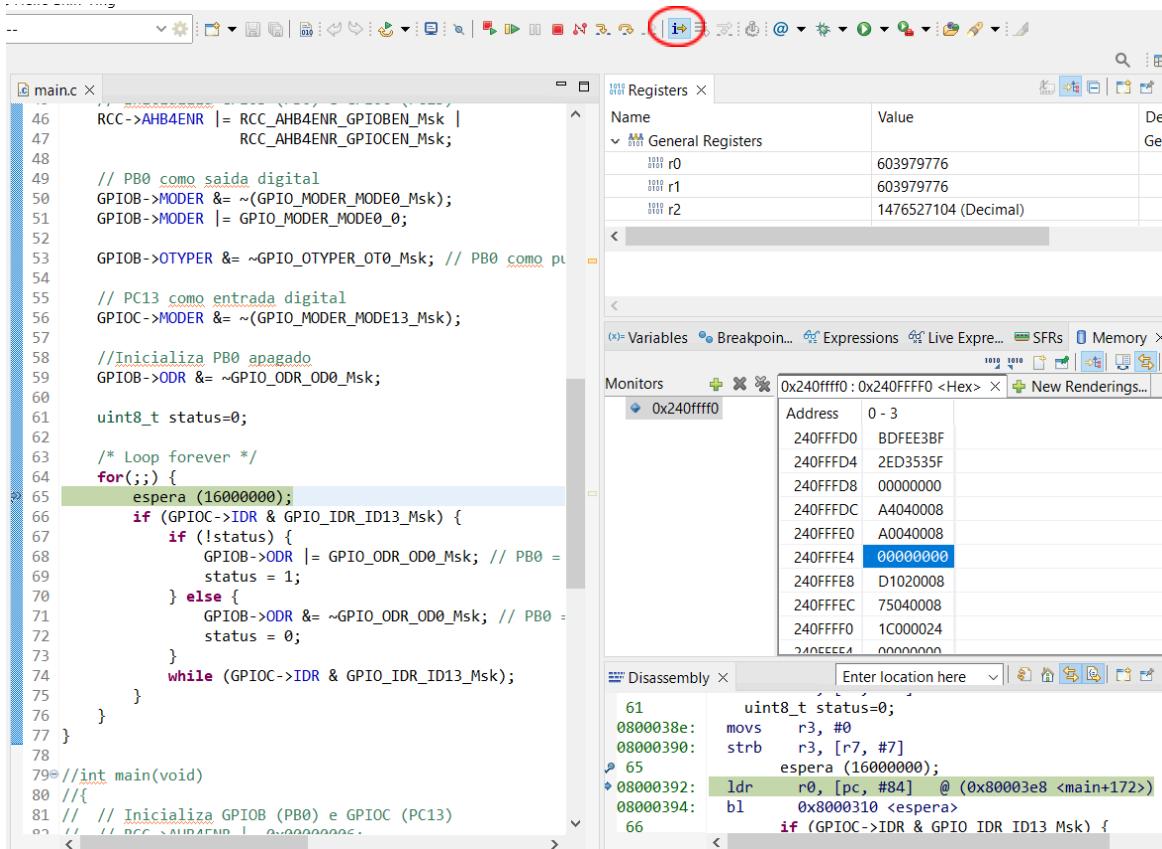

8. Abra a aba “Disassembly” na perspectiva “Debug” e coloque um *breakpoint* na linha que contém “espera (16000000)”. Inicie a execução do programa. Quando a execução parar no *breakpoint*, observe a linha correspondente em *assembly* na aba “Disassembly”. Em seguida, verifique o conteúdo do endereço `0x8000310` na aba “Disassembly”.

The screenshot shows the Eclipse IDE interface with the C code editor and assembly view. The code editor displays the following snippet of C code:

```

47     RCC_AHB4ENR_GPIOCEN_Msk;

48

49 // PB0 como saida digital

50 GPIOB->MODER &= ~(GPIO_MODER_MODE0_Msk);

51 GPIOB->MODER |= GPIO_MODER_MODE0_0;

52

53 GPIOB->OTYPER &= ~GPIO_OTYPER_OT0_Msk; // PB0 como push-pull

54

55 // PC13 como entrada digital

56 GPIOC->MODER &= ~(GPIO_MODER_MODE13_Msk);

57

58 //Iniciaiza PB0 apagado

59 GPIOB->ODR &= ~GPIO_ODR_OD0_Msk;

60

61 uint8_t status=0;

62

63 /* Loop forever */

64 for(;;) {

65     espera (16000000);

66     if (GPIOC->IDR & GPIO_IDR_ID13_Msk) {

67         if (!status) {

68             GPIOB->ODR |= GPIO_ODR_OD0_Msk; // PB0 = 1

69             status = 1;

70         } else {

71             GPIOB->ODR &= ~GPIO_ODR_OD0_Msk; // PB0 = 0

72             status = 0;

```

The assembly view shows the generated assembly code. The instruction at address `0x8000392` is highlighted, corresponding to the `espera (16000000);` line in the C code. The assembly code for this instruction is:

```

59     GPIOB->ODR &= ~GPIO_ODR_OD0_Msk;

08000382: ldr    r3, [pc, #92]  @ (0x80003e0 <main+164>

08000384: ldr    r3, [r3, #20]

08000386: ldr    r2, [pc, #88]  @ (0x80003e0 <main+164>

08000388: bic.w r3, r3, #1

0800038c: str    r3, [r2, #20]

61     uint8_t status=0;

0800038e: movs   r3, #0

08000390: strb   r3, [r7, #7]

08000392: ldr    r0, [pc, #84]  @ (0x80003e8 <main+172>

08000394: b1    0x8000310 <espera>

65     espera (16000000);

08000398: ldr    r3, [pc, #72]  @ (0x80003e4 <main+168>

```

| Name | Value               |

|------|---------------------|

| sp   | 0x240ffff0          |

| lr   | 134218787           |

| pc   | 0x8000392 <main+86> |

| xdsr | 1627389952          |

< Enter location here

Disassembly x

```

espera:

08000310: push {r7, lr}

08000312: sub sp, #16

08000314: add r7, sp, #0

08000316: str r0, [r7, #4]

multiplo_iteracoes (valor, &i);

08000318: add.w r3, r7, #12

0800031c: mov r1, r3

0800031e: ldr r0, [r7, #4]

08000320: bl 0x80002ec <multiplo_iteracoes>

while (i) i--;

08000324: b.n 0x800032c <espera+28>

08000326: ldr r3, [r7, #12]

08000328: subs r3, #1

0800032a: str r3, [r7, #12]

0800032c: ldr r3, [r7, #12]

0800032e: cmp r3, #0

08000330: bne.n 0x8000326 <espera+22>

41

08000332:

```

9. Abra a aba “Memory” e insira o endereço do ponteiro da pilha (SP ou R13). Configure o formato de exibição para “Row Size” e “Column Size” igual a 4. Em seguida, abra a aba “Registers” para monitorar o conteúdo dos registradores. Ative o modo “Instruction Stepping” pelo ícone destacado para avançar a execução do programa, instrução por instrução, em *assembly*.

10. Avance um passo “Step Over” (tecle F6) e registre o valor carregado em r0, PC, SP. No Roteiro 1 vimos que os registradores PC e SP armazenam, respectivamente, o endereço da próxima instrução a ser buscada na memória e o endereço do topo da pilha que veemos mais adiante.

11. Na linha da instrução “bl 0x8000310”, avance com o comando “Step Into” (tecla F5) para entrar na função “espera”. Em seguida, use o comando “Step Over” (tecla F6) para avançar pelas instruções até chegar na instrução “add.w r3, r7, #12”. Monitore as alterações no conteúdo da pilha a cada passo. Você consegue responder às seguintes perguntas?

- Qual é a função da instrução “push [r7, lr]”?

- Quais dados foram empilhados desde a entrada na função “espera” até este ponto?

- Quais deles são originados durante o chaveamento de contexto?

- Em qual endereço (da pilha) está armazenado o parâmetro de entrada “valor”?

- Em qual endereços (da pilha) está armazenado a variável local “i”?

- Qual registrador é usado como *frame pointer*?

- Quais são os endereços relativos (deslocamentos ou *offsets*) de “valor” e “i” em relação ao *frame pointer*?

Na aba “Memory”, destaque o quadro de pilha (*stack frame*) da chamada da função “espera”.

```

Registers X

Name Value

r0 16000000

r1 603979776

r2 1476527104 (Decimal)

Monitors + ✎ ✎ ✎

0x240ffff0

Address 0 1 2 3

240FFE4 00 00 00 00

240FFE8 F0 FF 0F 24

240FFEC 99 03 00 08

240FFFF0 1C 00 00 24

240FFF4 00 00 00 00

Disassembly X Enter location here

espera:

08000310: push {r7, lr}

08000312: sub sp, #16

08000314: add r7, sp, #0

08000316: str r0, [r7, #4]

39 multiplo_iteracoes (valor, &i);

*08000318: add.w r3, r7, #12

0800031c: mov r1, r3

0800031e: ldr r0, [r7, #4]

08000320: bl 0x80002ec <multiplo_iteracoes>

10 while (i--)

```

Sem pânico se as respostas das perguntas não surgirem e você não entendeu as instruções destacadas agora! Ao desvendarmos juntos o mecanismo por trás deste conceito mais adiante, tudo fará mais sentido e as respostas se revelarão. Revisite este ponto, refaça os itens subsequentes e teste seus conhecimentos sobre **um mecanismo de passagem de parâmetros entre funções via pilha**, depois de estudar os fundamentos teóricos apresentados mais adiante.

12. Avance usando "Step Over" até a instrução "bl 0x80002ec". Antes de utilizar "Step Into" para entrar na função "multiplo\_iteracoes", registre o conteúdo dos registradores r0, r1, PC e SP.

13. Ao entrar na função "multiplo\_iteracoes", avance com "Step Over" até a instrução "ldr r3, [r7,#4]". Registre o conteúdo da pilha após a entrada na função. Identifique como os valores das variáveis "valor" e "j" são acessados. Além disso, determine qual é o quadro de pilha (*stack frame*) para esta chamada e qual registrador está sendo usado como *frame pointer* para a chamada desta função.

14. Com base na análise realizada até agora, descreva as diferenças entre a passagem de parâmetros por valor e a passagem de parâmetros por (valor de) endereço em termos de instruções de máquina na linguagem C. Considere como cada método afeta a execução e o armazenamento dos dados.

15. Continue avançando com "Step Over" até chegar à instrução "return;" no código C. Em seguida, avance até a instrução "bx lr", enquanto monitora o conteúdo dos registradores r7 e SP. Essas instruções são responsáveis pela restauração do contexto anterior antes de retornar ao fluxo da função "espera". Não se esqueça de registrar o conteúdo do registrador lr.

16. Dê um "Step Over" em "bx lr". Anote o endereço da instrução depois do passo e compare-o com o valor de PC que você anotou antes de entrar na função "multiplo\_interacoes".

17. Continue avançando com "Step Over" até atingir a instrução "pop {r7,pc}", monitorando o conteúdo dos registradores r7, PC e SP durante o processo. Após executar um "Step Over" na instrução "pop {r7,pc}", registre o conteúdo atualizado desses registradores. Além disso, explique a função desta instrução.

18. Analise o que foi observado durante o percurso pelo fluxo de execução do programa. Compare suas observações com os conceitos que você aprendeu depois de estudar os fundamentos teóricos apresentados adiante. A execução do programa está alinhada com esses conceitos?

## Um Projeto de GPIO com Interrupção

No passo (6) do projeto anterior, observamos que a inserção do comando

```

for (d = 0; d < 16000000; d++) ;

```

atrapalha o sincronismo entre a ação do usuário e a resposta do microcontrolador. Isso acontece porque o processador só verifica o estado do botão azul depois de concluir a

execução do laço “for”, que leva um tempo muito maior que 1s. Agora, pense nisso: será que há uma maneira de o microcontrolador reagir imediatamente ao pressionamento do botão, sem precisar esperar o fim de uma tarefa em andamento? A resposta é sim! Para isso, utilizamos um recurso chamado **interrupção**. Você já ouviu falar desse mecanismo? Ele permite que o processador pause temporariamente o que está fazendo para lidar com eventos externos, garantindo uma resposta ágil ao usuário.

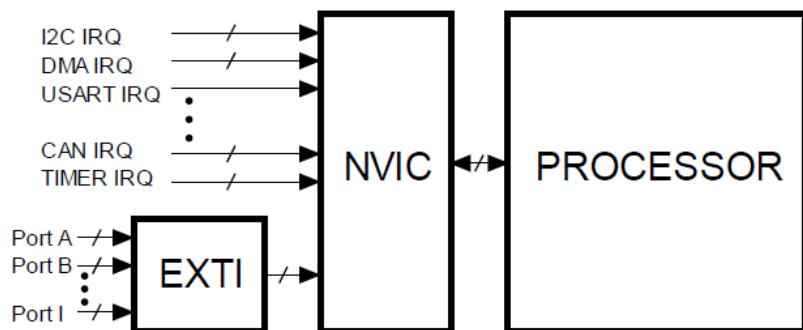

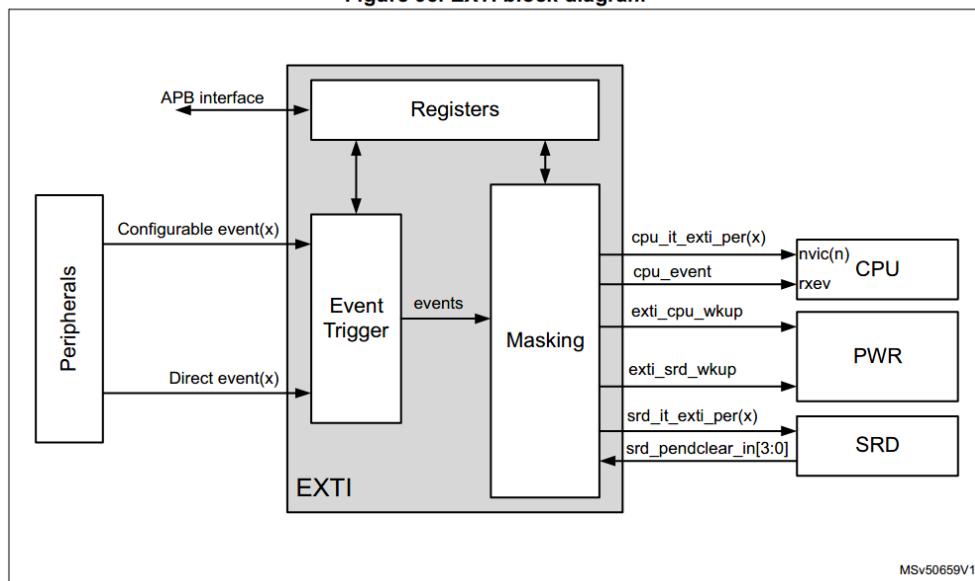

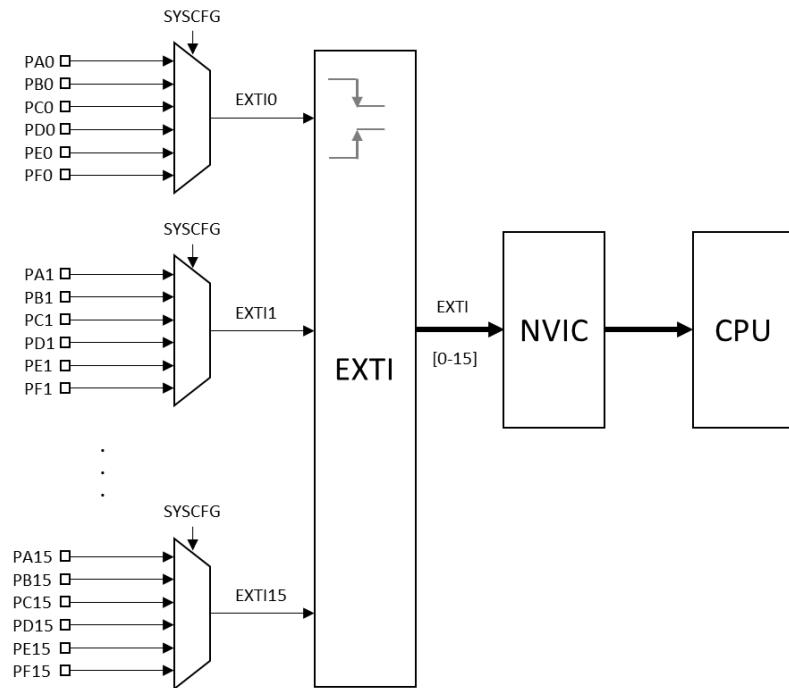

Neste cenário, a interrupção baseada em sinais digitais se torna essencial. Para que o microcontrolador STM32H7A3 responda automaticamente à transição do nível lógico de um pino GPIO, precisamos conectá-lo ao módulo EXTI (do inglês *External Interrupt*), responsável por detectar eventos e acionar uma interrupção. Além disso, devemos configurar o NVIC (do inglês, *Nested Vectored Interrupt Controller*) para processar a interrupção, definindo prioridade, tipo de evento e a função ISR (do inglês, *Interrupt Service Routine*) correspondente.

Vamos, então, juntos executar os passos necessários para implementar essa técnica e tornar a resposta do microcontrolador instantânea e eficiente?

1. Vamos escrever um programa que troque o estado do LED verde quando o botão é pressionado, mas agora usando uma interrupção. Inicialmente, crie o projeto “Toggle\_Int” da mesma forma que o projeto anterior deste roteiro. Lembre-se de selecionar “Empty” na opção “Targeted Project Type” e de adicionar as pastas com os arquivos de suporte “stm32h7a3xxq.h” e “core\_cm7.h”, além de colocar o “include” para o arquivo de cabeçalho.

2. Vamos repetir a configuração do pino PB0 para o LED verde, e vamos incluir a configuração do PC13 como entrada. Repetindo a ativação simultânea de GPIOB e GPIOC:

`RCC_AHB4ENR |= 0x00000006;`

Na sequência, os registradores de GPIOB são configurados como no projeto anterior, para que se possa ligar e desligar o LED verde. Para a entrada do *push-button*, vamos configurar o pino 13 de GPIOC como uma requisição de interrupção sensível à borda de subida (transição de nível baixo para alto). Inicialmente, configura-se o pino como entrada:

```

GPIOC_MODER &= 0xF3FFFFFF;

```

O gerenciamento e roteamento das linhas de interrupção EXTI é feita pelo módulo [EXTI](#) e o mapeamento dos pinos de entrada GPIO nos sinais EXTI acontece no módulo [SYSCFG](#). Inicialmente, precisamos habilitar o módulo SYSCFG, que é ligado ao barramento APB4. Essa habilitação ocorre via o registrador RCC\_APB4ENR. O [Manual de Referência](#) mostra que o bit 1 deste registrador habilita o módulo; daí a instrução:

```

RCC->APB4ENR |= 0x00000002;

```

### 8.7.46 RCC APB4 clock register (RCC\_APB4ENR)

Address offset: 0x154

Reset value: 0x0000 0000

|        |          |        |      |         |          |          |      |        |      |        |      |           |      |           |          |

|--------|----------|--------|------|---------|----------|----------|------|--------|------|--------|------|-----------|------|-----------|----------|

| 31     | 30       | 29     | 28   | 27      | 26       | 25       | 24   | 23     | 22   | 21     | 20   | 19        | 18   | 17        | 16       |

| Res.   | Res.     | Res.   | Res. | DSDM2EN | DTSEN    | Res.     | Res. | Res.   | Res. | Res.   | Res. | Res.      | Res. | Res.      | RTCAPBEN |

|        |          |        |      | rw      | rw       |          |      |        |      |        |      |           |      |           | rw       |

| 15     | 14       | 13     | 12   | 11      | 10       | 9        | 8    | 7      | 6    | 5      | 4    | 3         | 2    | 1         | 0        |

| VREFEN | COMP12EN | DAC2EN | Res. | Res.    | LPTIM3EN | LPTIM2EN | Res. | I2C4EN | Res. | SPI6EN | Res. | LPUART1EN | Res. | SYSCFGGEN | Res.     |

| rw     | rw       | rw     |      |         | rw       | rw       |      | rw     |      | rw     |      | rw        |      | rw        |          |

Agora precisamos conectar o pino PC13 da porta C à linha de interrupção EXTI13. Cada interrupção externa EXTIIn ( $n = 0..15$ ) pode ser conectada ao pino de mesmo número de qualquer porta. A definição da porta usada para cada número de pino é feita pelos registradores SYSCFG\_EXTICR1 (pinos 0 a 3), SYSCFG\_EXTICR2 (pinos 4 a 7), SYSCFG\_EXTICR3 (pinos 8 a 11) e SYSCFG\_EXTICR4 (pinos 12 a 15). Para a EXTI13, usa-se os bits 4, 5, 6 e 7 de [SYSCFG\\_EXTICR4](#). A combinação de bits que especifica a Porta C é 0b0010. Assim, deve-se setar 0b0010 nos bits 4, 5, 6 e 7 do quarto elemento do membro EXTICR da estrutura SYSCFG através de:

SYSCFG->EXTICR[3] &= 0xFFFFFFF0F;

SYSCFG->EXTICR[3] |= 0x00000010;

Note que na linguagem C, o índice inicial de um vetor é sempre 0. Assim, os registradores SYSCFG\_EXTICRn, n de 1 a 4, estão mapeados nas posições do vetor EXTICR de 0 a 3, respectivamente.

Os detalhes da configuração da interrupção são realizados pelo módulo [EXTI](#). Esse módulo suporta até 92 linhas de interrupção. Para configurar a sensibilidade dessas interrupções, o microcontrolador utiliza 3 pares de registradores [EXTI\\_RTSRn](#) e [EXTI\\_FTSRn](#), onde n varia de 1 a 3. Cada bit dentro desses pares de registradores é dedicado a um tipo específico de configuração, sendo EXTI\_RTSRn e EXTI\_FTSRn responsáveis por configurar a sensibilidade à borda de subida (*Rising Edge Trigger*) e à borda de descida (*Falling Edge Trigger*), respectivamente.

Neste projeto, queremos apenas a borda de subida, e assim precisamos setar o bit correspondente em EXTI\_RTSRn e limpar o bit correspondente em EXTI\_FTSRn. Para EXTI13, usamos o bit 13 dos registradores EXTI\_RTSR1 e EXTI\_FTSR1 para configurar a sensibilidade:

EXTI->RTSR1 |= 0x00002000; // Habilita borda de subida de EXTI13

EXTI->FTSR1 &= 0xFFFFDFFF; // Desabilita borda de descida de EXTI13

Ainda no módulo EXTI, é necessário habilitar a **máscara de interrupção** correspondente a EXTI13. A máscara de interrupção permite que o código bloquee temporariamente uma

interrupção quando necessário. Os registradores de máscara de interrupção do módulo são EXTI\_CPUIMRn (n = 1..3). Para EXTI13, precisamos setar o bit 13 de [EXTI\\_CPUIMR1](#):

EXTI->IMR1 |= 0x00002000; // Habilita máscara de EXTI13

Para finalizar, precisamos configurar a prioridade de atendimento da interrupção no NVIC. Neste projeto, vamos atribuir prioridade 1 à nossa interrupção (quanto menor o número, mais prioritária é a interrupção) e habilitar a mesma. No [Manual de Referência](#), podemos ver a tabela de vetores de interrupção. Cada interrupção tem um número, e as 16 primeiras (0 a 15) são as exceções geradas pelo próprio núcleo ARM. A coluna “NVIC position” indica o número de requisição de interrupção. Podemos ver que a interrupção de número 40 é a EXTI15\_10, ou seja, há apenas um vetor de interrupção para tratar as interrupções externas de 10 a 15. É este vetor que devemos usar para EXTI13.

| Signal            | Priority | NVIC position | Acronym   | Description                 | Address offset |

|-------------------|----------|---------------|-----------|-----------------------------|----------------|

| i2c2_ev_it        | 40       | 33            | I2C2_EV   | I2C2 event interrupt        | 0x0000 00C4    |

| exti_i2c2_ev_wkup |          |               |           |                             |                |

| i2c2_err_it       | 41       | 34            | I2C2_ER   | I2C2 error interrupt        | 0x0000 00C8    |

| spi1_it           | 42       | 35            | SPI1      | SPI1 global interrupt       | 0x0000 00CC    |

| exti_spi1_it      |          |               |           |                             |                |

| spi2_it           | 43       | 36            | SPI2      | SPI2 global interrupt       | 0x0000 00D0    |

| exti_spi2_it      |          |               |           |                             |                |

| uart1_gbl_it      | 44       | 37            | USART1    | USART1 global interrupt     | 0x0000 00D4    |

| exti_usart1_wkup  |          |               |           |                             |                |

| uart2_gbl_it      | 45       | 38            | USART2    | USART2 global interrupt     | 0x0000 00D8    |

| exti_usart2_wkup  |          |               |           |                             |                |

| uart3_gbl_it      | 46       | 39            | USART3    | USART3 global interrupt     | 0x0000 00DC    |

| exti_usart3_wkup  |          |               |           |                             |                |

| exti_exti10_wkup  | 47       | 40            | EXTI15_10 | EXTI Line[15:10] interrupts | 0x0000 00E0    |

| exti_exti11_wkup  |          |               |           |                             |                |

| exti_exti12_wkup  |          |               |           |                             |                |

| exti_exti13_wkup  |          |               |           |                             |                |

| exti_exti14_wkup  |          |               |           |                             |                |

| exti_exti15_wkup  |          |               |           |                             |                |

Há um conjunto de registradores de prioridade e de habilitação das interrupções no NVIC. Os detalhes podem ser encontrados na [Documentação da ARM](#).

Para simplificar o trabalho, o CMSIS dispõe macros para configurar prioridade e habilitar as interrupções no NVIC. Assim, usamos:

```

NVIC_SetPriority(EXTI15_10 IRQn, 1); // Prioridade 1

```

```

NVIC_EnableIRQ(EXTI15_10 IRQn); // Habilita

```

O STM32CubeIDE também simplifica o trabalho de achar o endereço inicial da ISR e carregar no vetor de interrupção. Ele já define uma função “void EXTI15\_10\_IRQHandler(void)” que é chamada no atendimento da interrupção, e deve ser definida dentro do arquivo “main.c”. As definições dos nomes de funções ISR para cada

vetor da tabela pode ser encontrada no arquivo “startup\_stm32h7a3zitxq.s”, na pasta “Startup”.

```

174 .word TIM2_IRQHandler      /* TIM2 */          */

175 .word TIM3_IRQHandler      /* TIM3 */          */

176 .word TIM4_IRQHandler      /* TIM4 */          */

177 .word I2C1_EV_IRQHandler   /* I2C1 Event */    */

178 .word I2C1_ER_IRQHandler   /* I2C1 Error */   */

179 .word I2C2_EV_IRQHandler   /* I2C2 Event */    */

180 .word I2C2_ER_IRQHandler   /* I2C2 Error */   */

181 .word SPI1_IRQHandler      /* SPI1 */          */

182 .word SPI2_IRQHandler      /* SPI2 */          */

183 .word USART1_IRQHandler    /* USART1 */        */

184 .word USART2_IRQHandler    /* USART2 */        */

185 .word USART3_IRQHandler    /* USART3 */        */

186 .word EXTI15_10_IRQHandler /* External Line[15:10]s */

187 .word RTC_Alarm_IRQHandler /* RTC Alarm (A and B) through EXTI Line */

188 .word DFSDM2_IRQHandler    /* DFSDM2 Interrupt */

189 .word TIM8_BRK_TIM12_IRQHandler /* TIM8 Break and TIM12 */

190 .word TIM8_UP_TIM13_IRQHandler /* TIM8 Update and TIM13 */

191 .word TIM8_TRG_COM_TIM14_IRQHandler /* TIM8 Trigger and Commutation and TIM14 */

192 .word TIM8_CC_IRQHandler    /* TIM8 Capture Compare */

193 .word DMA1_Stream7_IRQHandler /* DMA1 Stream7 */

194 .word FMC_IRQHandler       /* FMC */

195 .word SDMMC1_IRQHandler    /* SDMMC1 */

196 .word TIM5_IRQHandler      /* TIM5 */

197 .word SPI3_IRQHandler      /* SPI3 */

198 .word UART4_IRQHandler     /* UART4 */

199 .word UART5_IRQHandler     /* UART5 */

200 .word TIM6_DAC_IRQHandler /* TIM6 and DAC1&2 underrun errors */

201 .word TIM7_IRQHandler      /* TIM7 */

```

Para verificar se uma interrupção foi ativada, examine os registradores de *flag*. Após atender a interrupção, limpe a *flag* correspondente, geralmente escrevendo '1' no *bit* específico (do inglês *write-one-to-clear* ou **w1c**).

3. Dentro do arquivo main.c, **antes** da função main(), inclua a definição da rotina de serviço:

```

27 // ISR para linhas EXTI 15_10

28 void EXTI15_10_IRQHandler(void) {

29     static uint8_t status=0;

30

31     if (EXTI->PR1 & EXTI_PR1_PR13_Msk) { // Testa "flag" de EXTI13

32         // Limpar o flag EXTI13

33         EXTI->PR1 |= EXTI_PR1_PR13_Msk;

34

35         // Vamos fazer o "toggle" do LED aqui

36         if(status) { // LED esta On

37             GPIOB->ODR &= ~GPIO_ODR_OD0_Msk; // LED Off

38             status = 0;

39         } else { // LED esta Off

40             GPIOB->ODR |= GPIO_ODR_OD0_Msk; // LED On

41             status = 1;

42         }

43     }

44 }

```

Veja que a variável “status” agora foi declarada como estática, pois suas modificações dentro da ISR deverão ser preservadas. Vemos ainda que no início da ISR testamos se o evento que a chamou foi realmente o EXTI13, e, caso positivo, limpa a *flag*. Essa prática de verificação é importante, uma vez que há mais de uma fonte de interrupção associada à IRQ40. A limpeza da *flag* remove a interrupção do estado pendente. Na sequência, é realizado o *toggle* do LED. Note também que não é necessário esperar o botão ser solto para terminar o processo, pois o que é testado é a transição do nível lógico baixo para o alto, e não a transição do nível alto

para baixo. A seguir, apresentamos uma implementação do arquivo “main.c” utilizando exclusivamente as macros da interface CMSIS definidas no arquivo-cabeçalho `stm32h730xxQ.h`. Vale ressaltar que as funções `NVIC_SetPriorityGrouping`, `NVIC_SetPriority` e `NVIC_EnableIRQ`, também fornecidas pela CMSIS, oferecem uma abstração de *hardware* ligeiramente superior.

```

int main(void)

{

// Ativa GPIOB (PB0) e GPIOC (PC13)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN_Msk |

RCC_AHB4ENR_GPIOCEN_Msk;

// PB0 como saída digital

GPIOB->MODER &= ~(GPIO_MODER_MODE0_Msk);

GPIOB->MODER |= GPIO_MODER_MODE0_0;

GPIOB->OTYPER &= ~GPIO_OTYPER_OT0_Msk; // PB0 como push-pull

// PC13 como entrada digital

GPIOC->MODER &= ~(GPIO_MODER_MODE13_Msk);

// Ativar o SYSCFG

RCC->APB4ENR |= RCC_APB4ENR_SYSCFGEN_Msk;

// Conectar PC3 com EXTI13

SYSCFG->EXTICR[3] &= 0xFFFFFFF0F;

SYSCFG->EXTICR[3] |= SYSCFG_EXTICR4_EXTI13_PC;

// Ativar a borda de subida e desativar borda de descida

EXTI->RTSR1 |= EXTI_RTSR1_TR13_Msk;

EXTI->FTSR1 &= ~EXTI_FTSR1_TR13_Msk;

// Desmascarar EXTI13

EXTI->IMR1 |= EXTI_IMR1_IM13_Msk;

// Ativar IRQ 40 do NVIC com prioridade 1 (macros definidos em core_cm7.h)

uint8_t prioridade = 1;

//NVIC_SetPriorityGrouping(0b11);

//Montar a palavra para escrever os bits simultaneamente

uint32_t reg_value;

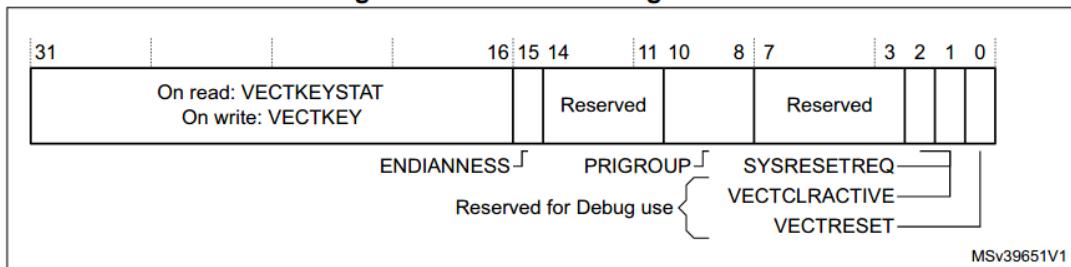

reg_value = SCB->AIRCR;

reg_value &= ~((uint32_t)(SCB_AIRCR_VECTKEY_Msk | SCB_AIRCR_PRIGROUP_Msk)); // limpar bits

reg_value = (reg_value |

((uint32_t)0x5FAUL << SCB_AIRCR_VECTKEY_Pos) |

((0b11 & (uint32_t)0x07UL) << SCB_AIRCR_PRIGROUP_Pos)); // chave e formato de agrupamento

SCB->AIRCR = reg_value;

//NVIC_SetPriority(EXTI15_10_IRQn, 1);

//Seta a prioridade nos bits [7:5] do byte de prioridade no registrador NVIC_IPRm

NVIC->IP[40]=(uint8_t)((prioridade << (8U-__NVIC_PRIO_BITS)) & (uint32_t)0xFFUL);

//NVIC_EnableIRQ(EXTI15_10_IRQn);

//Setar o bit 40%32=(40&0x01) do registrador NVIC_ISERn, onde n = 40/32 = 40<<5.

NVIC->ISER[((uint32_t)40) >> 5UL] = (uint32_t)(1UL << (((uint32_t)40) & 0x1FUL));

//Inicializa PB0 apagado

GPIOB->ODR &= ~GPIO_ODR_OD0_Msk;

/* Loop forever */

uint32_t d;

for(;;) {

```

```

// Fazendo Polling

for(d = 0; d < 16000000; d++);

}

}

```

Observe que estamos mantendo o *loop* de atraso que causava problemas no *polling*. Isso vai impactar a alternância do estado do LED verde como ocorria no projeto anterior? Além disso, note que a alternância dos estados do LED não é mais realizada dentro do laço principal. Quando ocorre essa alternância? E por qual motivo foi feita essa mudança?

Não se apavore se não conseguir responder essas perguntas ainda. Depois de aprender o mecanismo de interrupção implementada no microcontrolador STM32H7A3, você verá como elas são simples para responder.

4. Realize o *Build* e transfira o executável para o microcontrolador no modo *Debug* do programa. Expanda o item “Control” na aba SFRs para visualizar o conteúdo dos registradores VTOR e AIRCR. Em seguida, expanda o item “NVIC” e consulte o valor do byte 40%4 do registrador NVIC\_IPRn. Note que, para IRQ40, n = 40/4 = 10.

| Register     | Address    | Value      |

|--------------|------------|------------|

| Control      |            |            |

| ACTLR        | 0xe000e008 | 0x1000     |

| ICSR         | 0xe000ed04 | 0x0        |

| VTOR         | 0xe000ed08 | 0x8000000  |

| DEMCR        | 0xe000edfc | 0x10007f0  |

| AIRCR        | 0xe000ed0c | 0xfa050000 |

| VECTKEY      | [16:16]    | 0xfa05     |

| VECTKEYSTAT  | [16:16]    | 0xfa05     |

| ENDIANNESS   | [15:1]     | 0x0        |

| PRIGROUP     | [8:3]      | 0x0        |

| SYSRESETREQ  | [2:1]      | 0x0        |

| VECTCLRACTIV | [1:1]      | 0x0        |

| SCR          | 0xe000ed10 | 0x0        |

| CCR          | 0xe000ed14 | 0x40210    |

| SHBPI        | 0xe000ed18 | 0x0        |

| Register   | Address    | Value |

|------------|------------|-------|

| NVIC_IPR4  | 0xe000e410 | 0x0   |

| NVIC_IPR5  | 0xe000e414 | 0x0   |

| NVIC_IPR6  | 0xe000e418 | 0x0   |

| NVIC_IPR7  | 0xe000e41c | 0x0   |

| NVIC_IPR8  | 0xe000e420 | 0x0   |

| NVIC_IPR9  | 0xe000e424 | 0x0   |

| NVIC_IPR10 | 0xe000e428 | 0x0   |

| PRL_N3     | [24:8]     | 0x0   |

| PRL_N2     | [16:8]     | 0x0   |

| PRI_N1     | [8:8]      | 0x0   |

| PRI_NO     | [0:8]      | 0x0   |

| NVIC_IPR11 | 0xe000e42c | 0x0   |

| NVIC_IPR12 | 0xe000e430 | 0x0   |

| NVIC_IPR13 | 0xe000e434 | 0x0   |

| NVIC_IPR14 | 0xe000e438 | 0x0   |

Com base nisso, responda às seguintes perguntas depois de explorarmos os detalhes técnicos de processamento de interrupção do STM32H73A:

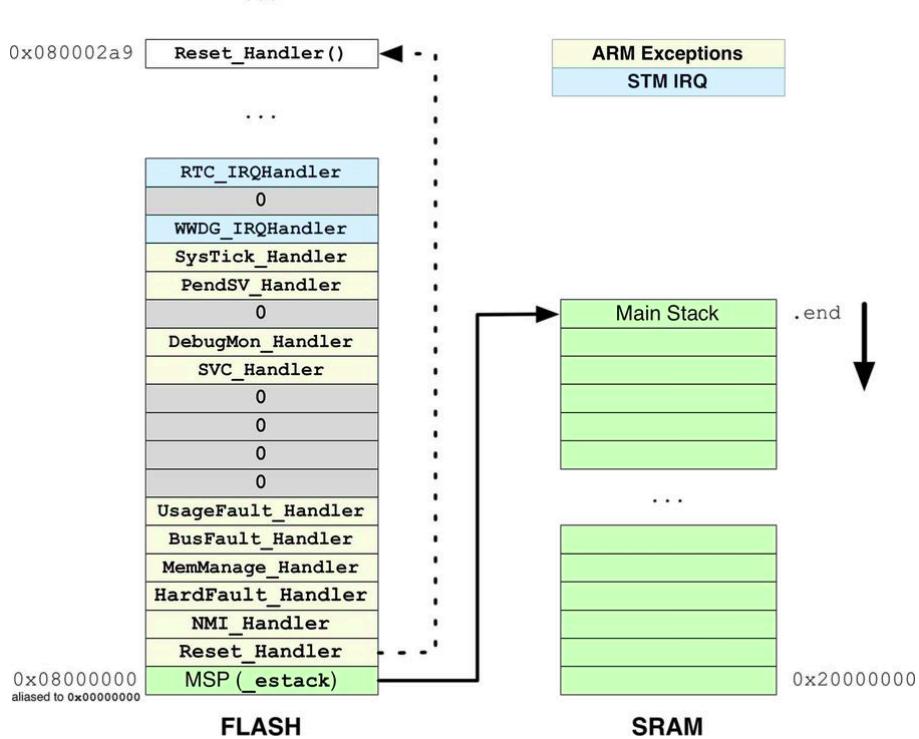

- Qual é o deslocamento em relação ao endereço-base 0x00000000 configurado para o endereço inicial da Tabela de Vetores de Interrupção?

- O endereço efetivo da Tabela de Vetores de Interrupção está condizente com o endereço onde se encontra armazenado o endereço do **Reset Handler** que é a primeira rotina de código executada após um evento de *reset*, inicializando e preparando o sistema para a operação normal?

5. Insira um *breakpoint* na linha “NVIC->IP[40]=(uint8\_t)((prioridade << (8U-\_\_NVIC\_PRIO\_BITS)) & (uint32\_t)0xFFUL);” e um *breakpoint* na linha “GPIOB->**ODR** &= ~GPIO\_ODR\_OD0\_Msk;”. Em seguida, continue (*Resume*) a execução do programa. Quando o código parar no primeiro *breakpoint*, verifique o formato de agrupamento setado no campo **PRIGROUP**. Note a instrução “SCB->**AIRCR** = reg\_value;” de atribuição direta do valor “reg\_value” no registrador SBC->AIRCR. É possível substituir pela instrução “SCB->**AIRCR** |= reg\_value;”? Sabia que essa é uma medida de segurança para proteger registradores importantes de alterações não intencionais, garantindo o funcionamento correto do sistema? Sabia que, no STM32HA3ZIT-Q, a configuração do PRIGROUP não tem efeito, uma vez que ele possui apenas 16 grupos de prioridade pré-definidos?

Continue (*Resume*) a execução do programa. Ao parar no segundo *breakpoint*, veja a prioridade setada para a linha de requisição de interrupção IRQ40 no byte menos significativo do registrador NVIC\_IPR10 e o bit 8 do registrador NVIC\_ISER1. Estão condizentes com a especificação de atribuir prioridade de IRQ40 em 1? Justifique a sua resposta, depois de entender como se programa a configuração individual da ativação e prioridade de cada linha de interrupção.

Continue (*Resume*) a execução do programa. Veja que, mesmo com o *loop* de atraso, não há mais problema no tempo de resposta ao pressionamento do botão azul. Vamos ver mais adiante a “mágica” que está por trás deste novo comportamento.

6. Uma forma eficaz de verificar a correta configuração do mecanismo de interrupção é através de um teste simples. Primeiramente, defina um *breakpoint* na primeira instrução da rotina de serviço de interrupção. Em seguida, provoque um evento que dispare a interrupção em questão. Se a execução do programa parar no *breakpoint* definido, significa que a interrupção foi configurada corretamente e o mecanismo está funcionando como esperado.

7. Ative a aba “Disassembly”, reinicie o programa e execute-o novamente. Ao parar no *breakpoint*, analise as instruções anteriores e posteriores à instrução em que o fluxo de controle parou na aba *Disassembly*. Veremos mais adiante que essas instruções definem um quadro de pilha (*stack frame*) e o *frame pointer* para os dados locais da ISR.

8. Compare o processamento do desvio de fluxo para as funções “espera” e “multiplo\_interacoes” do projeto anterior com o processamento de desvio de fluxo para uma ISR neste projeto. Analise como o desvio de fluxo é gerenciado em cada caso e veremos mais adiante por quê as ISRs não possuem argumentos.

9. Depois de você aprender o mecanismo de interrupção do STM32H73A, consegue fazer alterações neste projeto-exemplo para que o LED verde mude de estado na borda de descida do sinal em PC13 e reduzir a prioridade para 3?

10. Problemas de **reentrância** ocorrem quando uma função pode ser interrompida durante sua execução e chamada novamente antes que a primeira execução seja concluída, levando a comportamentos inesperados e difíceis de depurar. Considere a seguinte função em um cenário onde duas rotinas de serviço de interrupção (ISRs), ISR A e ISR B, chamam a mesma função:

```

void AAA () {

static uint32_t i=0;

i++;

if ( i%2 == 0 ) {

// execute instruções de A

} else {

// execute instruções de B

}

}

```

Qual seria o impacto no valor de “i” dentro da ISR A quando ela é interrompida pela ISR B que também modifica a variável “i” ao chamar a rotina AAA? Veremos mais adiante que este é um exemplo mais simples para ilustrar um problema de reentrância em um cenário de interrupção.

11. Analise o seguinte texto com base no seu entendimento de reentrância apresentada nesta apostila: “O processamento de interrupções envolve tanto *hardware* quanto *software*. O *hardware* detecta e sinaliza a interrupção, enquanto o *software* é responsável por lidar com a interrupção após sua ocorrência. Isso inclui a execução da rotina de serviço de interrupção, o chaveamento de contexto e a gestão da concorrência de recursos para garantir a integridade dos dados e do estado do sistema durante a execução do programa. Portanto, a resolução de problemas relacionados à reentrância é, predominantemente, uma questão de *design* e implementação de *software*.”

## FUNDAMENTOS TEÓRICOS

Através dos dois projetos-exemplo, mostramos que a interação de um microcontrolador com o mundo exterior se dá por meio de duas técnicas fundamentais: *polling* e interrupções. O

*polling*, comparável a um vigia constante, envolve a verificação repetida de dispositivos e pinos. Já as interrupções permitem que o microcontrolador reaja a eventos específicos sem verificações contínuas. Embora ambas sirvam ao propósito de monitorar e responder a estímulos do ambiente, elas o fazem de maneiras distintas, com implicações significativas para o desempenho e a eficiência do sistema. Para entender o funcionamento das interrupções, vamos explorar seus conceitos e fundamentos, desde o papel do *hardware* na detecção e sinalização até o *software*, responsável pelas rotinas de serviço de interrupção (ISRs) e pelo gerenciamento do contexto e das pilhas durante o processo. Com esse conhecimento, estamos prontos para configurar controladores de interrupção, implementar ISRs eficientes e integrar interrupções em projetos de sistemas embarcados, construindo sistemas mais responsivos e inteligentes.

## CARACTERÍSTICAS BÁSICAS DE SINAIS DIGITAIS

Sinais digitais são fundamentais para a comunicação e operação em sistemas digitais, desempenhando um papel crucial na troca precisa de informações. Entre as características principais que definem qualquer sinal digital, quatro aspectos básicos são essenciais para a interpretação e resposta dos sistemas digitais às mudanças no sinal, frequentemente refletindo alterações em fenômenos físicos:

**Borda de Subida:** Corresponde à transição de um nível baixo para um nível alto. Esta transição é crítica para a detecção de eventos ou a sincronização de operações. Em muitos sistemas, a borda de subida é usada para indicar o início de uma nova operação ou a ativação de um estado.

**Borda de Descida:** Corresponde à transição de um nível alto para um nível baixo. Assim como a borda de subida, a borda de descida é fundamental para detectar eventos e sincronizar atividades dentro de um sistema. Muitas vezes, é utilizada para marcar a conclusão de uma operação ou para sinalizar a desativação de um estado.

**Nível Alto:** Representa um estado em que o sinal digital está em seu valor máximo. Este nível geralmente corresponde a uma condição lógica “1”. O nível alto é frequentemente associado à ativação de funções ou à comunicação de dados importantes, servindo como um indicativo de que um sinal ou dado está presente.

**Nível Baixo:** Representa um estado em que o sinal digital está em seu valor mínimo, correspondente a uma condição lógica “0”. Este nível indica a ausência de um sinal ativo ou a desativação de uma função. O nível baixo é essencial para o reconhecimento de períodos de inatividade ou para representar a ausência de dados.

## POLLING

**Varredura** (em inglês, *polling*) é uma técnica amplamente utilizada em sistemas embarcados para verificar periodicamente o estado de um dispositivo ou recurso, com o objetivo de

determinar se ele requer atenção ou se há novos dados disponíveis. Em vez de aguardar que o dispositivo sinalize um evento, o processo de varredura envolve a consulta contínua ou periódica do estado do dispositivo. No contexto de sinais digitais, essa técnica consiste essencialmente na detecção de alterações em fenômenos físicos através de um dos quatro eventos ou estados básicos: borda de subida, borda de descida, nível alto e nível baixo.

Na prática, periféricos são projetados para detectar as mudanças nos estados físicos através da observação dos quatro eventos mencionados. A técnica de varredura simplifica a tarefa ao reduzir o problema a detectar um desses eventos específicos, amostrando periodicamente o sinal para identificá-los.

As principais vantagens da varredura incluem sua simplicidade e previsibilidade. A abordagem é fácil de implementar e não requer estruturas complexas, oferecendo um comportamento previsível no processo de verificação do estado dos dispositivos. No entanto, as desvantagens são significativas: a varredura pode ser ineficiente e introduzir latência. Isso ocorre porque o sistema gasta ciclos de processamento constantemente verificando o estado do dispositivo, mesmo quando não há mudanças, o que pode resultar em um uso ineficiente dos recursos e maior tempo de resposta para eventos importantes.

## EXCEÇÕES E INTERRUPÇÕES

A maneira mais comum de se priorizar o tratamento de um evento (como o apertar do botão) é com o uso das **interrupções**. Exceções e interrupções são mecanismos fundamentais em sistemas de computação para lidar com eventos inesperados e garantir o processamento das tarefas dedicadas ao tratamento destes eventos. Embora ambos envolvam a interrupção do fluxo normal de execução, suas formas de geração e detalhes de processamento apresentam diferenças significativas.

**Exceções** são eventos que ocorrem como resultado de condições anômalas durante a execução de um programa. Elas podem ser geradas por erros de *software*, como divisão por zero, instruções inválidas ou acesso a áreas de memória proibidas. Exceções são geralmente síncronas, ou seja, ocorrem em resposta direta a uma instrução específica que está sendo executada. Elas são intrínsecas ao processo de execução do programa e são frequentemente utilizadas para implementar mecanismos de tratamento de erros e garantir a integridade do sistema.

Por outro lado, **interrupções** são eventos assíncronos causados por fontes externas ao fluxo de execução do programa, como periféricos, temporizadores ou sinais de *hardware*. Quando um dispositivo precisa da atenção do processador, ele gera uma interrupção utilizando um dos quatro possíveis estados dos sinais digitais (bordas ou níveis). Essa interrupção sinaliza que um evento específico ocorreu, forçando o processador a interromper seu trabalho atual para tratar o evento. Isso permite que o sistema responda rapidamente a eventos externos, sem a necessidade de verificar continuamente seu estado.

Dependendo de como o processador gerencia as interrupções, elas podem ser classificadas como vetorizadas ou não-vetorizadas. Em um sistema com **interrupções vetorizadas**, cada fonte de interrupção é associada a um número de vetor. Esse número é utilizado pelo processador para localizar o endereço do manipulador (em inglês, *handler*), conhecido como rotina de serviço de interrupção (em inglês, *Interrupt Service Routine* – ISR), em uma estrutura chamada tabela de vetores de interrupção. Dessa forma, quando uma interrupção ocorre, o processador pode redirecionar o fluxo de controle diretamente para a ISR associada. Em contraste, **interrupções não-vetorizadas** não utilizam uma tabela de vetores para mapear as interrupções. Em vez disso, o processador pode precisar realizar etapas adicionais para determinar qual interrupção ocorreu e qual ISR deve ser executada, o que pode envolver verificações adicionais e processamento mais complexo para identificar a origem da interrupção e seu tratamento adequado.

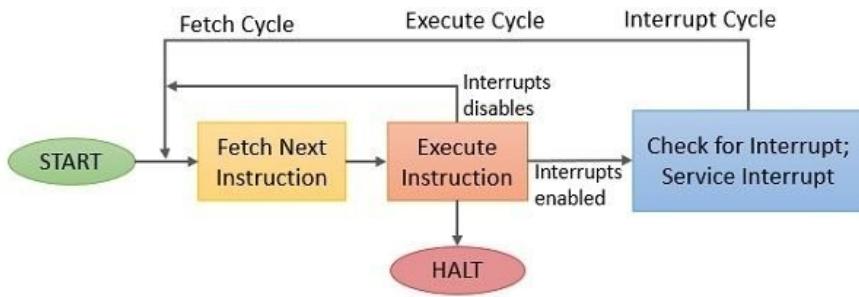

Quando a ISA adota uma abordagem de interrupção vetorizada, como a arquitetura ARM, exceções e interrupções, apesar de suas diferenças em origem e natureza, compartilham semelhanças no processamento e podem ser tratadas de maneira uniforme. Cada evento é associado a um **número de vetor** específico. Quando uma exceção ou interrupção ocorre, o tratamento segue um ciclo padronizado dentro do [ciclo de instrução com interrupção](#).

**Instruction Cycle with Interrupts**

A arquitetura ARM explora as características básicas dos sinais digitais, distinguindo interrupções sensíveis ao nível e de pulso. As **interrupções de pulso** também são descritas como interrupções acionadas por borda. Uma interrupção sensível ao nível é mantida ativa até que o periférico desative o sinal de interrupção. Normalmente isso acontece quando a ISR acessa o periférico, fazendo com que ele remova a *flag* de solicitação de interrupção. Uma interrupção de pulso é um sinal de interrupção amostrado de forma síncrona na borda do sinal de *clock* do processador. Para garantir que o processador detecte a interrupção de pulso, o periférico deve ativar o sinal de interrupção por pelo menos um ciclo de relógio, durante o qual o processador detecta o pulso e trava a interrupção.

Quando o processador entra na ISR, ele remove automaticamente o estado pendente da interrupção, como descreve o [Manual de Programação](#). Para uma **interrupção sensível ao nível**, se nível do sinal não for desativado antes do processador retornar da ISR, o processador deve executar sua ISR novamente. Isso significa que o periférico pode reter o sinal de interrupção ativado até que ele não precise mais de atendimento. Para uma interrupção acionada por borda, o sinal de interrupção é continuamente monitorado mesmo

estando em execução a ISR. Assim, quando um pulso é detectado, a solicitação é ativada e, ao retornar de uma ISR, o processador re-entra na ISR se não houver outras solicitações prioritárias.

## Ciclo de Interrupção

O ciclo de interrupção/exceção consiste dos seguintes passos:

**Interrupção do Fluxo Normal de Execução:** O processador desvia temporariamente do código em execução para tratar o evento, seja ele uma condição de erro ou uma sinalização de *hardware*.

**Uso de Tabela de Vetores de Interrupção:** Quando uma exceção ou interrupção ocorre, a tabela de vetores de interrupção é utilizada pelo processador para localizar o endereço da ISR correspondente e redireciona o fluxo de execução para esse endereço. A ISA especifica não apenas a presença e a organização dos endereços das ISRs na tabela, mas também a localização desta tabela na memória.

Para processadores baseados na arquitetura ARM Cortex-M, o endereço-padrão da tabela de vetores é o início da memória de instrução, que geralmente é 0x00000000. No entanto, no núcleo Cortex-M7 do microcontrolador STM32H7A3ZIT6-Q, a tabela de vetores é mapeada para o endereço 0x08000000 no espaço de endereçamento do processador através do registrador [VTOR](#), como ilustra a figura a seguir. Assim, a referência ao endereço 0x08000000 como o local da tabela de vetores é específica para essa configuração de mapeamento de memória e reflete a forma como a memória FLASH é mapeada neste microcontrolador.. Para mais detalhes sobre a organização da tabela, consulte o [Manual de Referência](#). Observe que as 16 primeiras entradas da tabela de vetores são reservadas para exceções, enquanto as 155 subsequentes são destinadas a interrupções.

**Salvamento do Contexto e Estado:** Antes de transferir o controle para a ISR, o processador salva automaticamente o estado atual do programa, incluindo o contador de programa (PC) e outros registradores, em uma pilha. Isso assegura que o fluxo de execução possa ser retomado corretamente após o tratamento da interrupção. Na arquitetura ARM, é chamada essa transferência de controle de chaveamento de contexto (do inglês *context switching*) do fluxo de controle atual, seja do modo Thread ou do modo Handler, para um novo fluxo de controle sempre do modo Handler. Para garantir a integridade do fluxo de controle neste chaveamento, o compilador e o ligador geram o código necessário para realizar as seguintes tarefas conforme as convenções e requisitos da arquitetura ARM ao compilar uma função que define uma ISR:

- finalizar a execução da instrução corrente,

- salvar na pilha os registradores de [AAPCS](#) (do inglês *ARM Architecture Procedure Call Standard*): R0, R1, R2, R3, R12, LR, PC, [APSR](#) (do inglês *Application Program Status Register*), que contém as *flags* de ALU necessárias para desvios condicionais e operação de algumas instruções, [IPSR](#) (do inglês *Interrupt Program Status Register*), que contém o número de vetor, e os registradores de FPUs,

- setar o registrador de retorno LR (do inglês *Link Register*) ou R14, com o valor de retorno da exceção, EXEC\_RETURN.

- atualizar o registrador de estado [IPSR](#) com o número de exceção do novo contexto, e

- carregar no PC (*Program Counter*) ou R15, que mantém o endereço da próxima instrução, o endereço da ISR armazenado na Tabela de Vetores de Interrupção.

**Execução de Código de Tratamento:** Tanto exceções quanto interrupções são tratadas por um código específico definido em uma ISR. Esse código é responsável por resolver a condição que causou a exceção ou responder ao evento de *hardware*, garantindo que o

sistema possa continuar funcionando corretamente.

As definições de ISRs e os endereços das suas instruções na memória são fortemente dependentes do aplicativo em desenvolvimento. Cada ISR deve ser implementada conforme as necessidades específicas do aplicativo, e os endereços dessas rotinas na tabela de vetores de interrupção precisam ser configurados para refletir corretamente onde cada ISR está localizada na memória. Para facilitar o desenvolvimento e reduzir a complexidade associada ao gerenciamento manual desses endereços, o STM32CubeIDE oferece uma funcionalidade prática. Em vez de exigir que o desenvolvedor configure manualmente os endereços das ISRs, o STM32CubeIDE cria o arquivo `Startup/startup_stm32h7a3zitxq.s` que contém a tabela de vetores de interrupção inicialmente preenchida com símbolos no lugar de endereços específicos das ISRs:

```

.section .isr_vector, "a",%progbits

.type g_pfnVectors, %object

g_pfnVectors:

.word _estack

.word Reset_Handler

.word NMI_Handler

.word HardFault_Handler

.word MemManage_Handler

.word BusFault_Handler

.word UsageFault_Handler

.word @

.word @

.word @

.word @

.word SVC_Handler

.word DebugMon_Handler

.word @

.word PendSV_Handler

.word SysTick_Handler

.word WWDG_IRQHandler

.word PVD_PVM_IRQHandler

.word RTC_TAMP_STAMP_CSS_LSE_IRQHandler

.word RTC_WKUP_IRQHandler

.word FLASH_IRQHandler

.word RCC_IRQHandler

.word EXTI0_IRQHandler

.word EXTI1_IRQHandler

.word EXTI2_IRQHandler

.word EXTI3_IRQHandler

.word EXTI4_IRQHandler

.word DMA_STR0_IRQHandler

.word DMA_STR1_IRQHandler

.word DMA_STR2_IRQHandler

.word DMA_STR3_IRQHandler

.word DMA_STR4_IRQHandler

.word DMA_STR5_IRQHandler

.word DMA_STR6_IRQHandler

.word ADC1_2_IRQHandler

.word FDCAN1_IT0_IRQHandler

/* Window Watchdog interrupt */

/* PVD through EXTI line */

/* RTC tamper, timestamp */

/* RTC Wakeup interrupt */

/* Flash memory global interrupt */

/* RCC global interrupt */

/* EXTI Line 0 interrupt */

/* EXTI Line 1 interrupt */

/* EXTI Line 2 interrupt */

/* EXTI Line 3interrupt */

/* EXTI Line 4interrupt */

/* DMA1 Stream0 global interrupt */

/* DMA1 Stream1 global interrupt */

/* DMA1 Stream2 global interrupt */

/* DMA1 Stream3 global interrupt */

/* DMA1 Stream4 global interrupt */

/* DMA1 Stream5 global interrupt */

/* DMA1 Stream6 global interrupt */

/* ADC1 and ADC2 global interrupt */

/* TTCAN Interrupt 0 */

```

O desenvolvedor pode então implementar as ISRs como funções C normais, utilizando os mesmos símbolos especificados na tabela de vetores para garantir consistência. Por exemplo, se a ISR para o módulo “SysTick” é definida como “`SysTick_Handler`”, o código pode ser escrito da seguinte forma:

```

void SysTick_Handler(void) {

//código de tratamento de interrupção

}

```

Durante o processo de vinculação, o ligador GNU do STM32CubeIDE localiza as definições das funções ISR no código e associa essas definições aos símbolos listados na tabela de vetores de interrupção. Ele então resolve as referências a esses símbolos, substituindo-os pelos endereços efetivos das funções ISR no programa final. Isso garante que a tabela de vetores contenha os endereços corretos para que, quando uma interrupção ocorre, o processador possa redirecionar o fluxo de execução para a ISR apropriada.

O STM32CubeIDE também trata a situação em que uma definição de ISR está ausente para um evento de interrupção específico, fornecendo uma função padrão chamada “Default\_Handler” no mesmo arquivo “Startup/startup\_stm32h7a3zitxq.s”.

```

/*********************************************

*

* Provide weak aliases for each Exception handler to the Default_Handler.

* As they are weak aliases, any function with the same name will override

* this definition.

*

********************************************/

.weak    NMI_Handler

.thumb_set NMI_Handler,Default_Handler

.weak    HardFault_Handler

.thumb_set HardFault_Handler,Default_Handler

.weak    MemManage_Handler

.thumb_set MemManage_Handler,Default_Handler

.weak    BusFault_Handler

.thumb_set BusFault_Handler,Default_Handler

.weak    UsageFault_Handler

.thumb_set UsageFault_Handler,Default_Handler

.weak    SVC_Handler

.thumb_set SVC_Handler,Default_Handler

.weak    DebugMon_Handler

.thumb_set DebugMon_Handler,Default_Handler

.weak    PendSV_Handler

.thumb_set PendSV_Handler,Default_Handler

.weak    SysTick_Handler

.thumb_set SysTick_Handler,Default_Handler

.weak    WWDG_IRQHandler

.thumb_set WWDG_IRQHandler,Default_Handler

```

A função de substituição “Default\_Handler” é automaticamente utilizada pelo sistema para lidar com interrupções para as quais não há um manipulador definido, garantindo que o sistema tenha uma resposta predefinida e evitando possíveis falhas ou comportamentos indefinidos.

```

/*

* @brief This is the code that gets called when the processor receives an

* unexpected interrupt. This simply enters an infinite loop, preserving

* the system state for examination by a debugger.

*

* @param None

* @retval : None

*/

.section .text.Default_Handler,"ax",%progbits

Default_Handler:

Infinite_Loop:

b Infinite_Loop

.size Default_Handler, .-Default_Handler

```

É importante notar que **as ISRs não recebem argumentos**. Isso ocorre porque elas são chamadas diretamente pelo *hardware* em resposta a eventos específicos, sem que o *software* tenha controle sobre o momento da chamada ou os dados que podem ser passados para a rotina. A comunicação entre a ISR e o restante do código geralmente é feita através de variáveis globais ou *flags*, que permitem que a ISR sinalize eventos ou compartilhe dados com outras partes do programa.

**Retorno ao Fluxo Normal:** Após o tratamento da exceção ou interrupção, o processador restaura o estado salvo do programa e retoma a execução do código no ponto em que foi interrompido usando o retorno de exceção. Como **o tratamento de exceção ocorre no modo Handler**, há três tipos de retorno, indicado pelo valor EXEC\_RETURN: para modo *Handler*, para modo *Thread* privilegiado ou para modo *Thread* não-privilegiado. O valor EXEC\_RETURN é carregado no LR na entrada da exceção.

| EXC_RETURN Behavior |                                                                                                                              |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|

| 0xFFFFFFF1          | Return to Handler Mode.<br>Exception return gets state from the Main stack.<br>On return execution uses the Main Stack.      |

| 0xFFFFFFFF9         | Return to Thread Mode.<br>Exception return gets state from the Main stack.<br>On return execution uses the Main Stack.       |

| 0xFFFFFFFFD         | Return to Thread Mode.<br>Exception return gets state from the Process stack.<br>On return execution uses the Process Stack. |

| Unused              | Reserved.                                                                                                                    |

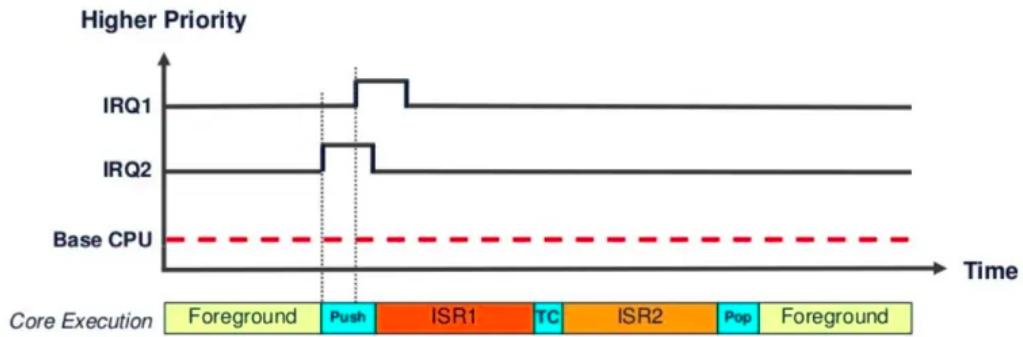

## Prioridade de Atendimento

As interrupções/exceções permitem que o microcontrolador responda imediatamente os

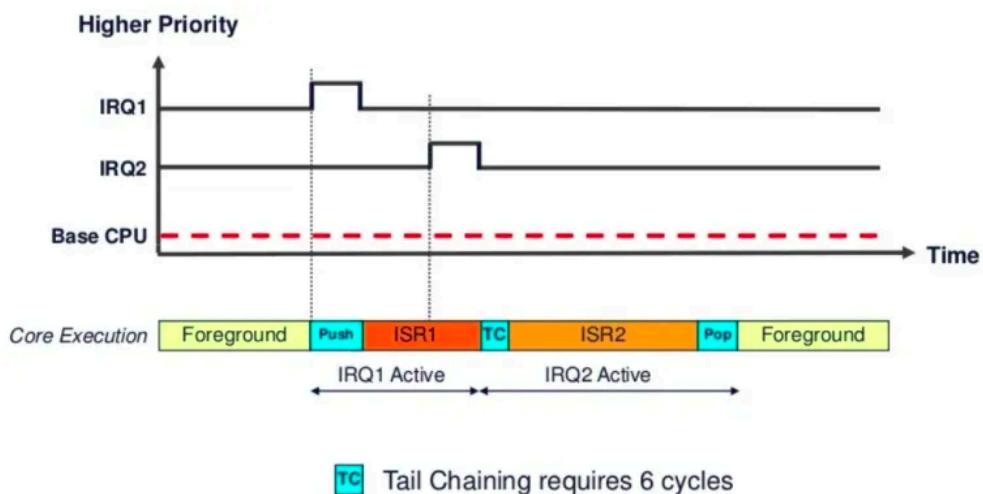

eventos externos/internos do processador, suspendendo temporariamente a execução do fluxo de controle principal (núcleo) para lidar com uma situação emergente. No entanto, quando múltiplas interrupções ocorrem simultaneamente ou em rápida sucessão, é necessário garantir que eventos sejam atendidos pelo processador na ordem dos seus níveis de criticidade ou de prioridade. Portanto, existem dois conceitos fundamentais em interrupções que o programador deve ter em mente: preempção e prioridade. A **preempção** se refere à capacidade do sistema de interromper a execução de uma tarefa para que uma tarefa mais importante ou urgente possa ser executada, o que é realizado através das interrupções. A **prioridade** de interrupção determina a ordem de importância das interrupções. Em um sistema onde múltiplas interrupções podem ocorrer, a cada uma é atribuída um nível de prioridade. Interrupções com prioridade mais alta podem interromper aquelas com prioridade mais baixa.

Atualmente, praticamente todos os processadores provêm níveis de prioridade de interrupção para gerenciar de forma eficiente as interrupções que ocorrem no sistema. O nível de prioridade de uma ISR em execução é setado como a **prioridade de execução** do processador. Enquanto esta ISR estiver executando, existem duas abordagens para lidar com a ocorrência de interrupções de prioridade maior: a técnica de interrupções aninhadas e a técnica de interrupções não-aninhadas. Em sistemas com **interrupções não-aninhadas**, uma vez que uma interrupção começa a ser atendida, nenhuma outra interrupção pode interrompê-la até que o atendimento seja concluído. As interrupções são atendidas em uma ordem sequencial, conforme o nível de prioridade configurado enquanto não houver nenhuma ISR em execução. As **interrupções aninhadas** permitem, por sua vez, que uma interrupção em andamento seja interrompida por outra interrupção de prioridade maior do que a prioridade da interrupção em execução. Assim, o sistema pode responder imediatamente a eventos mais críticos, mesmo que uma interrupção de menor prioridade esteja sendo atendida.

Para tratamento de interrupções aninhadas, o *software* deve estar preparado para aceitar outra interrupção/exceção, mesmo antes de terminar de tratar a interrupção/exceção atual. Vale a pena ressaltar que o tratamento de interrupções aninhadas é uma escolha feita pelo *software*, em função da configuração da prioridade de interrupção e do controle de interrupção ajustada pelo desenvolvedor conforme as necessidades específicas das aplicações. Ela não é imposta pelo *hardware*.

Uma consideração crucial nesse contexto é a diferença entre subrotinas aninhadas e subrotinas reentrantes para processamento de interrupções. **Subrotinas aninhadas** se referem a funções que podem chamar outras funções, inclusive aquelas que podem estar em execução simultaneamente. Isso pode complicar o controle do fluxo de execução e a manutenção do estado, especialmente quando se trata de interrupções aninhadas, onde uma interrupção pode chamar outra antes que a primeira tenha sido completamente tratada.

**Subrotinas reentrantes**, por outro lado, são projetadas para serem seguras para chamadas simultâneas. Isso significa que uma subrotina reentrante pode ser interrompida no meio de sua execução e, posteriormente, ser chamada novamente antes que a execução anterior seja

concluída. A subrotina deve então ser capaz de retomar a execução de maneira correta e segura sem corromper os dados ou falhar na execução. Esse comportamento é essencial para o tratamento eficaz de interrupções, especialmente em sistemas multitarefa e sistemas embarcados, onde a reentrância pode permitir que múltiplos eventos sejam gerenciados de forma eficiente.

Os problemas desafiadores de reentrância incluem garantir que todas as variáveis usadas em uma subrotina reentrante sejam locais ou devidamente protegidas contra **condições de corrida** (em inglês *race conditions*) e corrupções de dados. Além disso, o uso de recursos compartilhados, como *buffers* de dados e variáveis globais, precisa ser cuidadosamente sincronizado para evitar inconsistências. Desenvolvedores enfrentam o desafio de implementar mecanismos para proteger esses recursos e garantir que as subrotinas possam ser interrompidas e retomadas sem problemas.

Portanto, embora o tratamento de interrupções aninhadas e a configuração de prioridade por *hardware* proporcionem flexibilidade no gerenciamento de eventos, a implementação de subrotinas reentrantes pelo desenvolvedor é essencial para assegurar a robustez e a confiabilidade de sistemas em ambientes altamente concorrentes e de alta prioridade. A capacidade de gerenciar interrupções de maneira segura e eficiente é um aspecto crítico do desenvolvimento de um sistema embarcado. Isso exige um domínio profundo tanto do cenário de concorrência quanto das técnicas de programação, para alcançar um equilíbrio cuidadoso entre flexibilidade, desempenho e segurança.

Idealmente, uma interrupção aninhada deve ser reentrante, o que significa que o sistema deve preservar a integridade dos dados e do estado para permitir que uma ISR suspensa retome sua execução a partir do ponto em que foi interrompida, após a conclusão da ISR de maior prioridade. De acordo com o [Manual da ARM](#), para garantir que uma ISR reentrante possa lidar corretamente com interrupções aninhadas, é essencial salvar o estado atual da interrupção, proteger os recursos compartilhados, identificar corretamente as fontes de interrupção e gerenciar as *flags* de interrupção de maneira eficaz.

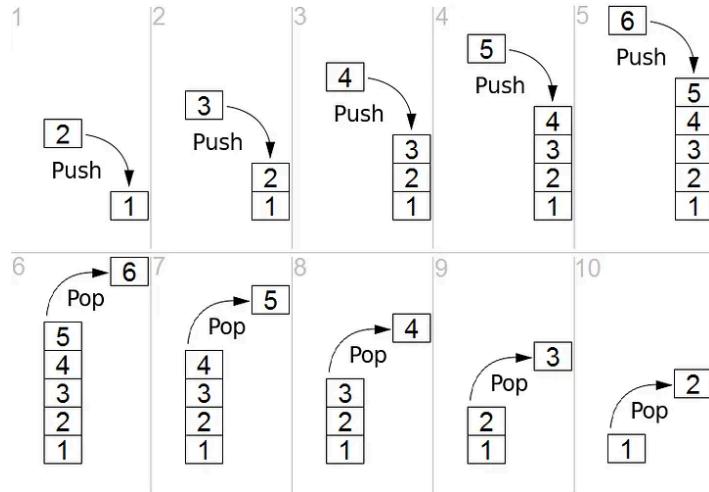

## ESTRUTURA DE DADOS: PILHAS

A pilha é um subespaço contíguo da memória destinada ao armazenamento de dados temporários. O acesso à pilha é feito no modo *Last In, First Out* (LIFO) onde o último dado inserido é o primeiro a ser removido. Duas operações são associadas a essa estrutura de dados: **empilhar** (do inglês *push*) um novo elemento sobre o topo e **desempilhar** (do inglês *pop*) do topo um elemento. O endereço do topo é armazenado numa variável para facilitar o seu processamento. Hoje em dia todos os processadores suportam a implementação de pilhas, provendo o registrador denominado **ponteiro de pilha SP** (do inglês *stack pointer*), e instruções de empilhamento e desempilhamento, como as instruções [PUSH](#) e [POP](#), além de operações de memória como LDR e STR.

Existem convenções de gerenciamento de pilha, como ilustra a [figura](#). Na **pilha ascendente** (em inglês, *full ascending stack*), a memória é alocada em direção ao alto endereço (ou seja, os endereços de memória aumentam conforme mais dados são empilhados). Ao adicionar um novo item à pilha, você move o ponteiro da pilha para um endereço de memória maior. Na **pilha descendente** (em inglês, *full descending stack*), a memória é alocada em direção ao baixo endereço (ou seja, os endereços de memória diminuem conforme mais dados são empilhados). Ao adicionar um novo item à pilha, você move o ponteiro da pilha para um endereço de memória menor. Na arquitetura ARM, a abordagem padrão é usar uma pilha descendente. Ou seja, a pilha começa em um endereço alto e cresce em direção a endereços baixos.

A pilha é fundamental para operações como chamadas de funções e o tratamento de interrupções ou exceções. Para uma implementação detalhada e completa dessa estrutura em C, consulte o artigo disponível no [GeeksForGeeks](#).

De acordo com a AAPCS (do inglês *ARM Architecture Procedure Call Standard*), os primeiros quatro parâmetros são passados nos registradores r0 a r3. Parâmetros adicionais são passados na pilha. Por exemplo, para a função, os parâmetros “a”, “b”, “c” e “d” são passados nos registradores r0, r1, r2 e r3, enquanto os parâmetros “e” e “f” são empilhados e acessados na função “Exemplo 1” via pilha:

```

void Exemplo 1 (int a, int b, int c, int d, int e, int f) {

// Código da função

}

```

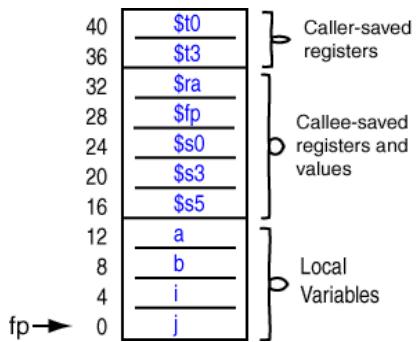

A pilha é amplamente utilizada para armazenar variáveis locais em uma função devido à sua capacidade de alocar e desalocar memória de forma rápida e eficiente. Como parte do processo de chamada de uma função, o compilador de C gera as instruções necessárias para salvar e restaurar o estado dos registradores na pilha, como também para reservar o espaço para as variáveis locais na pilha. A [figura](#) ilustra o empilhamento dos registradores que a função chamadora precisa preservar (em inglês *caller-saved registers*), registradores que a função chamada precisa preservar (em inglês *callee-saved registers and values*) e variáveis locais (em inglês *local variables*) da função chamada, realizado por essas funções.

É comum denominar de **quadro da pilha** (em inglês *stack frame*) o bloco de memória da pilha reservado para processamento de uma função chamada. Define-se ainda como **ponteiro do quadro** (em inglês *frame pointer*) um endereço-base, tipicamente o topo da pilha. Assim, as instruções da função chamada podem acessar todos os seus dados pré-empilhados usando deslocamentos fixos em relação ao ponteiro do quadro fp, ao invés de variar o ponteiro da pilha SP, empilhando e desempilhando as variáveis locais na execução das instruções. Ao final da função, basta desempilhar o quadro para restaurar o estado da pilha antes da chamada da função. O registrador r7 é tipicamente utilizado como ponteiro de quadro.

A menos das operações dedicadas à transferência de operandos entre o processador e a memória, todas as instruções da arquitetura ARM envolvem somente os registradores. Como são poucos os registradores quando o processador executa no modo Thumb, a pilha é também muito utilizada para salvar e restaurar os valores dos registradores.

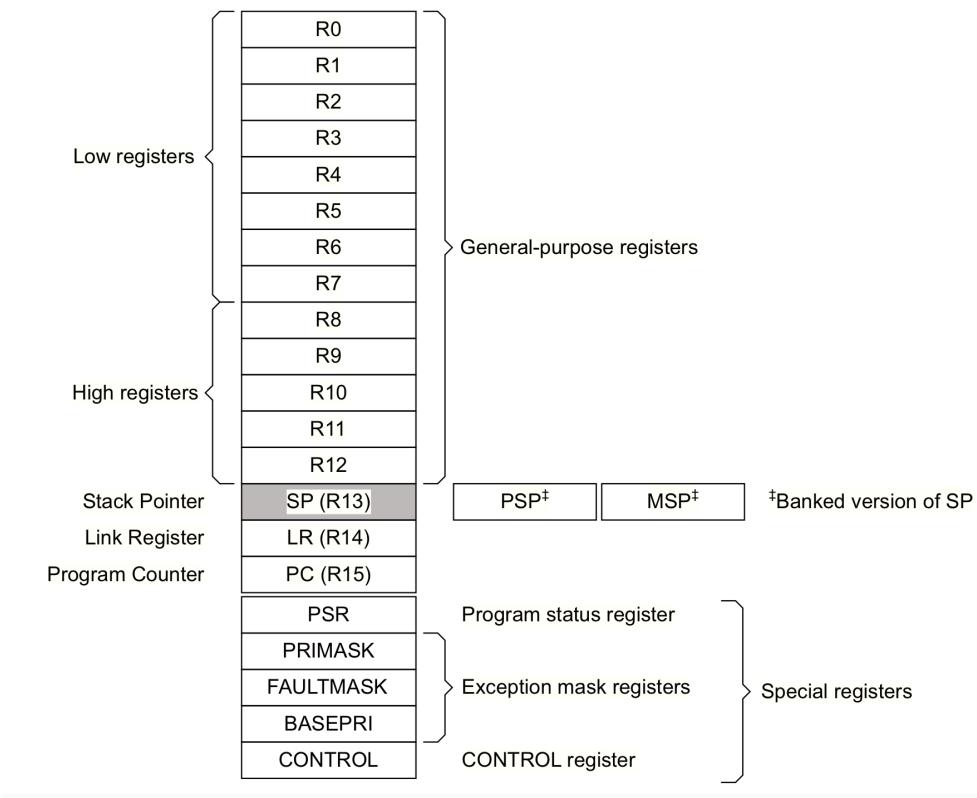

Os processadores ARM Cortex-M são equipados de *hardware* de **ponteiro de pilha dedicado (R13)** para operações de pilha. Eles possuem uma instrução PUSH para armazenar dados na pilha e uma instrução POP para recuperar dados. O ponteiro de pilha atualmente selecionado é ajustado automaticamente para cada operação PUSH e POP. Como a arquitetura ARM usa uma pilha descendente, o ponteiro da pilha sempre aponta para os últimos dados armazenados na memória da pilha e o ponteiro da pilha pré-decrementa para cada nova operação PUSH.

O STM32H7A3ZIT6-Q mantém, em particular, dois ponteiros de pilha:

**MSP** (do inglês *Main Stack Pointer*) é o ponteiro-padrão, configurado durante a inicialização do sistema e usado sempre no modo Handler e no modo Thread supervisor. Sua alteração é menos comum e geralmente feita apenas em configuração inicial ou em situações onde é necessário alterar o comportamento do sistema de exceções.