# **DISCIPLINA EA701**

## **Introdução aos Sistemas Embarcados**

### **ROTEIRO 4: Organização de Memória e Tipos de Dados em C**

**TECNOLOGIAS DE MEMÓRIA, ALINHAMENTO E

ORDENAÇÃO DE *BYTES*, MAPA E SEGMENTAÇÃO DE

MEMÓRIA, MEMÓRIA CACHE E MEMÓRIA FORTEMENTE

ACOPLADA (TCM), SISTEMA DE MEMÓRIA NO

STM32H7A3ZIT6-Q, TIPOS DE DADOS EM C.**

**Profs. Antonio A. F. Quevedo e Wu Shin-Ting**

**FEEC / UNICAMP**

**Revisado em fevereiro de 2025 por Ting com auxílio do Chatgpt**

**Revisado em agosto de 2024**

This work is licensed under Creative Commons

Attribution-NonCommercial-ShareAlike 4.0 International. To view a copy of this

license, visit <https://creativecommons.org/licenses/by-nc-sa/4.0/>

|                                                                           |           |

|---------------------------------------------------------------------------|-----------|

| <b>INTRODUÇÃO</b>                                                         | <b>2</b>  |

| <b>UM PROJETO-EXEMPLO PARA EXPLORAR MEMÓRIA</b>                           | <b>3</b>  |

| <b>FUNDAMENTOS TEÓRICOS</b>                                               | <b>13</b> |

| TECNOLOGIAS DE MEMÓRIA: PROM, EPROM, EEPROM, FLASH NAND, NOR, SRAM e DRAM | 13        |

| MAPA DE MEMÓRIA                                                           | 19        |

| ALINHAMENTO DE DADOS                                                      | 21        |

| ORDENAÇÃO DOS BYTES                                                       | 23        |

| SEGMENTAÇÃO DE MEMÓRIA PRINCIPAL                                          | 23        |

| MEMÓRIA CACHE                                                             | 26        |

| MEMÓRIA FORTEMENTE ACOPLADA (TCM)                                         | 30        |

| <b>SISTEMA DE MEMÓRIA NO STM32H7A3</b>                                    | <b>30</b> |

| <b>TIPOS DE DADOS EM C</b>                                                | <b>32</b> |

## INTRODUÇÃO

A memória é um componente fundamental em todos os sistemas computacionais. Nela são armazenadas as instruções a serem executadas (código), bem como os valores de variáveis (dados) usados pelo programa. Os microcontroladores costumam ter a memória incluída no *chip*, e alguns deles ainda permitem configurar parte de seus pinos para acesso a componentes de memória externos aos mesmos.

Os dois tipos de memória mais usados em microcontroladores são a tecnologia FLASH e a SRAM. A memória FLASH é uma memória não-volátil (preserva o conteúdo mesmo sem energia) que pode ser apagada e gravada em blocos, e é normalmente usada para armazenar de forma semi-permanente o código a ser executado, ao mesmo tempo permitindo que o código seja modificado e regravado a partir de fontes externas, um processo que acontece rotineiramente em atualizações de *firmware* nos equipamentos. A memória SRAM, ou RAM estática, é uma memória volátil (perde os dados ao ser retirada a energia) com um custo e tamanho maiores que os da memória DRAM (RAM dinâmica), porém de maior velocidade e sem depender de um controlador específico. Para quantidades de memória RAM não muito grandes, como é comum em microcontroladores, a SRAM é ideal. Esta memória é normalmente usada para armazenar os valores de variáveis, na forma de alocação estática, *heap* ou *stack*, dependendo do tipo de informação armazenada.

Um fator que determina o uso de certos tipos de memória é sua velocidade. A memória SRAM é mais rápida que a FLASH para a leitura. Sistemas computacionais de maior porte costumam carregar uma cópia da parte do código em uma memória SRAM dedicada para acesso mais rápido, sendo esta memória denominada **memória cache**. Apesar de não ser tão comum em sistemas microcontrolados, alguns microcontroladores, como o STM32H7A3ZIT6-Q, possuem *cache* para otimizar a velocidade de execução. Entretanto, o

gerenciamento desta memória é algo bastante complexo. A **TCM** (do inglês *Tightly Coupled Memory*) é mais comumente encontrada em microcontroladores e sistemas embarcados, onde a proximidade e a alta velocidade de acesso são essenciais para o desempenho de tarefas específicas. Esta memória especial é projetada para operar extremamente próxima ao processador, oferecendo latências muito baixas e alta largura de banda.

Neste roteiro, veremos a organização dos diferentes tipos de memória, bem como seu uso pelos diversos tipos de dados.

## UM PROJETO-EXEMPLO PARA EXPLORAR MEMÓRIA

Já se perguntou o que acontece nos bastidores quando um computador executa uma tarefa? Sabemos que ele possui um sistema de memória onde são armazenadas as instruções para o processador gerar sinais de controle que manipulam os dados. Mas já imaginou como informações tão diversas, como instruções de programas, textos, números naturais, inteiros e reais, encontram seu lugar nesse sistema? Onde ficam armazenadas as instruções dos programas nos microcontroladores para garantir que o processador execute tudo com precisão e velocidade assim que é energizado? E mais, como podemos tirar proveito da proximidade da linguagem C do *hardware* para instruir um processador como organizar e armazenar dados de forma eficiente. Vamos iniciar a especificação do uso de um sistema de memória com o seguinte projeto-exemplo.

1. Crie um projeto denominado “Memoria”, da mesma forma que foi feito nos roteiros anteriores. Apague o código-fonte do arquivo “main.c” e o preencha com o seguinte código:

```

#include <stdint.h>

#include <malloc.h>

#include <string.h>

// Variaveis Globais inicializadas, armazenadas no segmento "data"

uint8_t global_var1 = 42;

// Variaveis Globais Não-inicializadas, armazenadas no segmento "BSS"

uint32_t uninitialized_var1;

// Variaveis constantes, armazenadas no segmento Rodata (FLASH)

const uint32_t const_var1 = 100;

// Variavel para demonstrar alocacao no "heap" e strings

char *heap_var;

// Outras variaveis a serem usadas na demonstracao

uint8_t *usig;

int16_t *sig;

int16_t k;

// Funcao para demonstrar o uso de qualificador register e static

uint32_t reg_demo(uint32_t v) {

//Var local

uint16_t reg_local;

```

```

// Var local com qualificador register

register uint32_t reg_var;

// Variaveis estaticas, armazenadas no segmento "data"

static uint8_t reg_static_var1 = 10;

reg_local = const_var1;

reg_var = v + 1;

reg_static_var1++;

if (reg_static_var1 == 0xff) reg_static_var1 = 0;

return reg_var;

}

volatile uint32_t *RCC_AHB4ENR = ((uint32_t *)0x58024540);

volatile uint32_t *GPIOB_MODER = ((uint32_t *)0x58020400);

volatile uint32_t *GPIOB_OTYPER = ((uint32_t *)0x58020404);

volatile uint32_t *GPIOB_ODR = ((uint32_t *)0x58020414);

#define ITERACOES 5000

int main(void)

{

struct mallinfo mi;

uint32_t i;

float *fp;

float x;

// Aloca 100 bytes para o vetor heap_var com 100 elementos do tipo

// char. Observe a conversao explicita de tipo de retorno "void"

// da funcao malloc para "char *"

heap_var = (char *)malloc(sizeof(char) * 100);

// Atribuir 200 a heap_var[0] que é equivalente a *heap_var

*heap_var = 200;

// Ler a informacao sobre alocacao de memoria

mi = mallinfo();

global_var1++;

uninitialized_var1 = 5;

//const_var1++;

global_var1 = reg_demo(10);

// A funcao copia a segunda string na primeira

// Por padrao, as variaveis processadas pelas funcoes da biblioteca

// "string" sao do tipo "char"

strcpy(heap_var, "This is a NULL-terminated String");

// Muda o espaco alocado

// Observe a conversao explicita do tipo de variavel heap_var

heap_var = (char *)realloc(heap_var, sizeof(uint8_t) * 200);

mi = mallinfo();

usig = (uint8_t *)0xAABBCCDD;

sig = &k;

k = -10;

fp = &x;

*fp = 3.375;

*RCC_AHB4ENR = *RCC_AHB4ENR | 0x00000002;

*GPIOB_MODER = ((*GPIOB_MODER | 0x00000001) & 0xFFFFFFFF);

*GPIOB_OTYPER = *GPIOB_OTYPER & 0xFFFFFFFF;

for(;;) {

*GPIOB_ODR = *GPIOB_ODR & 0xFFFFFFFF; //PB0 = 0;

for (i=0; i<ITERACOES; i++); // Espera

}

}

```

```

*GPIOB_ODR |= *GPIOB_ODR | 0x00000001; //PB0 = 1;

for (i=0; i<ITERACOES; i++); // Espera

}

}

```

Observe o uso do tipo de dado “struct mallinfo”. Este tipo de dado é fornecido por algumas implementações da biblioteca padrão de alocação dinâmica de memória, como a *GNU C Library* (glibc). Ele é utilizado para fornecer informações sobre a alocação de memória em um programa que usa a função “malloc”, por meio da chamada da função “mallinfo()”. Para que o compilador possa utilizar o tipo de dado “struct mallinfo” e a função “mallinfo()”, é necessário incluir o arquivo de cabeçalho “malloc.h” no código-fonte com a diretiva “#include <malloc.h>”.

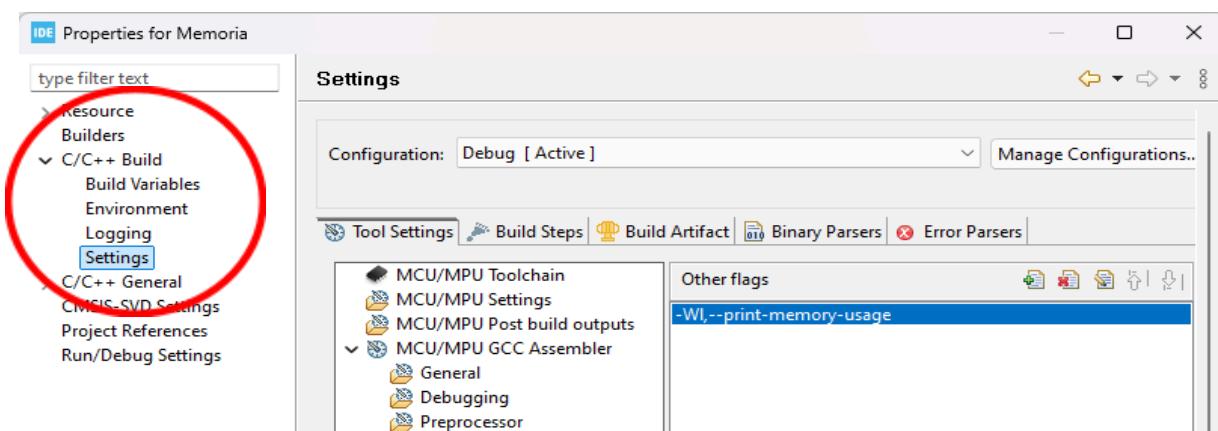

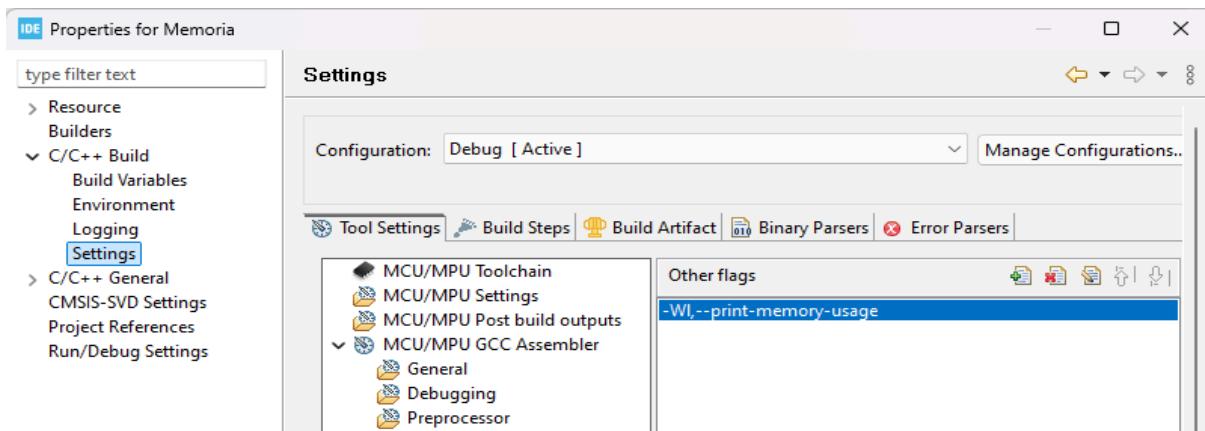

2. Para podermos analisar o uso da memória pelo programa em diferentes estágios de ligação, vamos ativar a exibição de estatísticas sobre o uso de memória do ligador. Com o projeto selecionado no “Project Explorer”, siga o caminho do menu principal “Project > Properties” e selecione “Properties”. No painel à esquerda da janela que se abre, expanda a opção “C/C++ Build” e selecione “Settings”.

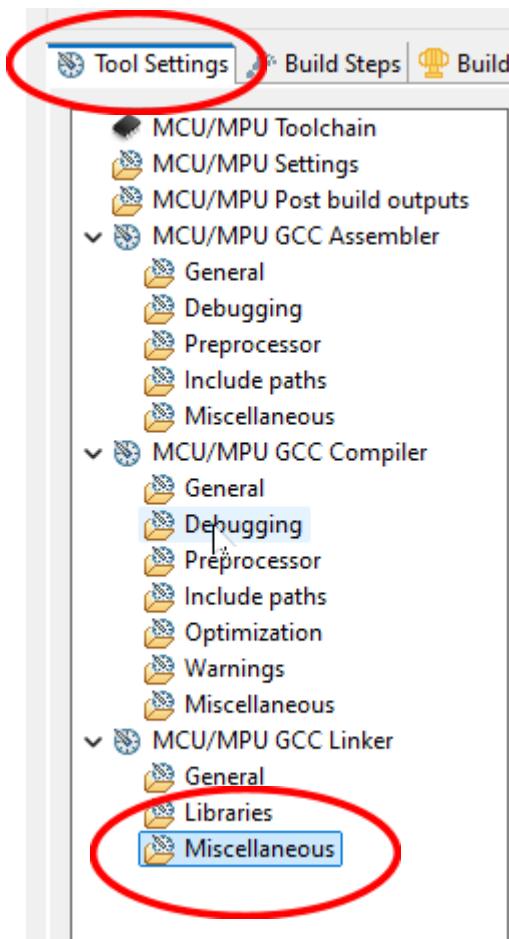

3. Mantendo ativa a aba “Tool Settings”, encontre entre as opções o conjunto “MCU GCC Linker” e clique em “Miscellaneous” (expanda o conjunto se necessário).

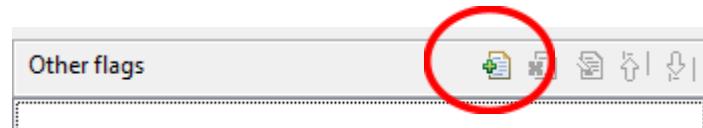

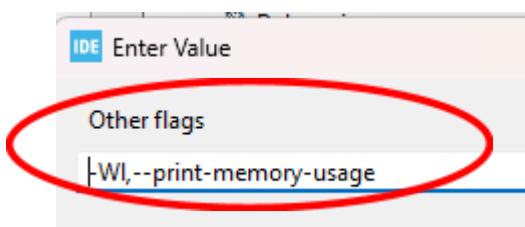

4. No campo “Other flags” clique no botão com o símbolo de “+” em verde.

5. Na janela que se abre, digite “-Wl,--print-memory-usage” e clique no botão “OK”. O “-Wl”, informa ao GCC que as opções a seguir são para o ligador e não para o próprio compilador. O “--print-memory-usage” é a opção específica para o *linker* que faz com que ele exiba estatísticas sobre o uso de memória.

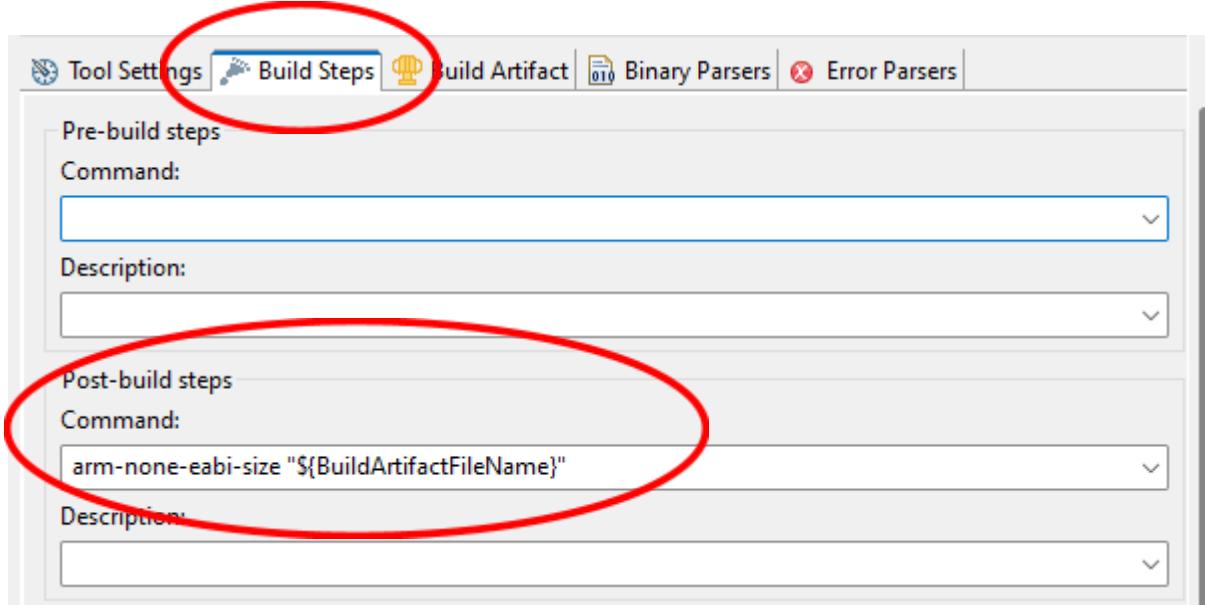

6. Adicionamos o comando “arm-none-eabi-size “\${BuildArtifactFileName}”” para exibir, na etapa de pós-construção, o tamanho das seções do arquivo binário “\${BuildArtifactFileName}” gerado pela compilação e ligação. Clique na aba “Build Steps”. Na seção “Post-build steps” adicionar o comando: arm-none-eabi-size “\${BuildArtifactFileName}”

Vale destacar que este comando é incluído no comando anterior. Optamos por esta redundância para mostrar o comando específico para exibição do tamanho dos segmentos de dados e de instruções em *bytes*.

7. Finalmente, clique no botão “Apply and Close”. Com estas configurações no projeto, ao se realizar um “Build”, ao final do processo serão mostradas as seguintes informações, incluindo a ocupação das unidades de memória físicas e o tamanho dos segmentos de instruções (text), de dados inicializados (data) e dados não inicializados (bss, do inglês *block start by symbol*). Esses tamanhos serão apresentados tanto em decimal (dec) quanto em hexadecimal (hex), medidos em *bytes*.

```

Memory region           Used Size  Region Size %age Used

ITCMRAM:             0 GB    64 KB  0.00%

FLASH:              2456 B   2 MB  0.12%

DTCMRAM1:            0 GB    64 KB  0.00%

DTCMRAM2:            0 GB    64 KB  0.00%

RAM:                2064 B   1 MB  0.20%

RAM_CD:              0 GB   128 KB  0.00%

RAM_SRD:              0 GB   32 KB  0.00%

Finished building target: Mwmoria.elf

arm-none-eabi-size Mwmoria.elf

arm-none-eabi-objdump -h -S Mwmoria.elf > "Mwmoria.list"

text    data    bss   dec   hex filename

2352     104   1960   4416   1140 Mwmoria.elf

Finished building: default.size.stdout

Finished building: Mwmoria.list

```

A lista mostra que a memória RAM é utilizada para diferentes finalidades: ITCM (do inglês *Instruction Tightly Coupled Memory*), DTCM ( do inglês *Data Tightly Coupled Memory*), RAM\_CD (do inglês *Code and Data RAM* ou *Data Cache RAM*) e RAM\_SRD (do inglês *Static Dual Rate RAM*). Sabe dizer qual das duas tecnologias de RAM, SRAM (RAM estática) e DRAM (RAM dinâmica), é predominantemente usada em microcontroladores, incluindo o microcontrolador STM32H7A3? Não se apavore se não souber responder a pergunta. Nós veremos adiante qual delas é a tecnologia de RAM predominante em microcontroladores.

8. Anote os valores apresentados, em termos de *bytes* e percentagem, do uso das unidades de memória físicas. Identifique os tipos de memória usados para o segmento de instruções e de dados inicializados e não-inicializados.

9. Clique no “Debug” para carregar o programa no microcontrolador. A perspectiva é chaveada para “Debug” e o fluxo de execução deve estar pausado (pequena seta azul à esquerda da linha) na linha “`heap_var = (char *)malloc(sizeof(char));`”

```

79 //Aloca 100 bytes para o vetor heap_var com 100 elementos do tipo

80 //char. Observe a conversao explicita de tipo de retorno "void"

81 //da funcao malloc para "char *"

82 heap_var = (char *)malloc(sizeof(char) * 100);

```

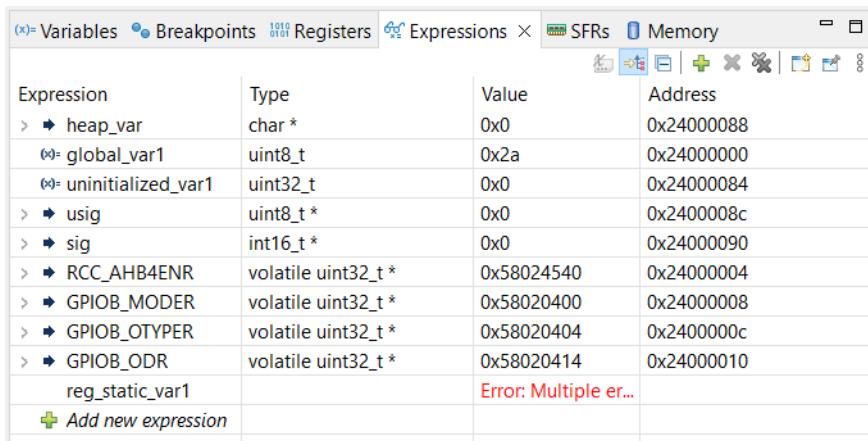

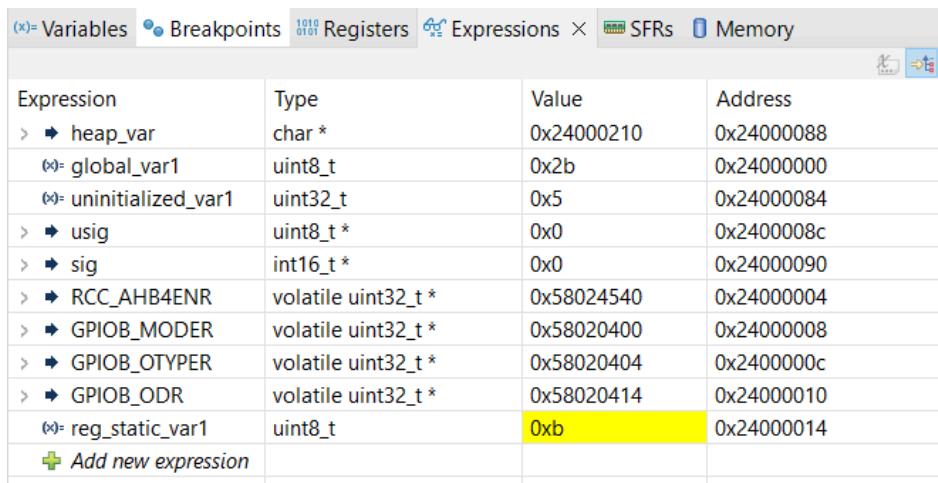

10. Na perspectiva de “Debug”, abra a aba “Expressions” e adicione as expressões conforme mostra a primeira coluna na seguinte imagem. Com base nos endereços alocados para essas variáveis e a [organização de memória](#) apresentada no Manual de Referência, identifique em qual unidade de memória física elas estão armazenadas e determine se elas estão localizadas em endereços mais baixos ou mais altos dentro dessa unidade de memória.

| Expression                               | Type                | Value                 | Address    |

|------------------------------------------|---------------------|-----------------------|------------|

| > $\Rightarrow$ heap_var                 | char *              | 0x0                   | 0x24000088 |

| $\Rightarrow$ global_var1                | uint8_t             | 0x2a                  | 0x24000000 |

| $\Rightarrow$ uninitialized_var1         | uint32_t            | 0x0                   | 0x24000084 |

| > $\Rightarrow$ usig                     | uint8_t *           | 0x0                   | 0x2400008c |

| > $\Rightarrow$ sig                      | int16_t *           | 0x0                   | 0x24000090 |

| > $\Rightarrow$ RCC_AHB4ENR              | volatile uint32_t * | 0x58024540            | 0x24000004 |

| > $\Rightarrow$ GPIOB_MODER              | volatile uint32_t * | 0x58020400            | 0x24000008 |

| > $\Rightarrow$ GPIOB_OTYPER             | volatile uint32_t * | 0x58020404            | 0x2400000c |

| > $\Rightarrow$ GPIOB_ODR                | volatile uint32_t * | 0x58020414            | 0x24000010 |

| reg_static_var1                          |                     | Error: Multiple er... |            |

| $\textcolor{blue}{+}$ Add new expression |                     |                       |            |

Note que todos os ponteiros são indicados por uma seta azul-escuro. A coluna “Value” mostra o valor do ponteiro em si e não o valor para o qual ele aponta. À esquerda da seta pode-se expandir a variável para mostrar o valor para o qual ela aponta clicando em “>”. Note que os valores dos ponteiros não inicializados é zero.

11. Use o botão “Step Over” ou a tecla F6 para avançar uma linha de código. Execute as duas próximas linhas e veja o que acontece com os valores das expressões. Olhe também a aba “Variables”, que mostra “mi”. Esta variável contém as informações sobre a alocação de “heap\_var”, especialmente o elemento “uordblk”, que indica o número total de *bytes* alocados dinamicamente pelo usuário. Quais outras variáveis são mostradas nesta aba? Qual é a função em execução? Podemos dizer que a aba “Variables” apenas mostra variáveis locais da função em execução? Veja os endereços das variáveis que estão nesta aba. Identifique em qual unidade de memória física elas estão armazenadas e determine se elas estão localizadas em endereços mais baixos ou mais altos dentro dessa unidade de memória.

Não se apavore se você não souber responder essas perguntas ainda. Elas servem para chamar atenção à identificação dos possíveis problemas de fragmentação ou uso ineficiente da memória através dos endereços das variáveis, auxiliando na otimização do código, e à organização da memória em sistemas embarcados que veremos mais adiante.

12. Execute as duas linhas seguintes, que modificam valores em variáveis. Veja o que acontece com os seus valores na aba “Expressions”.

13. Ao chegar na linha “global\_var1 = reg\_demo(10);”, ao invés de usar “Step over” (Tecla F6), use o botão “Step Into” (Tecla F5) para entrar na função. Veja o que aconteceu com a última linha da aba “Expressions”. Por quê foi preenchida esta linha apenas depois da chamada da função e durante a execução das instruções desta função onde a variável “reg\_static\_var1” é declarada? Este item mostra o impacto do modificador/qualificador “static” da linguagem C na visibilidade de uma variável declarada numa função.

| Expression                                              | Type                | Value       | Address    |

|---------------------------------------------------------|---------------------|-------------|------------|

| > $\Rightarrow$ heap_var                                | char *              | 0x240000210 | 0x24000088 |

| $\Rightarrow$ global_var1                               | uint8_t             | 0x2b        | 0x24000000 |

| $\Rightarrow$ uninitialized_var1                        | uint32_t            | 0x5         | 0x24000084 |

| > $\Rightarrow$ usig                                    | uint8_t *           | 0x0         | 0x2400008c |

| > $\Rightarrow$ sig                                     | int16_t *           | 0x0         | 0x24000090 |

| > $\Rightarrow$ RCC_AHB4ENR                             | volatile uint32_t * | 0x58024540  | 0x24000004 |

| > $\Rightarrow$ GPIOB_MODER                             | volatile uint32_t * | 0x58020400  | 0x24000008 |

| > $\Rightarrow$ GPIOB_OTYPER                            | volatile uint32_t * | 0x58020404  | 0x2400000c |

| > $\Rightarrow$ GPIOB_ODR                               | volatile uint32_t * | 0x58020414  | 0x24000010 |

| $\Rightarrow$ reg_static_var1                           | uint8_t             | 0xb         | 0x24000014 |

| <span style="color: green;">+</span> Add new expression |                     |             |            |

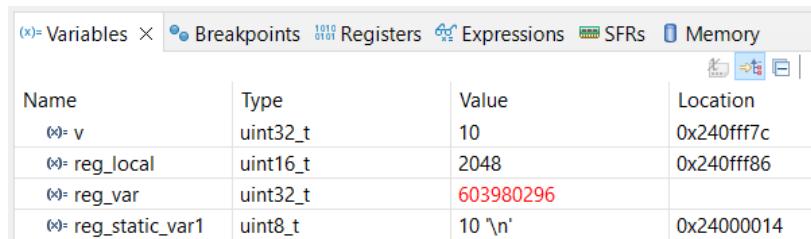

14. Vá para a aba “Variables” e veja as variáveis mostradas. Em qual função são utilizadas estas variáveis? Observe também que o campo “Location” da variável “reg\_var” está vazio. Mude para a aba “Registers” e veja os registradores de uso geral. Um deles deve ter o valor “10” (ou “0xa”) passado para a função. Volte para a aba “Variables”. Execute, passo a passo, as instruções e veja o que acontece depois da execução da linha “`reg_var = v + 1;`” Volte para a aba “Registers” e veja se há algum registrador de uso geral com o mesmo valor no campo “Value” da variável “reg\_var”. Qual foi o efeito do qualificador “register” da linguagem C na declaração da variável “reg\_var” dentro da função “reg\_demo()”? Você classificaria esta variável como local (tempo de vida limitado a uma função) ou global (tempo de vida se estende por toda a execução do programa)?

| Name                          | Type     | Value     | Location   |

|-------------------------------|----------|-----------|------------|

| $\Rightarrow$ v               | uint32_t | 10        | 0x240fff7c |

| $\Rightarrow$ reg_local       | uint16_t | 2048      | 0x240fff86 |

| $\Rightarrow$ reg_var         | uint32_t | 603980296 |            |

| $\Rightarrow$ reg_static_var1 | uint8_t  | 10 '\n'   | 0x24000014 |

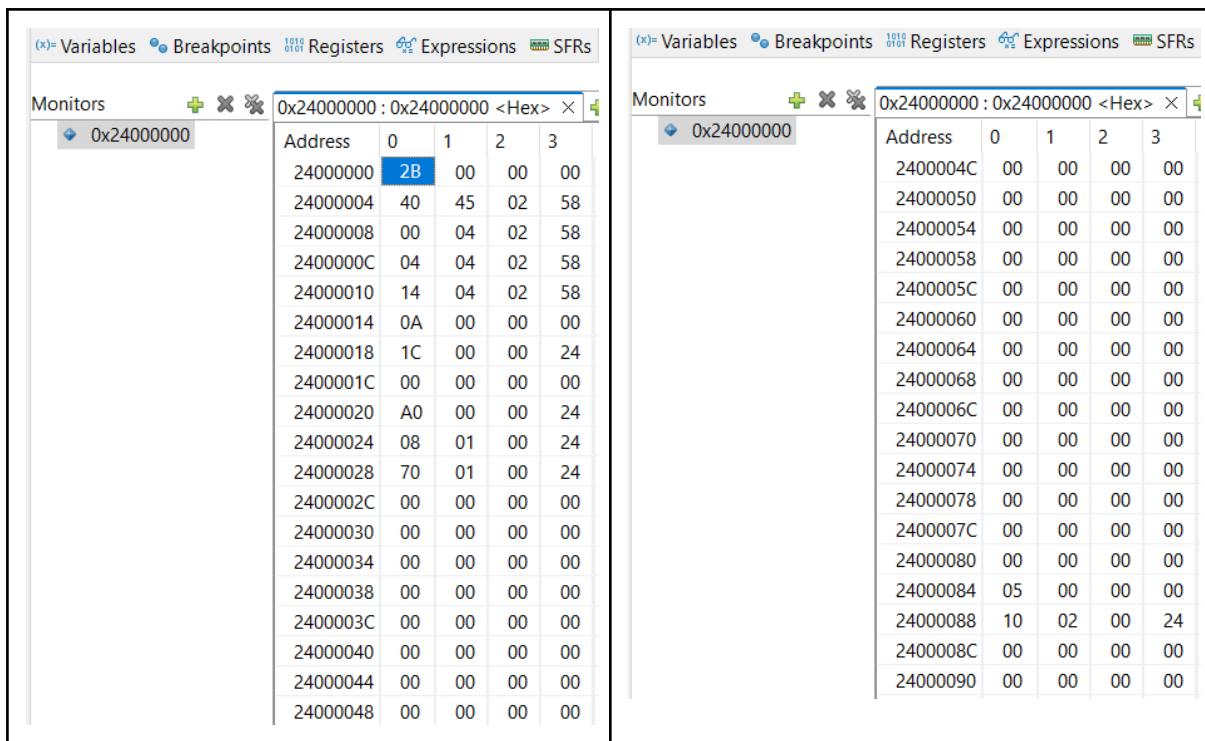

15. Vá para a aba “Memory” e analise a ordenação de *bits* das variáveis. São ordenados em *little-endian* ou em *big-endian*? Verifique ainda se as variáveis estão alocadas em espaços contíguos de memória, ou seja, se elas ficam adjacentes uma à outra. Caso contrário, identifique quais variáveis têm “buracos” (*bytes* ociosos) entre elas. Sabe por quê o compilador e o ligador nem sempre otimizam a alocação de memória para manter as variáveis “coladas” umas às outras?

Não se apavore se você não conseguiu responder as perguntas ainda. O importante é que você perceba que podem existir “lacunas” de *bytes* entre os *bytes* efetivamente alocados para variáveis. Nós veremos mais adiante os princípios adotados na conversão das instruções em linguagem C para códigos binários de máquina.

The image shows two side-by-side memory monitors. Both have tabs for Variables, Breakpoints, Registers, Expressions, and SFRs, with Registers selected. The left monitor shows memory from 0x24000000 to 0x24000048. The right monitor shows memory from 0x24000000 to 0x24000090. Both monitors have a 'Monitors' tab and a '+' button. The left monitor has a breakpoint at 0x24000000. The data is presented in a table with columns for Address and bytes 0, 1, 2, 3. The left monitor's data is as follows:

| Address  | 0  | 1  | 2  | 3  |

|----------|----|----|----|----|

| 24000000 | 2B | 00 | 00 | 00 |

| 24000004 | 40 | 45 | 02 | 58 |

| 24000008 | 00 | 04 | 02 | 58 |

| 2400000C | 04 | 04 | 02 | 58 |

| 24000010 | 14 | 04 | 02 | 58 |

| 24000014 | 0A | 00 | 00 | 00 |

| 24000018 | 1C | 00 | 00 | 24 |

| 2400001C | 00 | 00 | 00 | 00 |

| 24000020 | A0 | 00 | 00 | 24 |

| 24000024 | 08 | 01 | 00 | 24 |

| 24000028 | 70 | 01 | 00 | 24 |

| 2400002C | 00 | 00 | 00 | 00 |

| 24000030 | 00 | 00 | 00 | 00 |

| 24000034 | 00 | 00 | 00 | 00 |

| 24000038 | 00 | 00 | 00 | 00 |

| 2400003C | 00 | 00 | 00 | 00 |

| 24000040 | 00 | 00 | 00 | 00 |

| 24000044 | 00 | 00 | 00 | 00 |

| 24000048 | 00 | 00 | 00 | 00 |

The right monitor's data is as follows:

| Address  | 0  | 1  | 2  | 3  |

|----------|----|----|----|----|

| 2400004C | 00 | 00 | 00 | 00 |

| 24000050 | 00 | 00 | 00 | 00 |

| 24000054 | 00 | 00 | 00 | 00 |

| 24000058 | 00 | 00 | 00 | 00 |

| 2400005C | 00 | 00 | 00 | 00 |

| 24000060 | 00 | 00 | 00 | 00 |

| 24000064 | 00 | 00 | 00 | 00 |

| 24000068 | 00 | 00 | 00 | 00 |

| 2400006C | 00 | 00 | 00 | 00 |

| 24000070 | 00 | 00 | 00 | 00 |

| 24000074 | 00 | 00 | 00 | 00 |

| 24000078 | 00 | 00 | 00 | 00 |

| 2400007C | 00 | 00 | 00 | 00 |

| 24000080 | 00 | 00 | 00 | 00 |

| 24000084 | 05 | 00 | 00 | 00 |

| 24000088 | 10 | 02 | 00 | 24 |

| 2400008C | 00 | 00 | 00 | 00 |

| 24000090 | 00 | 00 | 00 | 00 |

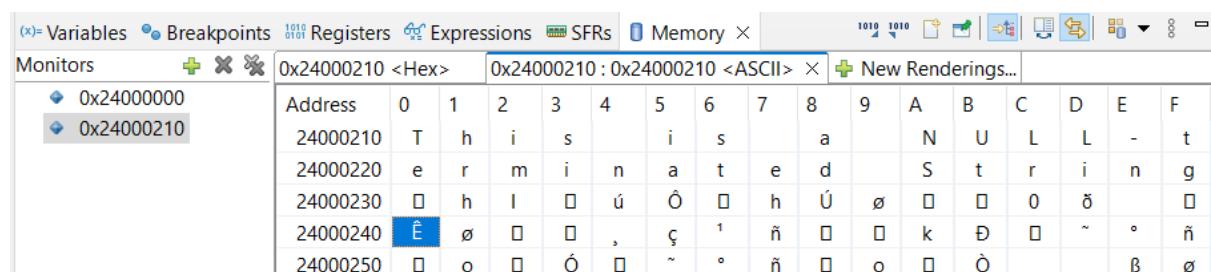

16. Ao sair da função, execute a instrução que se segue. Veja o valor do ponteiro “heap\_var” e, na aba “Memory”, crie um monitor para o endereço definido no ponteiro. Clique com o botão DIREITO em qualquer célula e selecione “Format”. Na janela que se abre, mude o valor de “Column Size” para 1 (byte). Além disso, adicione uma nova renderização clicando em “+” e selecione “ASCII” como novo formato de renderização. Compare os valores hexadecimais dos bytes com os códigos ASCII. Note que a linguagem C usa um valor para indicar que a *string* terminou. Qual é este valor?

The image shows a memory monitor with the 'Memory' tab selected. It has tabs for Variables, Breakpoints, Registers, Expressions, and SFRs, with Registers selected. The left monitor shows memory from 0x24000210 to 0x24000250. The right monitor shows memory from 0x24000210 to 0x24000210. Both monitors have a 'Monitors' tab and a '+' button. The left monitor has a breakpoint at 0x24000210. The data is presented in a table with columns for Address and bytes 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F. The left monitor's data is as follows:

| Address  | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F |

|----------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 24000210 | T | h | i | s |   | i | s |   | a |   | N | U | L | L | - | t |

| 24000220 | e | r | m | i | n | a | t | e | d |   | S | t | r | i | n | g |

| 24000230 | Ø | h | I | Ø | ú | Ó | Ø | h | Ú | ø | Ø | Ø | 0 | ð | Ø | Ø |

| 24000240 | Ê | ø | Ø | Ø | , | ç | 1 | ñ | Ø | Ø | k | Ø | ~ | º | ñ | Ø |

| 24000250 | Ø | o | Ø | Ó | Ø | ~ | º | ñ | Ø | o | Ø | Ø |   | Ø | Ø | Ø |

16. Execute as duas instruções a seguir e observe o efeito sobre a variável “mi”. Pela observação, você consegue explicar o que a função “realloc” faz? Não tem problema se você não consegue. Apenas registre o termo na sua memória e preste atenção nas explicações mais adiante.

17. Execute as instruções até a linha “for(;;)”. Em seguida, vá para a aba "Monitor" e examine o conteúdo da memória a partir do endereço “0x58024400”. Compare os valores exibidos nas células de memória com os valores dos registradores do periférico RCC na aba "SFRs". Por que há tanta semelhança entre esses dois conjuntos de valores?

Sabia que o tipo de dado “struct” em C permite mapear um bloco de memória, como o intervalo de “0x58024400” a “0x5802457F”, associando grupos de *bytes* de memória com nomes de registradores mapeados? Isso facilita a organização e a leitura dos dados na memória, rotulando os grupos de *bytes* conforme os registradores correspondentes.

| Address  | 0 - 3    | 4 - 7    | 8 - B    | C - F    |

|----------|----------|----------|----------|----------|

| 58024400 | 25400000 | 21070040 | 32010000 | 88000020 |

| 58024410 | 00000000 | 00000000 | 00000000 | 00000000 |

| 58024420 | 00000000 | 00000000 | 00020202 | 0000FF01 |

| 58024430 | 80020101 | 00000000 | 80020101 | 00000000 |

| 58024440 | 80020101 | 00000000 | 00000000 | 00000000 |

| 58024450 | 00000000 | 00000000 | 00000000 | 00000000 |

| 58024460 | 00000000 | 00000000 | 00000000 | 00000000 |

| 58024470 | 00000000 | 00000000 | 00000000 | 00000000 |

| 58024480 | 00000000 | 00000000 | 00000000 | 00000000 |

| 58024490 | 00000000 | 00000000 | 00000000 | 00000000 |

| 580244A0 | 00000000 | 00000000 | 00000000 | 00000000 |

| 580244B0 | 00000000 | 00000000 | 00000000 | 00000000 |

| 580244C0 | 00000000 | 00000000 | 00000000 | 00000000 |

| 580244D0 | 0000E800 | 00000000 | 00000000 | 00000000 |

| 580244E0 | 00000000 | 00000000 | 00000000 | 00000000 |

| 580244F0 | 00000000 | 00000100 | 00000000 | 3151E9FD |

| 58024500 | 23020006 | 710A0060 | FF072030 | 48000000 |

| 58024510 | FFC3FFE8 | 36010000 | F330D740 | AAE6010C |

| 58024520 | 00000000 | 00000000 | 00000000 | 00000000 |

| 58024530 | 0000E800 | 00000000 | 00000000 | 00000000 |

| 58024540 | 00000000 | 00000000 | 00000000 | 00000000 |

| 58024550 | 00000000 | 00000100 | 00000000 | 3151E9FD |

| 58024560 | 23020006 | 710A0060 | FF072030 | 48000000 |

| 58024570 | FFC3FFE8 | 36010000 | F330D740 | AAE6010C |

| 58024580 | 00000000 | 00000000 | 00000000 | 00000000 |

18. Onde está localizada a constante “const\_var1”? Por quê? Para responder esta pergunta, vale lembrar que no Roteiro 2 mostramos que, em C, os valores de variáveis de tipos de dados com modificador `const` não podem ser alterados durante toda a execução do programa. Qual memória é ideal para armazená-los?

19. Termine a execução do programa (CTRL+F2). Volte para o editor da perspectiva “C/C++”. Apague as barras de comentário (“//”) da linha “`const_var1++;`” e tente realizar um “Build”. O que acontece? **Dica:** Sempre leia atentamente as mensagens de erros e avisos.

20. Com base na sua análise, organize os segmentos *Code*, *Data*, *BSS*, *Stack* e *Heap* de acordo com seus endereços de memória. Verifique se o *layout* desses segmentos segue a ordenação típica, do endereço mais baixo para o mais alto: *Code*, *Data*, *BSS*, *Heap* e *Stack*.

## FUNDAMENTOS TEÓRICOS

Compreender a representação de informações em códigos binários é fundamental para quem trabalha com Engenharia Elétrica e da Computação. Esse conhecimento é a base para criar sistemas eficientes, que armazenam dados de forma otimizada e os recuperam rapidamente. Ao entender como os dados são organizados e manipulados em nível de *bits*, como um número inteiro é representado em binário, por exemplo, fica mais fácil entender a importância dos tipos de dados em C e seus impactos nos resultados observados no projeto-exemplo. Vamos explorar agora os detalhes por trás da definição de tipos de dados e das instruções de alocação de memória em C no projeto-exemplo. Ao final, espera-se que você adquira uma base sólida para entender como os dados são organizados na memória e como isso afeta o desempenho e a eficiência de seus programas.

## TECNOLOGIAS DE MEMÓRIA: PROM, EPROM, EEPROM, FLASH NAND, NOR, SRAM e DRAM

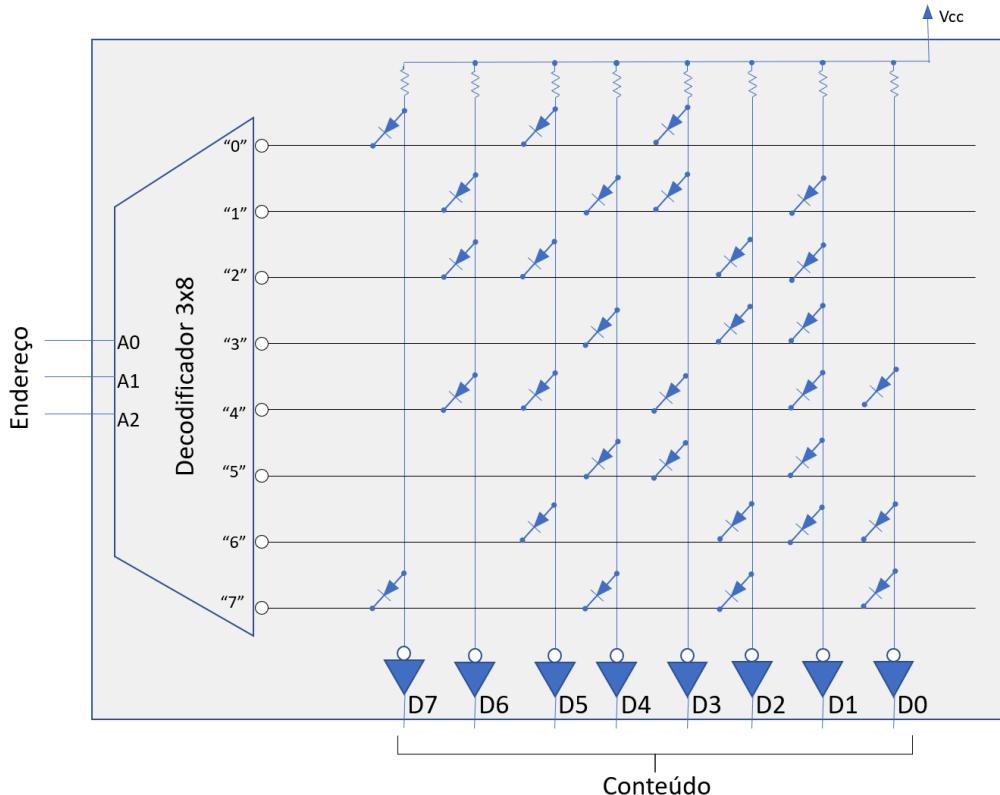

Os princípios de funcionamento de um circuito de memória podem ser ilustrados com uma matriz de diodos. Os sinais A2-A0 correspondem a entrada do código de endereço. Para cada combinação destes três *bits*, uma única saída do decodificador 3x8 é colocada no nível lógico “0” (zero), todas as demais saídas do decodificador permanecem no nível lógico “1” (um). Cada saída deste decodificador aciona uma linha da matriz. As colunas desta matriz são levadas ao nível alto (em inglês, *pull-up*) por um resistor ligado ao Vcc. Cada coluna entra em uma porta inversora gerando os sinais D7-D0, que são os *bits* de saída de conteúdo da memória. Nos cruzamentos linha-coluna da matriz podem ser colocados diodos com o anodo ligado na coluna e o catodo ligado na linha. Quando uma linha correspondente ao código em A2-A0 for colocada em zero (selecionada), os diodos a ela ligados estarão polarizados diretamente, aproximando o nível lógico da coluna do diodo a “0”, que passando pelo inversor da saída, expõe o nível lógico “1”. Nos cruzamentos desta linha onde não houver diodo, a coluna permanecerá em nível lógico “1” que, passando pelo inversor de saída, expõe o nível lógico “0”. Considere a condição do código de endereço igual a 000 selecionando a linha “0”, com a disposição dos diodos nesta linha, a saída D7-D0 ficará em 10101000. Dizendo de outra forma, o conteúdo da posição 0 é 10101000. A programação do conteúdo de cada posição desta memória será feita pela ligação de diodos em cada cruzamento da matriz onde for necessário “armazenar” o valor “1”.

A matriz de diodos é um modelo simplificado, mas funcional. No entanto, as memórias modernas foram além dos diodos para oferecer programabilidade, regravabilidade e maior eficiência. Entre as principais tecnologias de memória moderna estão PROM, EPROM, EEPROM, SRAM, DRAM, FLASH NAND e FLASH NOR, cada uma com suas particularidades e aplicações específicas.

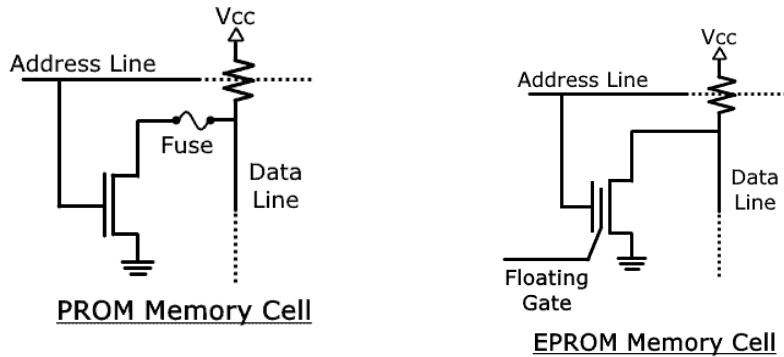

**OTP** (do inglês *One-Time Programmable*) refere-se a um tipo de memória que pode ser programada apenas uma vez. Após a gravação inicial, os dados armazenados na memória OTP não podem ser alterados. Nos microcontroladores, a memória OTP é aplicada no armazenamento de informações permanentes, identificadores únicos, códigos de configuração e dados de calibração. Além disso, é utilizada para armazenar dados de segurança, como chaves criptográficas. Existem várias tecnologias utilizadas para implementar a memória OTP em microcontroladores. Uma das tecnologias mais comuns é a **PROM** (do inglês *Programmable Read-Only Memory*), em que os diodos foram substituídos por transistores bipolares e fusíveis programáveis eletricamente. A PROM é uma **memória não-volátil**, programada uma única vez através de um processo que envolve a aplicação de uma alta tensão para fundir fusíveis internos, de modo a armazenar o valor "0" no bit.

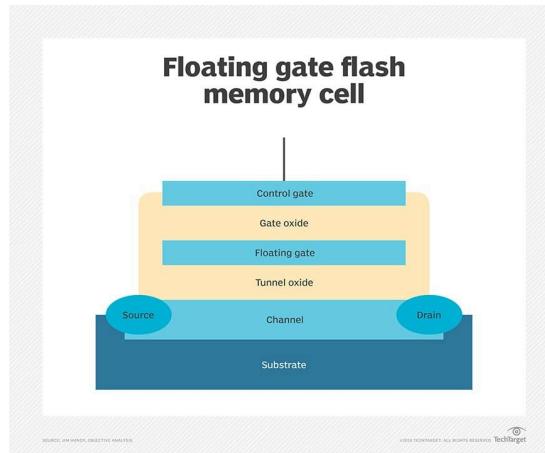

**Outra tecnologia relacionada é a EPROM** (do inglês *Erasable Programmable Read-Only Memory*), em que os transistores bipolares e fusíveis foram substituídos por transistores de porta flutuante, introduzindo a regravabilidade. Os [transistores de porta flutuante](#) representam um tipo especial de transistor, distinguindo-se pela presença de uma porta flutuante (em inglês, *floating gate*), capaz de armazenar cargas elétricas que representam os dados. Quando a porta está carregada (*bit "0"*), a corrente não passa pelo transistor. Se a porta está descarregada (*bit "1"*), a corrente flui livremente. Durante a programação, uma alta tensão é aplicada, resultando em uma descarga de avalanche de elétrons que se acumula na porta flutuante. Este fenômeno é conhecido por **injeção de elétrons quentes**. A carga acumulada na porta flutuante é isolada pelas camadas de óxido, impedindo seu vazamento e garantindo que os dados sejam armazenados de forma permanente. Para apagar os dados, é necessário expor a EPROM à luz ultravioleta, que dissipá a carga acumulada. Apesar de sua capacidade de ser reprogramada, a EPROM é considerada uma **memória não-volátil** porque mantém seu conteúdo mesmo quando o *chip* é desenergizado. Em alguns casos ela é utilizada como uma memória OTP quando a capacidade de apagamento não é necessária.

Desenvolvida para substituir o processo de apagamento por luz ultravioleta da EPROM e tornar o processo mais flexível e prático, as cargas acumuladas nas portas flutuantes de uma **EEPROM** (do inglês *Electrically Erasable Programmable Read-Only Memory*) podem ser apagadas e reprogramadas eletricamente, sem precisar remover o *chip* do circuito, incluindo um circuito de programação especial. Em dispositivos semicondutores, o **tunelamento** é um fenômeno quântico que permite que elétrons atravessem barreiras de potencial que, segundo a física clássica, seriam intransponíveis. No caso da memória EEPROM, o fenômeno específico conhecido como **tunelamento Fowler-Nordheim** permite que uma carga elétrica seja transferida para a porta flutuante do transistor, representando dados na memória, mesmo

com tensões relativamente baixas, semelhantes às tensões de leitura. Por permitir a reprogramação *byte a byte*, a velocidade de gravação de EEPROM é geralmente mais lenta a EPROM. Por outro lado, a memória FLASH, um tipo de EEPROM, foi projetada para oferecer alta velocidade a um custo mais baixo. No entanto, a memória FLASH tem um número limitado de ciclos de reprogramação, cerca de 10 mil, enquanto os modelos mais recentes de EEPROM podem suportar até 1 milhão de ciclos. Além disso, a FLASH exige a exclusão de grandes blocos de memória, em vez de *bytes* individuais.

A memória FLASH é também baseada em transistores de porta flutuante. O nome FLASH deriva da ideia de *flash* em inglês, que transmite a ideia de algo que ocorre rapidamente, refletindo a capacidade da memória de apagar e gravar dados rapidamente. A gravação da FLASH tradicionalmente envolvia a injeção de elétrons quentes. Esse processo requer tensões mais altas do que as tensões de leitura, pois os elétrons precisam adquirir energia suficiente para “saltar” para a porta flutuante. No entanto, a tecnologia FLASH evoluiu, e técnicas de tunelamento também são utilizadas em algumas variantes de FLASH para melhorar a eficiência e reduzir a necessidade de altas tensões. No estado não programado (sem cargas nas portas flutuantes), as células de memória FLASH geralmente correspondem ao valor lógico “1” (ou nível alto).

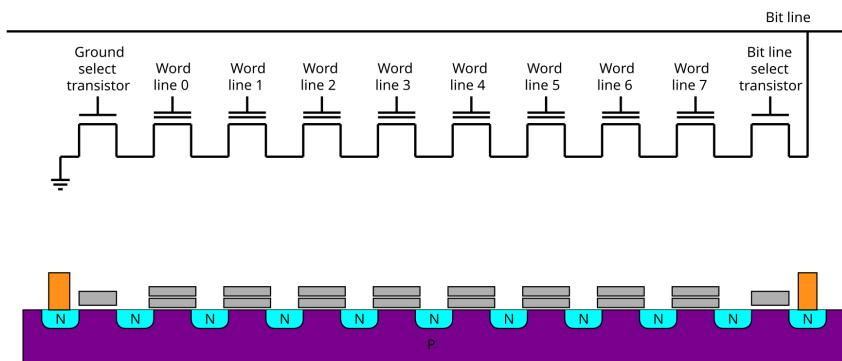

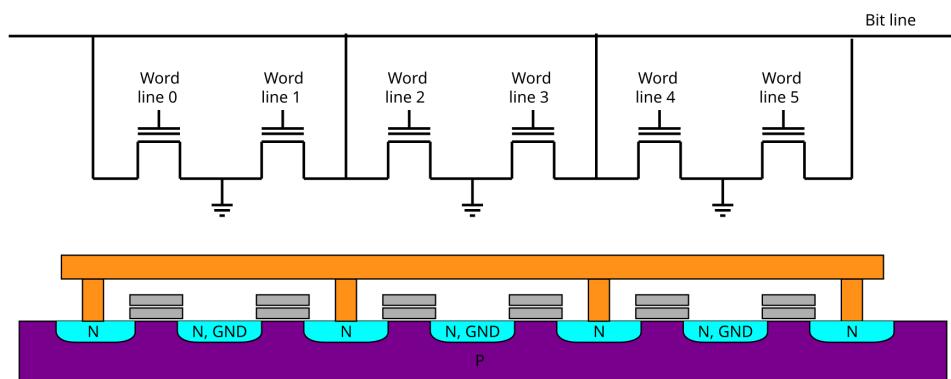

**FLASH NAND** é um tipo de **memória não-volátil** que armazena dados em células dispostas em série dentro de cada linha de bit (em inglês, *bit line*). Essa configuração faz com que a lógica da leitura dessas células se assemelhe à lógica de uma porta NAND: a leitura de uma linha de células depende do estado de todas as células da linha. Se qualquer célula impedir a passagem de corrente, a leitura da linha é afetada. Cada cadeia NAND possui transistores de seleção (*Bit Line Select* e *Ground Line Select*) no início e no fim, controlando o fluxo de corrente. Cada transistor de porta flutuante, responsável por armazenar os dados, possui um transistor de seleção associado, controlado pelo sinal da linha *wordline*, que define qual transistor será lido durante o acesso.

As células conectadas em série são, por sua vez, agrupadas em páginas, e essas páginas são organizadas em blocos. Devido à estrutura em série, o apagamento deve ser realizado em blocos inteiros, o que é eficiente para limpar grandes áreas de memória, mas impede o apagamento e a gravação de células individuais. A gravação, por outro lado, é realizada por páginas, o que permite a escrita de dados em uma página específica dentro de um bloco.

Essa arquitetura é amplamente utilizada em dispositivos de armazenamento devido à sua alta densidade e custo relativamente baixo. A memória FLASH NAND é ideal para aplicações que requerem grandes capacidades de armazenamento, como cartões de memória e unidades SSD (do inglês *Solid State Drives*). No entanto, a principal desvantagem é que a escrita e o apagamento devem ser feitos em blocos inteiros, o que pode reduzir a eficiência em operações de leitura e escrita aleatória. Por essas razões, a FLASH NAND é menos comum em microcontroladores, que frequentemente demandam acesso rápido e flexível a pequenas porções de dados. A complexidade de controle e as limitações associadas à escrita e apagamento em grandes blocos não se adequam bem às necessidades típicas de desempenho e flexibilidade para operações de código e dados em microcontroladores.

**FLASH NOR**, outra forma de memória não-volátil, armazena dados em [transistores de porta flutuante, com a sua fonte \(em inglês, source\) conectada à linha de bit e o dreno \(em inglês, drain\) ao terra](#). Um transistor de seleção, controlado pela linha de palavra (em inglês, *wordline*), determina a conexão do transistor de porta flutuante à linha de *bit*. Essa configuração em paralelo permite que a leitura da FLASH NOR se assemelhe à lógica de uma porta NOR: o estado da célula é detectado por meio de uma comparação, como na verificação das entradas de uma porta NOR. Diferente da FLASH NAND, que organiza as células em série e acessa blocos/páginas inteiros, a FLASH NOR possibilita a leitura e gravação de dados em células individuais ou unidades menores. Com isso, o processador acessa diretamente qualquer endereço de memória, sem necessidade de ler blocos completos.

Essas características faz da FLASH NOR uma escolha ideal para armazenar *firmware* e código de inicialização que precisa ser acessado rapidamente. Sua arquitetura proporciona acesso aleatório direto, facilitando operações de leitura. No entanto, é geralmente mais lenta para operações de escrita e tem uma capacidade de armazenamento menor em comparação com a FLASH NAND. Por essas razões, a FLASH NOR é frequentemente preferida em aplicações que exigem execução direta de código da memória, como em sistemas embarcados e *firmware* de dispositivos.

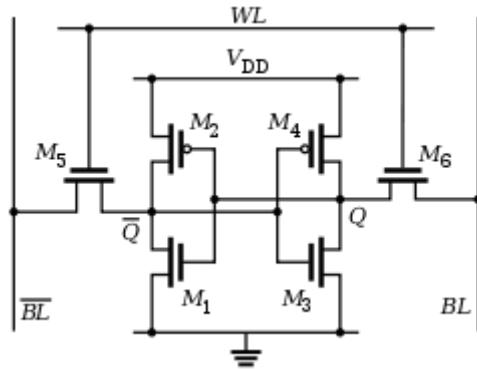

**SRAM** (do inglês *Static Random-Access Memory*) é uma tecnologia de **memória volátil** que se destaca pela sua alta velocidade e simplicidade de operação. Ao contrário da DRAM (do inglês *Dynamic RAM*), que precisa ser periodicamente atualizada, a SRAM retém seus dados enquanto a energia estiver sendo fornecida. Isso se deve ao seu componente interno, que pode utilizar [6 flip-flops para armazenar um bit](#) de informação. Esse componente é tipicamente conhecido como uma célula de memória.

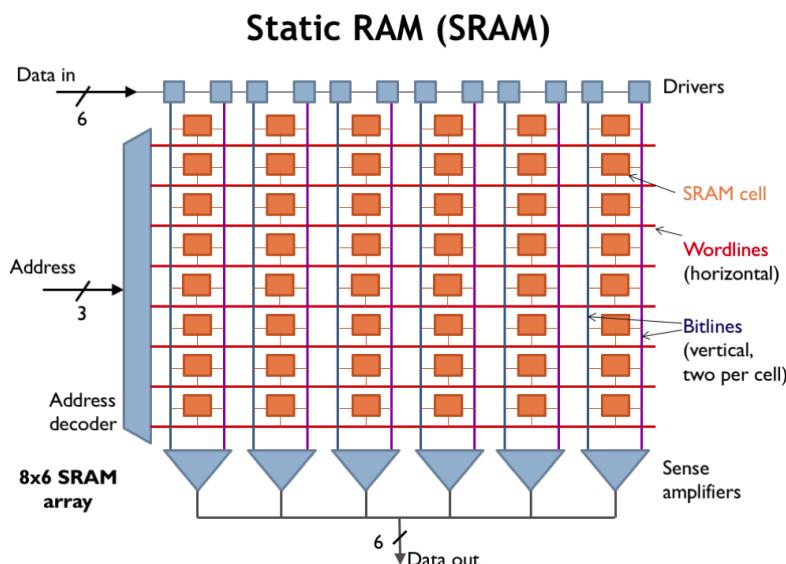

Em uma memória SRAM, cada célula de memória é conectada a duas linhas de *bit*, BL e \BL, por meio de dois transistores, M<sub>5</sub> e M<sub>6</sub>. Esses transistores atuam como chaves, controladas pela linha de palavra (WL). Quando a linha de palavra é ativada, os transistores permitem que a célula seja lida ou escrita. As células, representadas por retângulos laranja no [esquema a seguir](#), são interligadas para formar uma memória SRAM de 8 palavras de 6 bits.

A estrutura apresentada permite acesso quase instantâneo aos dados, o que a torna ideal para aplicações que requerem altas taxas de transferência e baixa latência. No entanto, a SRAM é mais cara e consome mais energia por *bit* armazenado comparada à DRAM e à memória FLASH, o que limita seu uso a tamanhos relativamente menores.

**DRAM** (do inglês *Dynamic Random Access Memory*) é uma forma de **memória volátil** amplamente utilizada para armazenar dados temporários em computadores e outros dispositivos eletrônicos. A tecnologia da DRAM se baseia em células de memória compostas por capacitores e transistores. Cada célula de DRAM armazena um *bit* de dado através de um capacitor que retém uma carga elétrica, representando um valor binário de 0 ou 1, enquanto um transistor controla o acesso à carga para ler ou escrever dados na célula. Quando a DRAM precisa ler um dado, o transistor é ativado para permitir a detecção da carga no capacitor, que é então amplificada e interpretada. Para escrever dados, a carga do capacitor é ajustada através do transistor para refletir o novo valor. Um aspecto importante da DRAM é

que a carga no capacitor pode vazar ao longo do tempo, o que exige que o conteúdo da célula seja periodicamente refrescado para manter a integridade dos dados.

Apesar de suas vantagens em termos de densidade de armazenamento e custo, a DRAM não é comumente utilizada em microcontroladores. Isso se deve principalmente à necessidade constante de **refresco** (em inglês *refreshing*) **dos dados**, o que adiciona complexidade ao sistema e aumenta o consumo de energia, tornando-a menos eficiente para aplicações onde a simplicidade e a eficiência energética são prioritárias. Além disso, a DRAM é mais complexa de implementar em comparação com outras tecnologias, como SRAM, que é preferida em microcontroladores devido à sua simplicidade e desempenho mais rápido.

## MAPA DE MEMÓRIA

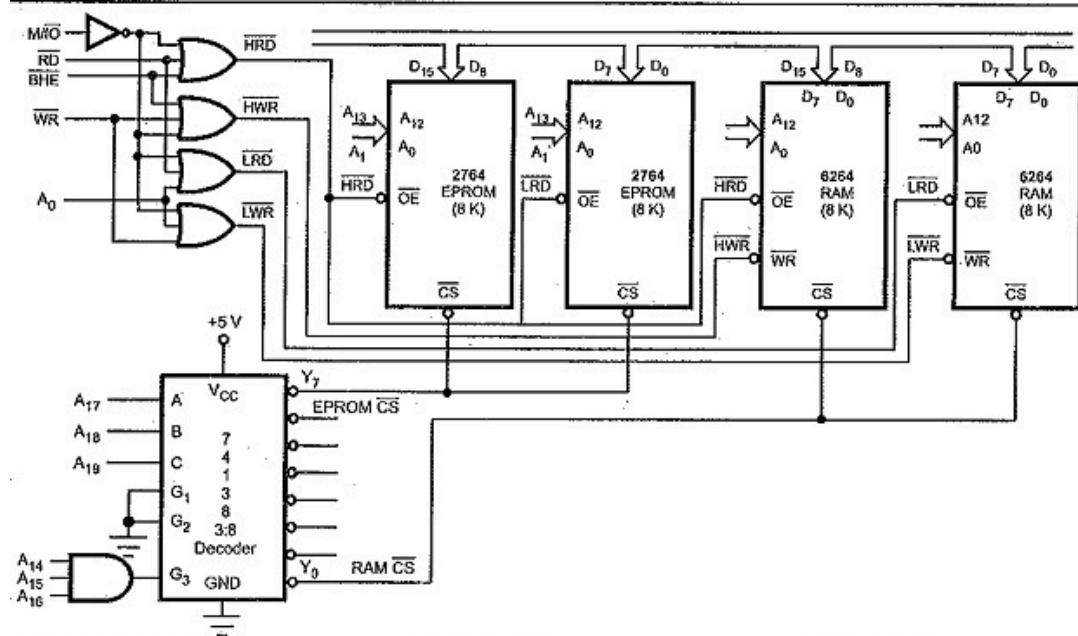

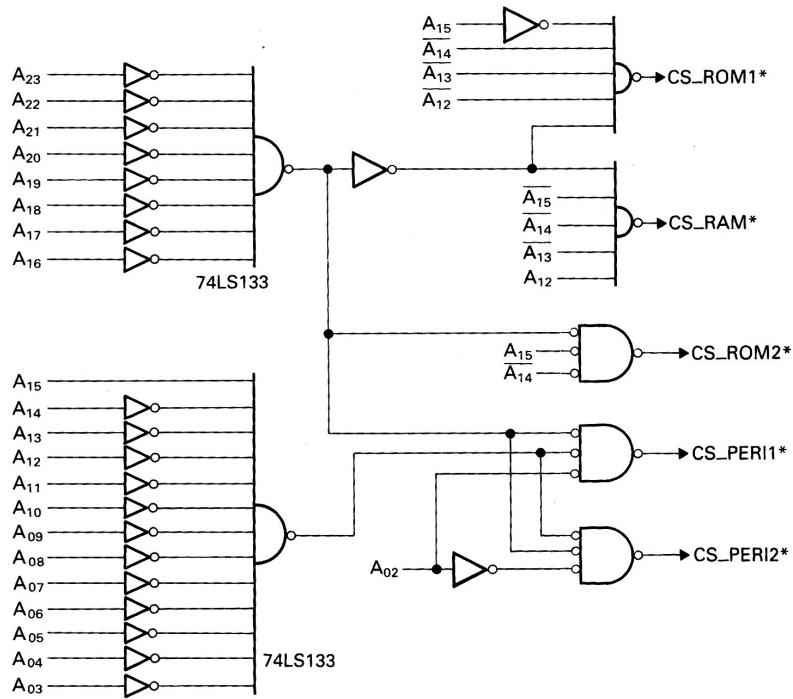

A organização geral da memória de um sistema computacional pode ser vista no **mapa de memória**. Este mapa divide a memória em blocos, usando como critérios o tipo de memória e a utilização da mesma. A maioria dos microcontroladores ARM, por usarem registradores de 32 bits, podem acessar um espaço de memória total de 4GB. Note que, apesar de a CPU poder acessar todo este espaço, muitas vezes apenas parte dele está ocupado com elementos físicos de memória. A conversão de um endereço no espaço de endereçamento do processador para um endereço específico em uma unidade de memória física é realizada pelo **decodificador de endereços**. Normalmente, o endereço é dividido em dois campos: [CS | *Offset*]. O campo de *bits* mais significativos é usado para gerar o sinal de Seleção de *Chip* (CS), que identifica qual unidade de memória física deve ser ativada. Já o campo de *bits* menos significativos é utilizado para endereçar os *bytes* dentro da unidade de memória selecionada. Nesse contexto, o valor *Offset* = 0 corresponde ao **endereço-base**, ou seja, o endereço inicial do bloco contíguo em que a unidade de memória física está mapeada.

Fig. 10.14 Block decoding

Segue-se um exemplo de circuito de decodificação dos endereços do processador de 24 bits em sinais de Seleção de *Chip* de ROM1, ROM2, RAM, PERI1 e PERI2, sendo PER1 e PER2 dois periféricos mapeados no espaço de endereçamento do processador.

O [Manual de Referência](#) apresenta a organização de memória do microcontrolador STM32HA3ZIT-Q, começando com a informação de que memórias de programa, dados, registradores e portas de entrada/saída compartilham o mesmo espaço linear de 4 GB. A [Tabela 6 da seção 2.3.2](#) apresenta o mapa de memória, incluindo blocos reservados para memórias externas e internas. Observe que os endereços de valores mais baixos estão no final da tabela, enquanto os limites de cada bloco de memória são endereços alinhados em múltiplos de 4 bytes. Internamente, os seguintes blocos estão ocupados por elementos físicos de memória:

- **Periféricos (0x4000 0000 a 0x5FFF FFFF):** Espaço reservado para o acesso aos registradores mapeados em memória dos periféricos. É importante notar que esses elementos de memória não são do tipo SRAM ou FLASH; em vez disso, o acesso a esses endereços é direcionado aos registradores dos diferentes periféricos do microcontrolador.

|             |                           |                                                                              |        |   |     |

|-------------|---------------------------|------------------------------------------------------------------------------|--------|---|-----|

| Peripherals | 0x4000 0000 - 0x5FFF FFFF | Peripherals (refer to <a href="#">Table 7: Register boundary addresses</a> ) | Device | - | Yes |

|-------------|---------------------------|------------------------------------------------------------------------------|--------|---|-----|

- **RAM (0x2000 0000 a 0x3FFF FFFF):** Espaço da SRAM, dividido em vários blocos, sendo alguns reservados (sem elementos físicos) e outros com blocos de SRAM ligados a vários barramentos internos, Backup, SDR (do inglês *Single Data Rate*),

AHB (do inglês *Advanced High-Performance*) e AXI (do inglês *Advanced eXtensible Interface*). Esses barramentos internos servem para interconectar a SRAM com diferentes partes do sistema, cada um com suas características e finalidades específicas.

- **Code (0x0000 0000 a 0x1FFF FFFF):** Área que inclui as memórias não-voláteis, como memória de sistema (registradores que guardam configurações gerais do microcontrolador), FLASH de código, e uma área OTP (do inglês *One-Time Programming*, que não pode ser regravada, usada para guardar dados permanentes).

**Table 6. Memory map and default device memory area attributes (continued)**

| Region | Boundary address          | Arm® Cortex®-M7     | Type   | Attributes                                 | Execute never |

|--------|---------------------------|---------------------|--------|--------------------------------------------|---------------|

| RAM    | 0x3880 1000 - 0x3FFF FFFF | Reserved            | Normal | Write-back, write allocate cache attribute | No            |

|        | 0x3880 0000 - 0x3880 0FFF | Backup SRAM         |        |                                            |               |

|        | 0x3801 0000 - 0x387F FFFF | Reserved            |        |                                            |               |

|        | 0x3800 0000 - 0x3800 7FFF | SDR SRAM            |        |                                            |               |

|        | 0x3002 0000 - 0x37FF 7FFF | Reserved            |        |                                            |               |

|        | 0x3001 0000 - 0x3001 FFFF | AHB SRAM2           |        |                                            |               |

|        | 0x3000 0000 - 0x3000 FFFF | AHB SRAM1           |        |                                            |               |

|        | 0x2600 0000 - 0x2FFF FFFF | Reserved            |        |                                            |               |

|        | 0x2500 0000 - 0x25FF FFFF | GFXMMU              |        |                                            |               |

|        | 0x2410 0000 - 0x24FF FFFF | Reserved            |        |                                            |               |

|        | 0x240A 0000 - 0x240F FFFF | AXI SRAM3           |        |                                            |               |

|        | 0x2404 0000 - 0x2409 FFFF | AXI SRAM2           |        |                                            |               |

|        | 0x2400 0000 - 0x2403 FFFF | AXI SRAM1           |        |                                            |               |

|        | 0x2002 0000 - 0x23FF FFFF | Reserved            |        |                                            |               |

|        | 0x2000 0000 - 0x2001 FFFF | DTCM                |        |                                            |               |

| Code   | 0x1FF2 0000 - 0x1FFF FFFF | Reserved            | Normal | Write-through cache attribute              | No            |

|        | 0x1FF0 0000 - 0x1FF1 FFFF | System Memory       |        |                                            |               |

|        | 0x08FF F400 - 0x1FEF FFFF | Reserved            |        |                                            |               |

|        | 0x08FF F000 - 0x08FF F3FF | OTP area            | Normal | -                                          | No            |

|        | 0x0820 0000 - 0x08FF EFFF | Reserved            | Normal | Write-through cache attribute              | No            |

|        | 0x0810 0000 - 0x081F FFFF | Flash memory bank 2 |        |                                            |               |

|        | 0x0800 0000 - 0x080F FFFF | Flash memory bank 1 |        |                                            |               |

|        | 0x0001 0000 - 0x07FF FFFF | Reserved            |        |                                            |               |

|        | 0x0000 0000 - 0x0000 FFFF | ITCM RAM            |        |                                            |               |

Note que a SRAM e os periféricos podem ser lidos e escritos diretamente pela CPU usando instruções padrão, porém a região de *Code*, onde as instruções são armazenadas, permite apenas leitura direta pela CPU, mas as escritas devem ser feitas através de um periférico interno específico para gravação da FLASH.

## ALINHAMENTO DE DADOS

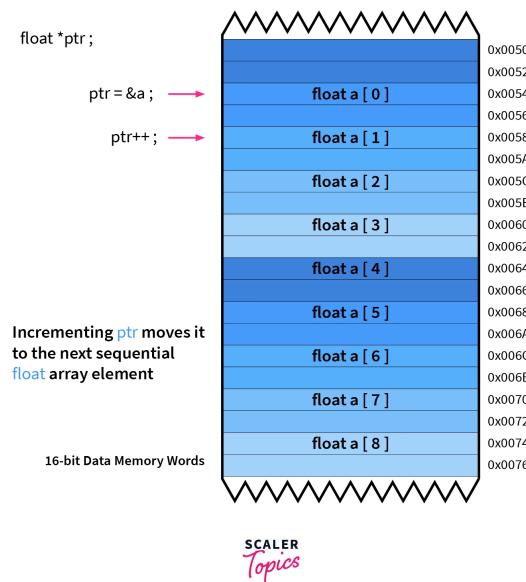

A menor unidade de acesso a todas as memórias é o *byte*. O **alinhamento de dados** se refere à organização dos dados na memória de forma que os endereços estejam alinhados conforme

a arquitetura do processador. Processadores exigem que os dados sejam armazenados em endereços que são múltiplos do tamanho da sua palavra. O tamanho da palavra de um processador se refere ao número de *bits* que ele pode processar em uma única operação. Além disso, o barramento de memória, que conecta o processador à memória principal, é projetado para transferir dados em blocos do tamanho da palavra do processador. Quando os dados estão alinhados com o limite de palavra (em inglês *word*), o processador pode acessar uma palavra inteira em uma única operação, utilizando toda a largura do barramento. Isso permite operações de leitura ou escrita em uma única transação, ao contrário dos dados desalinhados, que exigem múltiplas transações. Assim, o alinhamento adequado maximiza a eficiência do acesso à memória e melhora o desempenho geral do sistema.

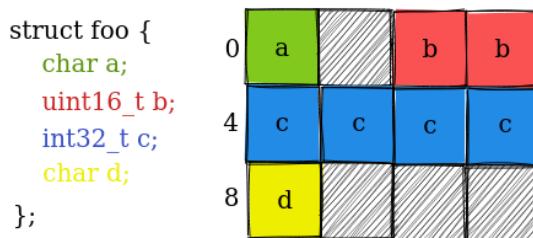

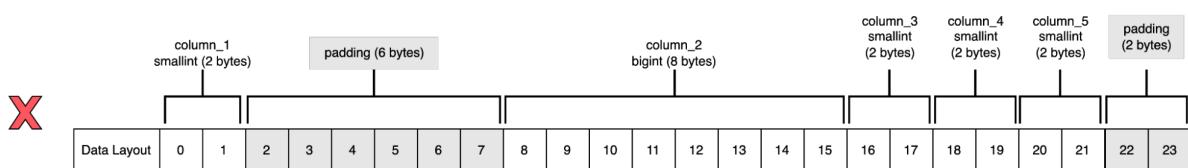

Quando os dados não estão alinhados corretamente, o sistema precisa adicionar *padding* (espaço não utilizado) para garantir o alinhamento adequado. Os *padding*s são *bytes* extras inseridos entre os dados para ajustar o alinhamento. Isso pode causar um aumento significativo no tamanho das estruturas de dados. Por exemplo, se uma estrutura contém um “char” seguido de um “int”, o compilador adiciona automaticamente *bytes* de padding entre eles para garantir que o *int* esteja alinhado em um múltiplo de 4 *bytes*. No entanto, o uso de *padding* pode resultar em desperdício de memória, especialmente em estruturas grandes ou em sistemas com recursos limitados.

Para otimizar o alinhamento e evitar *padding* desnecessário, é fundamental organizar os dados e estruturas de forma a minimizar o desperdício de memória. Isso pode ser feito posicionando os membros maiores das estruturas antes dos menores, alinhando dados de acordo com o tamanho da palavra do processador e utilizando diretivas de alinhamento fornecidas pelo compilador. Além disso, a análise e o ajuste do *layout* das estruturas para garantir que os dados estejam alinhados com os múltiplos adequados pode reduzir a quantidade de *padding* necessário. Técnicas como a reorganização de membros em estruturas e o uso das ferramentas de compilação ajudam a melhorar o uso da memória e a eficiência do sistema.

Por exemplo, considere uma tabela contendo quatro colunas do tipo “smallint” e uma coluna do tipo “bigint”, se uma coluna “smallint” (2 *bytes*) for seguida por uma coluna “bigint” (8 *bytes*), o sistema adiciona 6 *bytes* de preenchimento após a coluna “smallint” para garantir que a coluna “bigint” esteja alinhada a um limite de 8 *bytes*. No entanto, ao reorganizar as colunas “smallint” para que todas elas precedam a coluna “bigint”, é possível otimizar o *layout* da tabela e reduzir a necessidade de preenchimento. Um cenário que posiciona todas as quatro colunas “smallint” antes da coluna “bigint” é um cenário que minimiza o espaço de preenchimento, permitindo o uso de memória de forma mais eficiente.

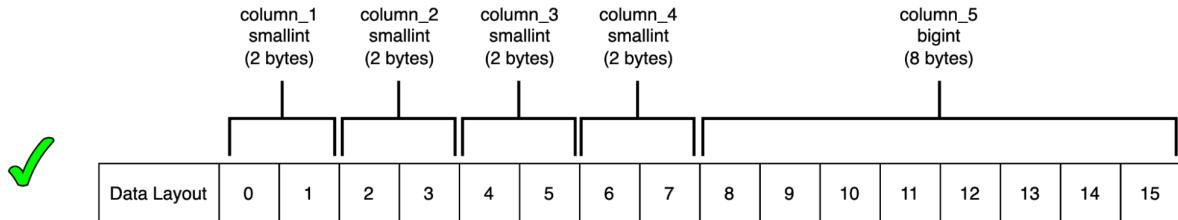

## ORDENAÇÃO DOS BYTES

Como uma palavra de memória do processador pode conter mais de um *byte*, existem duas estratégias principais para a organização desses *bytes* nos endereços de memória, conhecidas como **ordenação de bytes**. Os termos **little-endian** e **big-endian** descrevem esses métodos distintos. Em um sistema *little-endian*, o *byte* menos significativo é armazenado no menor endereço de memória, enquanto o *byte* mais significativo ocupa o endereço mais alto. Por [exemplo](#), para o valor  $1991994 = 0x001E53A$ , a organização seria  $0x3A$  no menor endereço e  $0x00$  no maior. Em contraste, em um sistema *big-endian*, a organização é inversa: o *byte* mais significativo é armazenado no menor endereço e o menos significativo no maior. Assim, para o mesmo valor,  $0x00$  estaria no menor endereço e  $0x3A$  no maior. A escolha de um esquema de ordenação é crucial para a interoperabilidade entre diferentes sistemas, pois garante que os dados sejam interpretados corretamente pelo processador ao serem trocados entre sistemas com diferentes ordenações. Compreender e aplicar a ordenação de *bytes* de forma adequada maximiza a eficiência e a compatibilidade no processamento de dados.

## SEGMENTAÇÃO DE MEMÓRIA PRINCIPAL

Para organizar e gerenciar eficientemente os recursos de memória em sistemas embarcados, garantindo a integridade e segurança dos dados e instruções em execução, é comum adotar uma abordagem de segmentação na memória responsável por armazenar dados e instruções que o processador precisa acessar rapidamente durante a execução de um programa. A memória utilizada para esse propósito é conhecida como **memória principal**. Em linguagens como C, essa segmentação reflete-se na forma como diferentes tipos de dados e código são

alocados e acessados. Cada segmento de memória possui regras e comportamentos específicos para o acesso e manipulação, alinhados com o tipo de dado que ele contém.

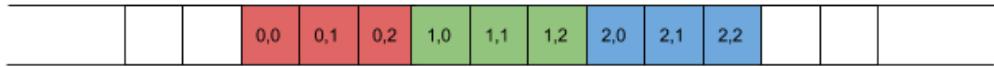

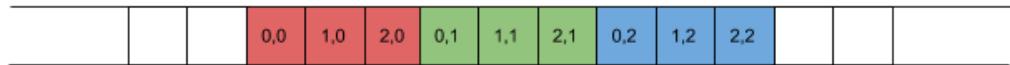

A **memória de instruções**, também conhecida como **memória de programa** ou **segmento de texto** (em inglês, *text*), armazena as instruções do programa em execução. Essas instruções são acessadas sequencialmente pelo processador e interpretadas/executadas para gerar os sinais de controle necessários. Contendo o código do programa, a memória de instruções delineia a sequência de operações a serem executadas pelo processador. Essa memória é geralmente somente de leitura, pois o código do programa não deve ser modificado durante a execução. Em sistemas embarcados, esse segmento é armazenado na memória FLASH, que retém dados mesmo quando o sistema está desligado.

A **memória de dados** tem a finalidade de armazenar os dados utilizados pelo programa em execução, abrangendo variáveis, vetores, estruturas de dados e outros elementos essenciais para a execução dos programas. Esses dados são passíveis de leitura, escrita e manipulação pelo processador conforme necessário durante a execução do programa, o que torna necessário o mapeamento dessa memória em unidades físicas de memória regraváveis, como a SRAM.

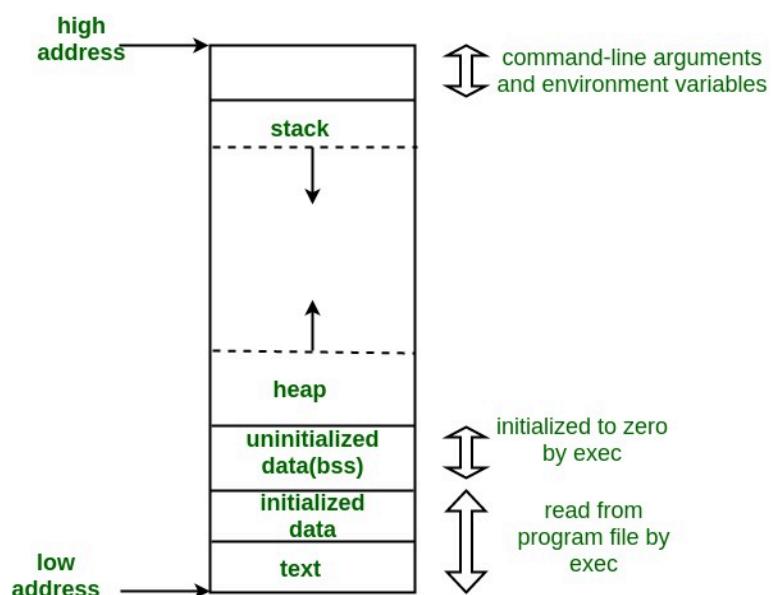

Para uma organização eficiente e gerenciamento otimizado dos diversos tipos de dados processados por um programa, é tipicamente dividida a memória de dados em segmentos específicos. Destacam-se os segmentos: **bss** (do inglês *Block Started by Symbol*), **rodata** (do inglês *Read-Only Data*), **data**, **pilhas** e **heap**. Essa distinção facilita a alocação, manipulação e controle de diferentes categorias de dados. Muitas linguagens de programação, especialmente a C, associam diferentes tipos de dados a diferentes regiões da memória de dados.

O **segmento BSS** é projetado para variáveis com uma vida útil que se estende por toda a execução do programa, mas que não são inicializadas explicitamente no código. Essas variáveis são reservadas na memória SRAM sem valores iniciais específicos; em vez disso, um código de inicialização pode ser incluído no próprio código principal para garantir que este segmento seja zerado antes do início da execução do programa. A estratégia aqui é alocar um bloco de dados para todas as variáveis não inicializadas em vez de alocar células de memória individuais para cada uma delas. Essa abordagem permite economizar tempo de alocação e inicialização, uma vez que não é necessário armazenar os valores iniciais dessas variáveis. Tipicamente, este segmento fica armazenado na memória SRAM.

O **segmento Rodata** é usado para armazenar dados somente leitura, ou seja, dados apenas para leitura e não podem ser modificados durante a execução do programa, como as variáveis do tipo de dado const da linguagem C. Ao separar os dados somente leitura em um segmento específico, é possível otimizar o acesso a esses dados e economizar espaço, pois eles não precisam ser duplicados em diferentes partes do programa, podendo ficar no espaço do arquivo executável. Em sistemas embarcados, esses dados são armazenados na memória FLASH, pois eles não mudam durante a execução do programa.

O **segmento Data** é usado para armazenar variáveis que permanecem ativas durante toda a execução do programa. Essas variáveis são inicializadas uma vez e podem ser modificadas conforme o programa avança. O espaço de cada variável é alocado e inicializado individualmente. Tipicamente, esse segmento reside entre o segmento text e o segmento BSS.

As **pilhas** (do inglês *stacks*) são amplamente usadas em sistemas computacionais para armazenar dados temporários, necessários dentro de um escopo específico de fluxo de controle, como vimos no Roteiro 3. Tendo suporte em *hardware* na maioria dos processadores, é apenas necessário organizar um bloco contíguo de células na memória RAM e armazenar o endereço do topo do bloco no registrador de ponteiro da pilha SP. Tipicamente, os endereços armazenados no ponteiro de pilha são alinhados em 8 bits (1 byte).

A **memória heap** corresponde a um bloco de memória RAM reservado para alocação dinâmica de posições de memória, isto é, alocação de posições durante a execução de um programa. Isso possibilita o compartilhamento de memória entre diferentes partes de um programa, podendo ser a única opção para microcontroladores com grandes restrições de memória. A alocação/desalocação dinâmica de memória não é ainda implementada por circuitos específicos. Ela é implementada por *software* de um sistema operacional, como por exemplo FreeRTOS, ou de uma biblioteca de gerenciamento de memória dinâmica, como em C *Bare Metal*. Por determinismo e por automatização, recomenda-se minimizar o uso de memória *heap* em projetos de sistemas embarcados. O gerenciamento dinâmico da memória *heap* pode introduzir complexidade imprevisível e afetar o determinismo do sistema, o que é crítico para aplicações de tempo real e sistemas com requisitos rigorosos de desempenho.

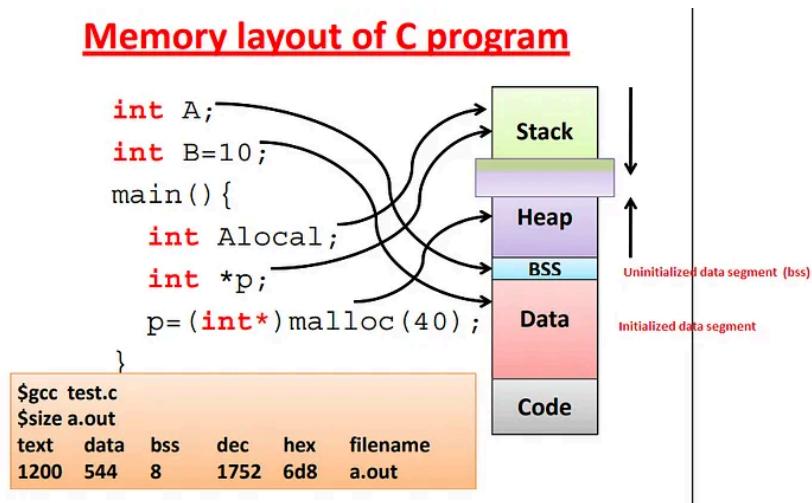

A [figura](#) a seguir ilustra a organização dos diferentes segmentos de insruções e dados na memória, incluindo áreas distintas para código (text), dados estáticos, *heap* e pilha, demonstrando como cada segmento é alocado e gerenciado durante a execução de um programa.

## MEMÓRIA CACHE

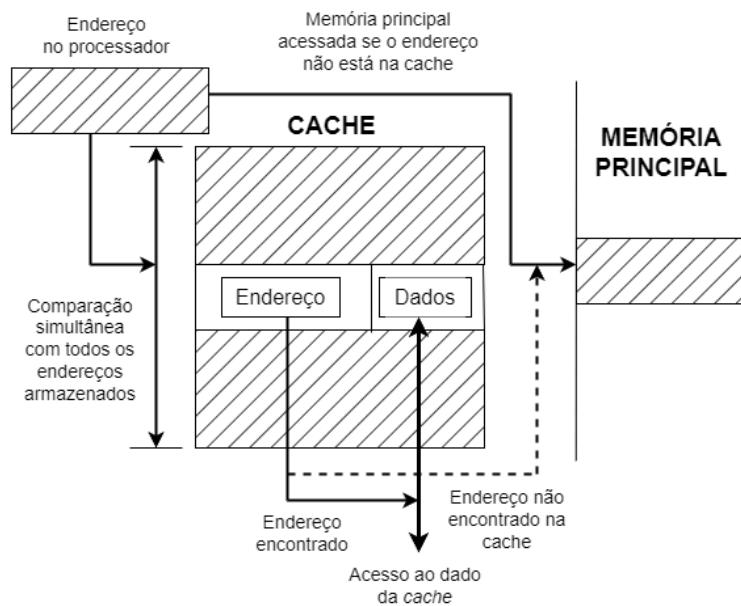

Embora muitos microcontroladores não incluam o mecanismo *cache* devido a considerações de custo e simplicidade, a introdução de *cache* em modelos mais avançados pode trazer significativos ganhos de desempenho e eficiência. Um circuito de gerenciamento *cache* é particularmente vantajoso em aplicações mais complexas ou exigentes, onde a redução da latência e a melhoria da eficiência energética são importantes. Em comparação com sistemas de alto desempenho, como CPUs que possuem múltiplos níveis de *cache*, os microcontroladores geralmente utilizam uma arquitetura de *cache* mais simplificada. Tipicamente, esses dispositivos incorporam um único nível de *cache* diretamente no núcleo do processador, o que é adequado para atender às suas necessidades mais específicas e restritas.

A **memória cache** funciona como um “*buffer*” intermediário entre o processador e a memória principal. Baseando-se em estimativas e suposições sobre o programa em execução, realiza-se uma cópia das instruções e dados necessários no *cache*. Assim, quando o processador acessa uma instrução ou dado, espera-se que ocorra um ***cache hit***, ou seja, que a instrução, ou o dado, já esteja presente no *cache*. Se a maioria dos dados requisitados estiver no *cache*, a latência média de acesso à memória de instruções ou dados será reduzida em comparação com um sistema sem *cache*. No entanto, se o dado solicitado não estiver no *cache*, ocorre um ***cache miss***. Nesse caso, o processador deve buscar as instruções ou os dados na memória principal, o que demanda mais tempo num ciclo de acesso.

A transferência entre a memória principal e o *cache* geralmente ocorre em blocos de instruções e dados, conhecidos como **linhas de cache**. A expectativa de que ocorra um *cache hit* nos acessos subsequentes é baseada nos princípios de localidade temporal e localidade espacial. O *cache* é projetado para aproveitar essas propriedades, mantendo dados e instruções frequentemente acessados ou adjacentes no *cache* para reduzir a latência de acesso.

e melhorar a eficiência do sistema. A **localidade temporal** garante que dados ou instruções recentemente acessados tenham uma alta probabilidade de serem reutilizados, enquanto a **localidade espacial** garante que dados próximos ao recentemente acessado também sejam carregados e disponíveis para acessos futuros. Com isso, o processador passa menos tempo esperando para acessar a memória principal e pode manter uma taxa de execução mais alta.

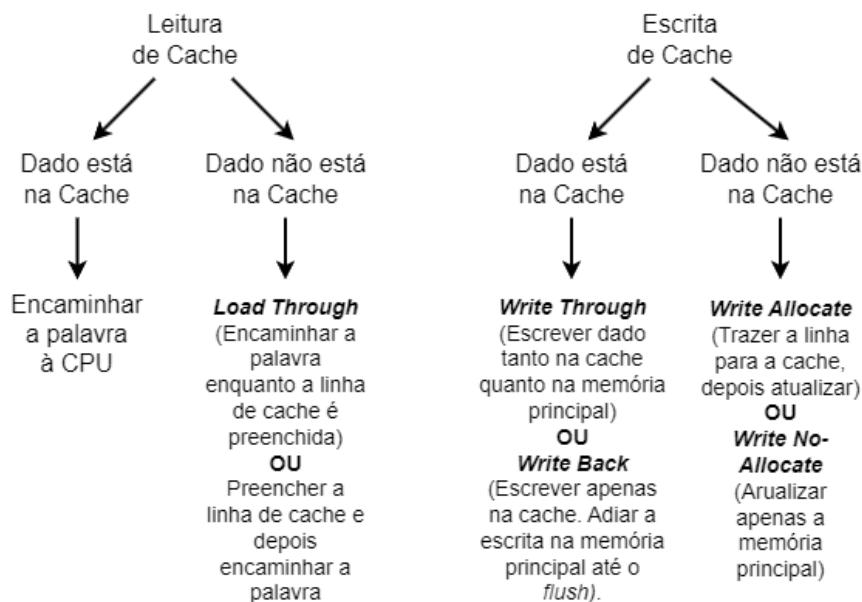

Observe que, quando o dado é modificado no *cache*, a memória principal deve ser consistentemente atualizada. Usa-se o *bit* “*Dirty*” para mostrar o estado de modificação de cada linha de *cache*. A [figura](#) sintetiza as diferentes políticas que podem ser adotadas na leitura e escrita de dados na memória principal com a presença do *cache*.

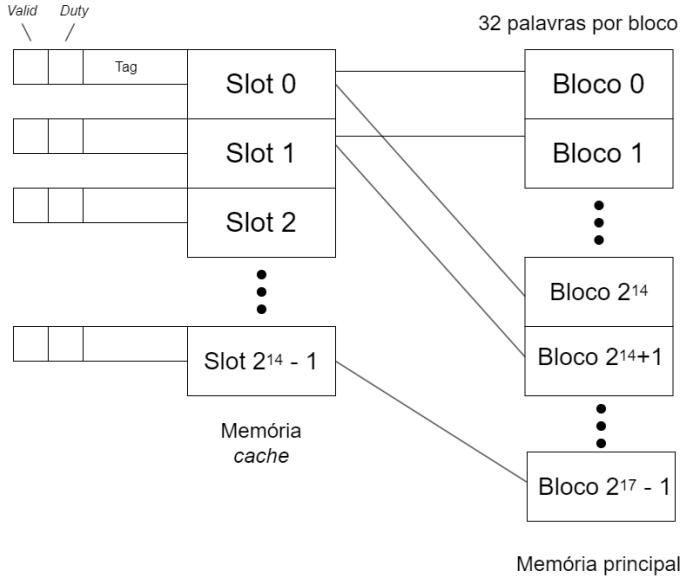

Essencialmente, há três tipos principais de mapeamento de blocos de memória principal para o *cache*, conhecidos como métodos de mapeamento de *cache*: *cache* direto (em inglês, *direct-mapped cache*), *cache* associativo por conjunto (em inglês, *set-associative cache*) e *cache* totalmente associativo (em inglês, *fully associative cache*).

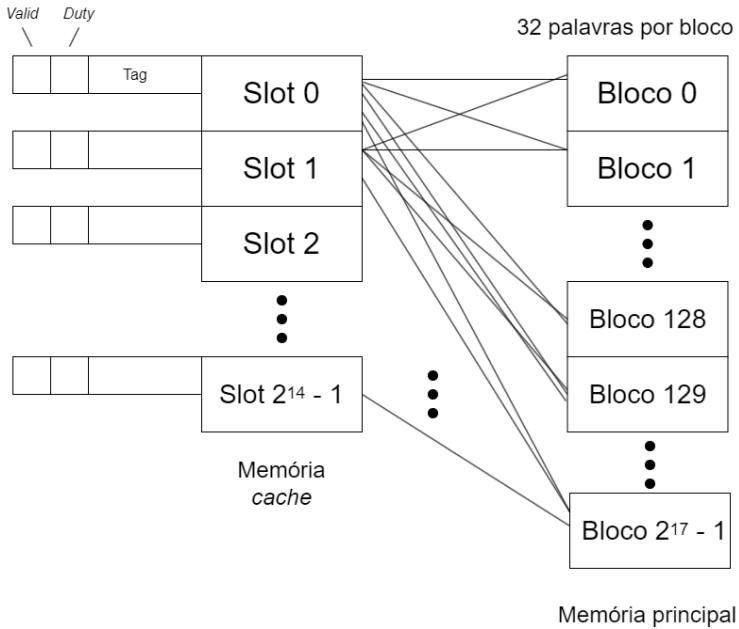

O ***cache* direto** é o método mais simples e direto de mapeamento. Neste esquema, cada bloco de memória principal é mapeado para um único local específico no *cache*. Ou seja, cada linha *i* de *cache*, Slot *i*, pode armazenar dados de apenas uma linha, Bloco *j*, de memória principal. A decisão de onde armazenar um bloco de memória principal é feita através de um cálculo direto baseado no endereço da memória, como  $i = j \% m$  onde  $m$  é a quantidade total de linhas no *cache*. Isso facilita a implementação e reduz a complexidade. No entanto, a abordagem pode levar a conflitos se vários blocos de memória principal mapearem para o mesmo local no *cache*, resultando em *cache misses* frequentes.

No mapeamento de um endereço de memória em um *cache* direto, divide-se o endereço em três campos: *[Tag|Slot|Offset]*:

**Tag**: identifica o bloco de memória principal específico.

**Slot**: Determina a linha de *cache* onde o bloco deve ser armazenado.

**Offset**: Indica a posição do *byte* dentro do bloco de dados.

O **cache associativo por conjunto** oferece um equilíbrio entre complexidade e flexibilidade. Neste método, o *cache*, composto de  $m$  linhas, é dividido em vários conjuntos, cada um contendo  $k$  linhas. Cada bloco de memória principal, Bloco  $j$ , pode ser mapeado em qualquer uma das  $k$  linhas dentro de um conjunto específico. O conjunto é determinado por  $(j\%(m/k))$ , onde  $m/k$  representa o número total de conjuntos no *cache*. O número de linhas por conjunto,  $k$ , é conhecido como **associatividade** do *cache*. Por exemplo, um *cache* associativo de 2 vias (em inglês, 2-way associative) permite que cada bloco de memória principal, Bloco  $j$ , seja armazenado em qualquer uma de duas linhas dentro do conjunto identificado, como ilustra a figura. Esta abordagem reduz os conflitos que podem ocorrer no *cache* direto, pois um bloco de memória principal tem mais opções de armazenamento, o que melhora a taxa de *cache hits*.

O endereço de memória principal é dividido em três campos:  $[Tag | Conjunto | Offset]$ . Nesse esquema:

- **Tag**: Identifica de forma única o bloco de dados específico na memória principal.

- **Conjunto**: Localiza o conjunto de *cache* onde o bloco pode estar armazenado.

- **Offset**: Especifica a posição do *byte* dentro do bloco de dados carregado na cache.

A localização de um bloco de memória principal dentro do conjunto de *cache* é feita através da comparação da *Tag* de cada linha de *cache* do conjunto de *cache* com os *bits* mais significativos do endereço de memória.

O **cache totalmente associativo** é o método mais flexível e complexo, permitindo que qualquer bloco de memória principal seja armazenado em qualquer linha do *cache*. Não há restrições quanto ao local onde um bloco pode ser colocado, o que minimiza os conflitos e maximiza a taxa de *cache hits*. No entanto, essa flexibilidade vem com um custo maior em termos de *hardware* e complexidade, pois o sistema precisa verificar todas as linhas do *cache* para encontrar um bloco específico. Isso torna a implementação e o gerenciamento do *cache* mais complexos e dispendiosos.

Devido às suas restrições de custo e complexidade, *caches* totalmente associativos são mais comuns em sistemas de alto desempenho e processadores de servidores, onde o desempenho e a flexibilidade são críticos e o custo de implementação mais complexo pode ser justificado. Em microcontroladores, quando presentes, são mais comuns *caches* direto ou associativo por conjunto, que oferecem um bom equilíbrio entre desempenho e custo, adequados para as necessidades específicas e restrições desses dispositivos.

## MEMÓRIA FORTEMENTE ACOPLADA (TCM)

A memória TCM (do inglês *Tightly Coupled Memory*) é uma forma de memória projetada para operar extremamente próxima ao processador, oferecendo baixa latência e alta largura de banda. Essa tecnologia é comumente implementada usando SRAM e se comunica com a CPU de forma direta e paralela, sem intermediários como controladores de memória que poderiam adicionar latência.

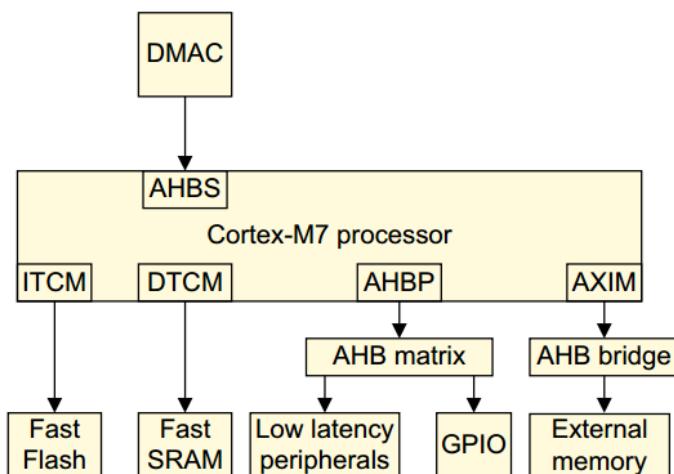

A principal motivação para a inclusão da TCM em microcontroladores é a necessidade de acesso rápido e eficiente a dados e instruções críticos. Em aplicações que demandam alto desempenho e baixa latência, como sistemas embarcados em tempo real, a TCM é utilizada para armazenar partes do código e dados frequentemente acessados. A proximidade da TCM ao núcleo do processador reduz significativamente o tempo de acesso à memória, melhorando o desempenho geral do sistema. Isso é alcançado ao evitar a latência associada ao acesso a memórias mais lentas e distantes, como a memória principal ou a memória externa. O diagrama de blocos a seguir ilustra a conexão direta entre o processador e as memórias SRAM e FLASH, que apresentam latências, via um controlador de TCM na arquitetura Cortex-M7.

Cabe ressaltar aqui que a memória *cache* atua como um intermediário entre o processador e a memória principal (RAM), armazenando dados e instruções frequentemente utilizados para acelerar o acesso. Enquanto a TCM é uma memória dedicada, separada da memória principal (RAM), conectada diretamente ao processador e projetada para fornecer acesso de baixíssima latência a dados críticos para o desempenho do sistema.

Figure 1-1 Example Cortex-M7 system

## SISTEMA DE MEMÓRIA NO STM32H7A3

O seguinte texto extraído do [Datasheet](#) sumariza as unidades de memória internas e externas suportadas pelo microcontrolador STM32H7A3.

### Memories

- Up to 2 Mbytes of flash memory with read while write support, plus 1 Kbyte of OTP memory

- ~1.4 Mbytes of RAM: 192 Kbytes of TCM RAM (inc. 64 Kbytes of ITCM RAM + 128 Kbytes of DTCM RAM for time critical routines), 1.18 Mbytes of user SRAM, and 4 Kbytes of SRAM in Backup domain

- 2x Octo-SPI memory interfaces, I/O multiplexing and support for serial PSRAM/NOR, Hyper RAM/flash frame formats, running up to 140 MHz in SRD mode and up to 110 MHz in DTR mode

- Flexible external memory controller with up to 32-bit data bus:

- SRAM, PSRAM, NOR flash memory clocked up to 125 MHz in Synchronous mode

- SDRAM/LPSDR SDRAM

- 8/16-bit NAND flash memories

- CRC calculation unit

O microcontrolador STM32H7A3, que utiliza o processador Cortex-M7 da ARM, apresenta um sistema de memória altamente otimizado para maximizar o desempenho em aplicações complexas. A arquitetura do Cortex-M7, lançada pela ARM em 2014, é a primeira da série Cortex-M a incluir mecanismo *cache* de um nível, marcando uma evolução significativa em relação aos modelos anteriores. Esta arquitetura adota uma variante da arquitetura Harvard, conhecida como Harvard modificada, que incorpora *cache* separado para instruções e dados. Esse desenho de projeto melhora o desempenho ao reduzir conflitos e otimizar o acesso às informações armazenadas, com cada tipo de *cache* especializado para o tipo de dado que armazena.

O [Manual de Cortex-M7](#) mostra que o *cache* de dados é configurado como um *cache* associativo por conjunto de quatro vias, enquanto o *cache* de instruções é um *cache* associativo por conjunto bidirecional. Ambos os *caches* utilizam linhas de 32 bytes, o que permite que cada bloco de memória principal seja carregado em uma linha de *cache*. Quando todas as linhas de *cache* em um conjunto estão ocupadas e um novo bloco precisa ser carregado, o controlador de *cache* deve substituir uma linha existente para abrir espaço para o novo bloco de dados ou instruções. Os dados e instruções armazenados no *cache* são recuperados da memória externa através da interface AXI Master (AXIM), e os controladores de *cache* utilizam SRAMs integradas ao processador para armazenar temporariamente essas informações durante a operação.

O STM32H7A3 inclui a memória TCM. De acordo com o [Manual do Cortex-M7](#), a arquitetura ARMv7E-M suporta acesso direto a essa memória através da interface AHBS (do inglês *Advanced High-performance Bus Slave*). Isso permite acesso quase instantâneo por barramentos distintos a dados e instruções críticos, armazenados em memórias separadas. Para garantir a integridade dos dados no sistema de memória, ajudando a detectar e prevenir erros de dados e aumentando a confiabilidade do sistema, o microcontrolador é provido de uma unidade CRC (do inglês *Cyclic Redundancy Check*) que é responsável por calcular e verificar o código CRC dos dados armazenados na memória.

No ambiente integrado de desenvolvimento STM32CubeIDE, o *layout* da memória e a alocação de espaço para diferentes segmentos, como instruções e dados, são definidos por meio de um *script* de *link*, como vimos no Roteiro 2. Esse *script*, com a extensão “.ld”, determina como a memória é organizada e onde cada tipo de dado e código será armazenado.

No entanto, a pré-carga da memória TCM, bem como a configuração e ajuste dos *caches* de instruções e dados, são realizadas no código-fonte do *firmware* do desenvolvedor. Isso envolve a configuração dos registradores específicos do processador para ajustar os parâmetros do sistema de memória conforme necessário.

O microcontrolador também oferece pinos para acesso a memórias externas, com modos de operação que podem ser ajustados para otimizar o desempenho conforme as necessidades específicas da aplicação. Entre esses modos, destacam-se o SRD (do inglês *Single Read Data*) e o DTR (do inglês *Dual Transfer Rate*). No modo SRD, é possível transferir um dado por ciclo de *clock*, adequado para operações básicas, enquanto o modo DTR permite a transferência de dois dados por ciclo de relógio, oferecendo uma largura de banda significativamente maior e melhorando a eficiência do sistema.

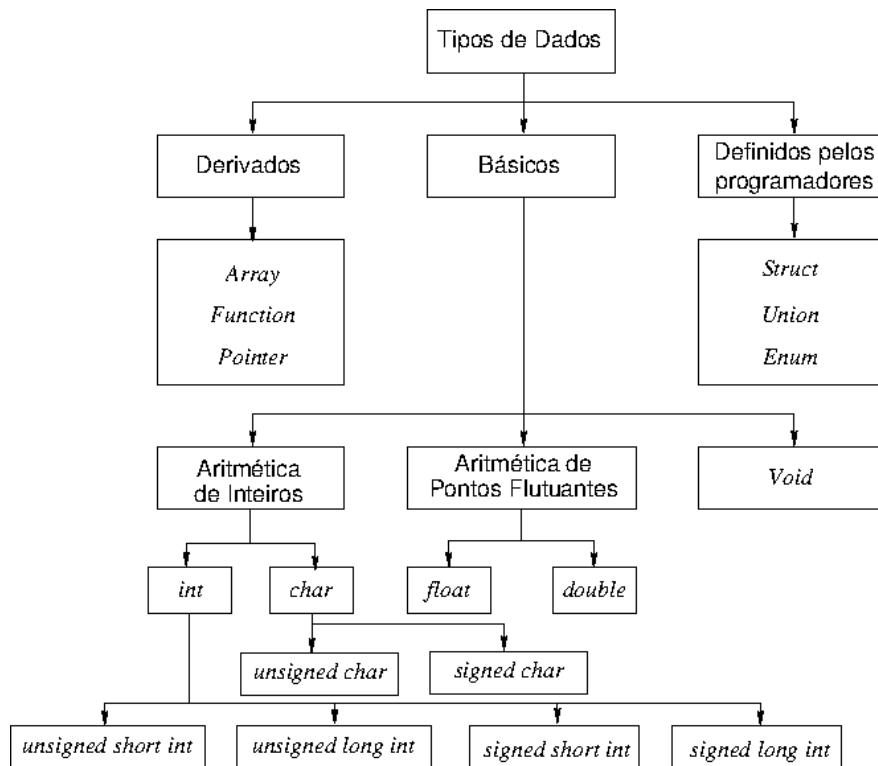

## TIPOS DE DADOS EM C

No contexto da programação, a memória do computador é um grande bloco contíguo de *bytes*, e esses *bytes* representam os dados que o *software* manipula. No entanto, a memória bruta, composta apenas por *bytes*, não é diretamente comprehensível ou útil em termos práticos. Os tipos de dados fornecidos pelas linguagens de programação transformam esses blocos de *bytes* em formas mais legíveis e úteis. Cada tipo de dado é uma maneira específica de interpretar e organizar esses *bytes*, facilitando o acesso e a manipulação das informações.

Do ponto de vista computacional, os **tipos básicos** de dados processados pelo processador são classificados em quatro categorias principais: números inteiros sem sinal, números inteiros com sinal, números de ponto flutuante e caracteres alfanuméricicos. Os caracteres alfanuméricicos incluem letras do alfabeto (tanto maiúsculas quanto minúsculas), os 10 dígitos arábicos e uma variedade de caracteres especiais, como hífen, travessão, ponto e vírgula. Existem várias abordagens para realizar essa conversão, e vamos explorar as mais comuns e amplamente utilizadas nos sistemas computacionais modernos.

**Números Naturais ou Números Inteiros sem Sinal:** O sistema de numeração decimal, amplamente conhecido, utiliza dez dígitos (0 a 9) e adota a notação posicional, onde o dígito mais à direita tem o menor valor e cada posição vale 10 vezes mais do que a posição imediatamente à direita. No entanto, este sistema não se adapta à natureza binária dos computadores. Em contraste, o sistema binário, que usa apenas dois dígitos (0 e 1), é mais adequado para a representação em computadores. Nesse sistema, cada dígito (ou *bit*) tem um valor que é o dobro do dígito à sua direita, seguindo a notação posicional.

O sistema binário é empregado para codificar números naturais ou inteiros sem sinal. Com  $n$  *bits*, é possível representar até  $2^n$  valores distintos, variando de 0 até  $2^n - 1$ . Dado que a menor unidade de armazenamento na maioria dos computadores é um *byte* (8 *bits*), a representação de números inteiros sem sinal geralmente é expressa em termos de *bytes*, podendo ser 1 *byte*, 2 *bytes*, 4 *bytes* ou 8 *bytes*, conforme a necessidade.

Para facilitar a manipulação e a leitura de grandes sequências binárias, os *bits* são frequentemente agrupados em blocos que correspondem a potências de 2, como 4 *bits* (nibble), 8 *bits* (byte), e 16 *bits*. Entre esses sistemas, a notação hexadecimal é particularmente útil em sistemas embarcados. O sistema hexadecimal, com base 16, utiliza os dígitos de 0 a 9 e as letras de A a F, que correspondem aos valores decimais de 10 a 15. Cada dígito hexadecimal representa um nibble (4 *bits*), facilitando a conversão entre binário e hexadecimal e tornando a interpretação dos dados mais eficiente.

**Números Inteiros com Sinal:** Números inteiros com sinal incluem tanto os números positivos quanto os negativos. Para representar esses números em binário destacam-se quatro diferentes formas.

A primeira delas é denominada representação de **sinal e magnitude**, em que um *bit*, usualmente o *bit* mais significativo, é reservado para representar o sinal do valor. Por convenção, 0 representa o sinal “+”, correspondendo a um número positivo, e 1 representa “-”, o que corresponde a um número negativo. Esse *bit* é chamado de **bit de sinal**. Cabe ressaltar que o restante da sequência de *bits*, tanto para um número positivo quanto para um negativo, é usada para o código binário do módulo do valor.

A segunda representação é conhecida como **complemento de um**, em que todos os números negativos são gerados a partir da sua contrapartida positiva, complementando *bit* a *bit* todos os seus *bits*. Ou seja, troca-se os 0's por 1's, e vice-versa. Esta representação tem a desvantagem de que há dois códigos binários associados ao número 0. Por exemplo, os dois códigos binários 0000 e 1111 representam o valor zero para um conjunto de números representado por 4 *bits*.

A terceira alternativa é a representação por **complemento de 2**, que resolve o problema da representação em complemento de 1 e que também facilita a realização de operações aritméticas sobre os números inteiros. A notação de complemento de 2 de um número negativo é obtida ao somar 1 à sua representação em complemento de 1. Com  $n$  *bits* nesta notação, pode-se representar os valores de  $-2^{n-1}$  até  $2^{n-1} - 1$ . O número 0 possui representação única e o *bit* mais significativo é o *bit* de sinal. É adotada a mesma convenção

das outras duas representações para interpretar o *bit* de sinal: se 0, então o número é positivo, senão o número é negativo. O interessante é que se quiser converter um número negativo em complemento de 2 para a sua contrapartida positiva, também em complemento de 2, basta complementar bit a bit o número e somar 1 ao resultado. Um problema observado nesta representação é a ordenação dos números pelos seus códigos binários, pois uma simples comparação de *bits* pode levar a conclusões erradas se não forem considerados o *bit* de sinal e os valores absolutos dos números.

A quarta representação é a representação de **excesso-N**. Esta representação usa o valor N como um valor de deslocamento (polarização), de forma que o código binário de N corresponde ao número 0 e o código binário com todos os *bits* zerados corresponde a  $-N$ . Desta forma, pode-se ordenar os números negativos e positivos comparando diretamente os seus códigos binários. Por exemplo, para o valor em decimal 35, a sua representação em excesso-128 é  $35+128 = 163$ .

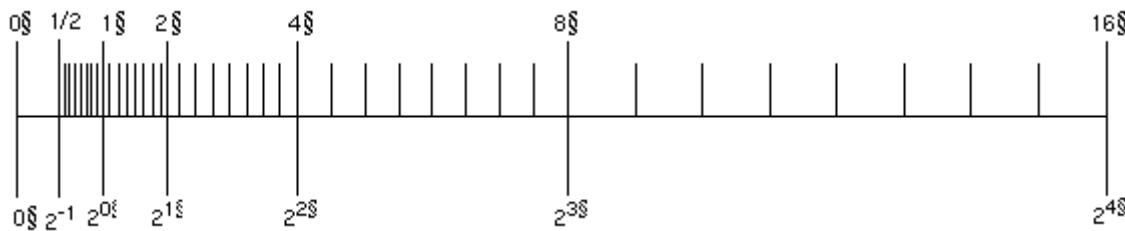

**Pontos flutuantes:** É importante notar que a quantidade distinta de valores que um conjunto de n *bits* pode representar de forma única é limitada a  $2^n$ . Para representar uma gama “infinita” de valores dentro de um intervalo real, utilizamos a **representação em ponto flutuante**. De acordo com o padrão IEEE 754, um número em ponto flutuante é descrito em notação científica por três componentes principais: **sinal, expoente e mantissa**.

|                  |                     |                            |

|------------------|---------------------|----------------------------|

| <b>S - sinal</b> | <b>E - expoente</b> | <b>F(ração) - mantissa</b> |

|------------------|---------------------|----------------------------|