# **DISCIPLINA EA701**

## **Introdução aos Sistemas Embarcados**

### **ROTEIRO 5: Temporizadores Digitais**

**TIM6/TIM7, SYSTICK, LPTIM1/LPTIM2, RTC e WATCHDOG**

**Profs. Antonio A. F. Quevedo e Wu Shin-Ting**

**FEEC / UNICAMP**

**Revisado e modificado em fevereiro de 2025 por Ting com auxílio do Chatgpt**

**Revisado em agosto de 2024**

This work is licensed under Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International. To view a copy of this license, visit

<https://creativecommons.org/licenses/by-nc-sa/4.0/>

|                                                   |           |

|---------------------------------------------------|-----------|

| <b>INTRODUÇÃO</b>                                 | <b>2</b>  |

| <b>PROJETOS-EXEMPLO</b>                           | <b>3</b>  |

| Projeto com o TIM6 usando CMSIS                   | 4         |

| Projeto com o SysTick usando CMSIS                | 9         |

| Projeto com o LPTIM usando CMSIS                  | 13        |

| Projeto com o Watchdog usando STM32CubeMX e CMSIS | 18        |

| Projeto com RTC usando STM32CubeMX e CMSIS        | 27        |

| <b>FUNDAMENTOS TEÓRICOS</b>                       | <b>37</b> |

| PRINCÍPIOS DE OPERAÇÃO                            | 37        |

| MODOS DE OPERAÇÃO                                 | 40        |

| INTEGRIDADE                                       | 40        |

| MECANISMOS DE PROTEÇÃO DOS REGISTRADORES          | 41        |

| PINOS MULTIPLEXÁVEIS                              | 42        |

| FONTES DE SINAIS DE RELÓGIO                       | 43        |

| TEMPORIZADORES DEDICADOS                          | 44        |

| Temporizador de Interrupções Periódicas           | 44        |

| Temporizador de Interrupções Periódicas Síncronas | 44        |

| Temporizador de Pulso Único                       | 45        |

| Temporizador de Vigilância                        | 45        |

| Relógio em Tempo Real                             | 46        |

| <b>STM32H7A3</b>                                  | <b>48</b> |

| Fontes de Sinais de Relógio                       | 48        |

| TIM6/TIM7                                         | 55        |

| Systick (Tick do Sistema)                         | 57        |

| Temporizador de Baixo Consumo (LPTIM)             | 58        |

| Watchdogs                                         | 62        |

| Real Time Clock (RTC)                             | 64        |

| GPIO: Pinos Multiplexáveis                        | 68        |

## INTRODUÇÃO

A gestão do tempo em sistemas embarcados representa um elemento crítico que exerce impacto direto sobre a precisão, confiabilidade e eficiência desses sistemas. A habilidade de medir e controlar o tempo de maneira precisa, bem como coordenar atividades de forma eficaz, é um

requisito fundamental em diversos setores, englobando automotivo, médico, aeroespacial, eletrônico e outros. Essa competência possibilita a sincronização de eventos, a geração de sinais periódicos e a medição precisa de intervalos de tempo. Na gestão do tempo de sistemas embarcados, existem duas tecnologias essenciais de temporização: os **relógios digitais**, ou temporizadores de *software*, e os **relógios analógicos**, ou temporizadores de *hardware*. Os relógios mecânicos são um exemplo clássico de temporizadores analógicos, onde a precisão é determinada pela qualidade das engrenagens e da construção do relógio. Em comparação com os relógios digitais, eles são geralmente menos precisos e requerem manutenção periódica para funcionar de maneira confiável. Com a ascensão da eletrônica digital, os relógios digitais, que utilizam circuitos de temporizadores digitais, tornaram-se mais comuns devido à sua precisão e facilidade de uso. A estabilidade e precisão dos temporizadores digitais são cruciais em sistemas microcontrolados, e para garantir a precisão e estabilidade dos temporizadores digitais integrados em microcontroladores, esses temporizadores devem utilizar sinais de *clock* gerados no microcontrolador a partir do *clock* geral, fornecendo uma base sólida para a contagem de tempo e a execução precisa de operações temporizadas.

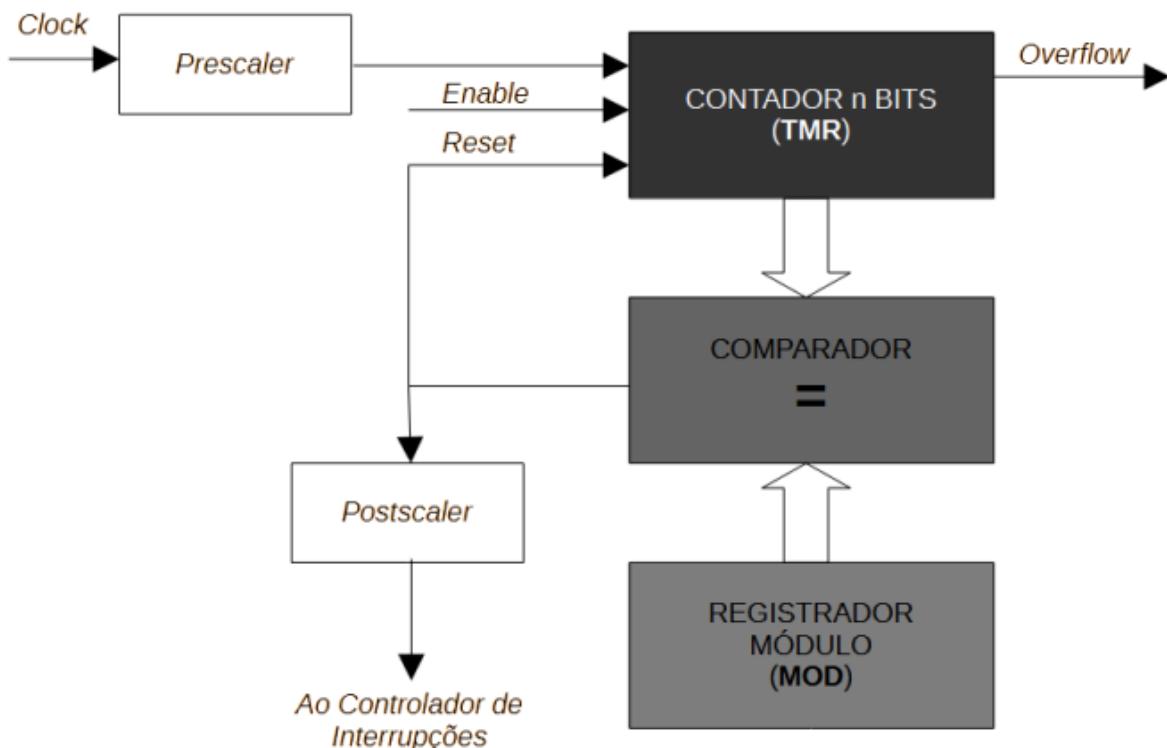

Os temporizadores podem variar em tipo e função, incluindo temporizadores básicos, temporizadores avançados, temporizadores de vigilância (em inglês, *watchdog*) e relógios em tempo real (em inglês, *Real Time Clock* – RTC). **Temporizadores básicos** são usados para medir intervalos de tempo e gerar eventos periódicos, enquanto **temporizadores avançados**, que frequentemente possuem recursos como controle de PWM (do inglês *Pulse Width Modulation*), captura e comparação, são projetados para aplicações que exigem alta precisão e controle detalhado. Os **temporizadores de *watchdog***, por outro lado, são críticos para garantir a confiabilidade do sistema, monitorando a operação do microcontrolador e reiniciando-o em caso de falha. O **RTC**, por sua vez, é um temporizador especializado em manter a contagem precisa do tempo real, incluindo horas e datas, mesmo quando o microcontrolador está em modo de baixo consumo ou desconectado da fonte principal de energia.

Microcontroladores, como os da série STM32, frequentemente incorporam uma ampla gama de temporizadores digitais para atender a diversas necessidades de aplicação. Essa variedade permite que o microcontrolador se adapte a diferentes requisitos, como controle preciso de motores, geração de sinais complexos, medição precisa de intervalos de tempo e gerenciamento de eventos. Além disso, temporizadores especializados, como os de *watchdog* e o RTC, garantem a confiabilidade do sistema e a manutenção contínua do tempo, mesmo quando a fonte principal de energia está desligada. Essa diversidade proporciona aos desenvolvedores a flexibilidade necessária para escolher o temporizador mais adequado para cada projeto, otimizando a eficiência e a confiabilidade do sistema embarcado.

## PROJETOS-EXEMPLO

Você já se perguntou como um temporizador digital, realmente funciona? O que faz um temporizador digital contar o tempo com tanta precisão? Seria a programação deles algo simples ou envolve camadas mais profundas de controle? Vamos descobrir neste roteiro as configurações dos

temporizadores do microcontrolador STM32H73A para geração precisa de interrupções periódicas (em inglês, *periodic interrupt timer*), geração de interrupções periódicas síncronas como sinal de relógio do processador (em inglês, *System Tick*), disparo único (em inglês, *one-shot*), relógio digital (em inglês, *real time clock*) e vigilância (em inglês, *watchdog*)?

## Projeto com o TIM6 usando CMSIS

Nos Roteiros 1 e 2, controlamos a alternância do LED verde manualmente ou usando um laço de espera programado, sem qualquer precisão no tempo entre cada mudança de estado. Mas agora que sabemos que o STM32H7A3 possui temporizadores digitais integrados e que todos eles podem gerar interrupções via NVIC, surge uma questão interessante: “É possível deixarmos o próprio microcontrolador determinar, com precisão, o instante exato em que o LED deve mudar de estado?” Essa abordagem automatiza o controle de tempo e nos permite obter uma precisão muito maior. Mas para isso, precisamos responder algumas perguntas-chave: (1) Como configurar um temporizador para gerar interrupções periódicas? (2) Como configurar NVIC e ativar sua linha de interrupção no NVIC? (3) Como programar a função ISR para alternar o estado do LED no momento exato? Vamos então criar um projeto onde o temporizador de propósito geral, [TIM6](#), gera uma interrupção periódica e faz o LED verde piscar a uma frequência fixa de 1Hz, sem desperdício de processamento e com total precisão! Está pronto para dominar essa técnica essencial e tornar seus projetos ainda mais eficientes? Vamos começar?

1. Crie um projeto com o nome “Timer\_CMSIS”, com suporte ao CMSIS, como foi feito nos Roteiros 2, 3 e 4 ([adicionando as pastas](#) com os arquivos de suporte `stm32h7a3xxq.h` e `core_cm7.h` e colocando o “include” do arquivo `stm32h7a3xxq.h` no “main.c”).

2. Vamos inicialmente adicionar a configuração de PB0 como saída para acionar o LED verde. No início da função “main”, adicione o seguinte código:

```

int main(void)

{

// Inicializa GPIOB, pino 0 (PB0)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN_Msk; // GPIOB clock enable

// PB0 como saída digital

GPIOB->MODER &= ~(GPIO_MODER_MODE0_Msk);

GPIOB->MODER |= GPIO_MODER_MODE0_0;

GPIOB->OTYPER &= ~(GPIO_OTYPER_OT0_Msk); // PB0 como push-pull

for (;;) ;

}

```

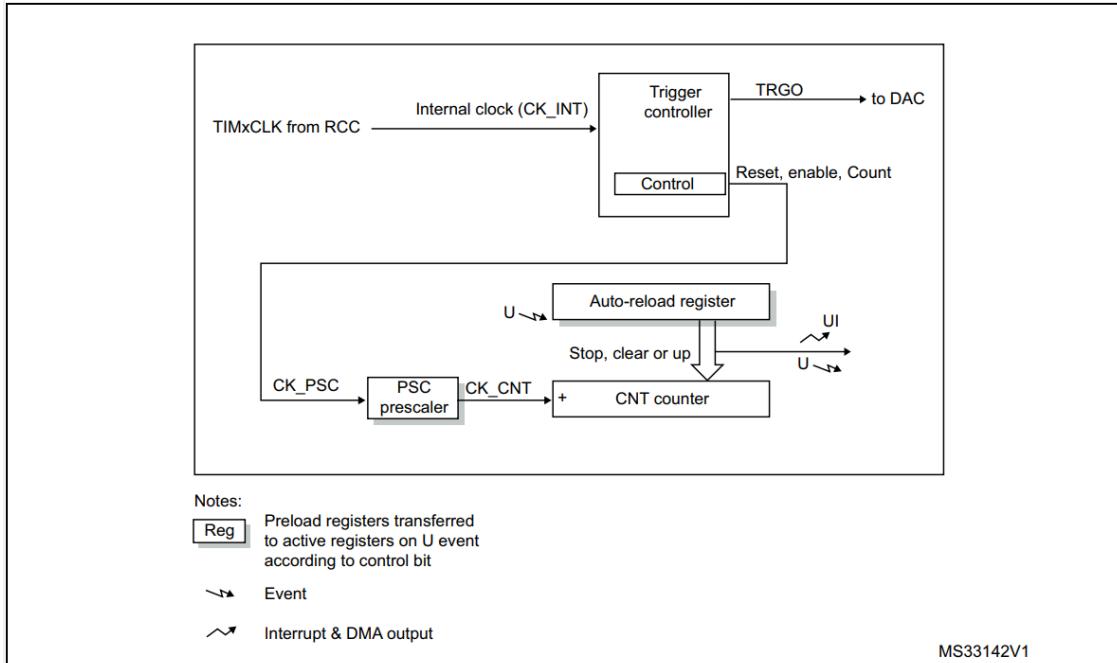

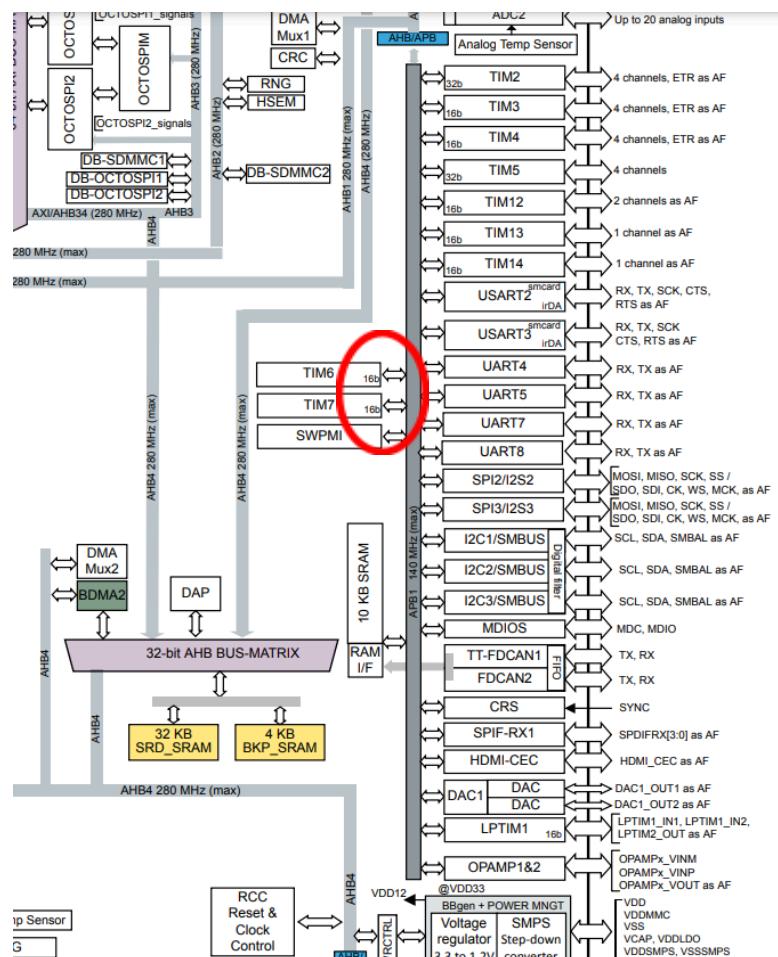

3. Agora precisamos configurar um dos *timers* disponíveis para contar 500ms e reiniciar. O reinício do *timer* irá realizar uma interrupção, cujo tratamento é a inversão do estado do LED. Para esta aplicação, os *Timers* mais simples são suficientes. O [Manual de Referência](#) apresenta os vários tipos de *Timers* com uma grande gama de modos de operação nos capítulos 43 a 45, e os mais básicos no [capítulo 46](#), que são o TIM6 e o TIM7. Vamos usar o TIM6 para gerar a interrupção periódica. O *timer* usa a frequência de *clock* TIMxCLK de seu barramento para realizar a contagem de tempo.

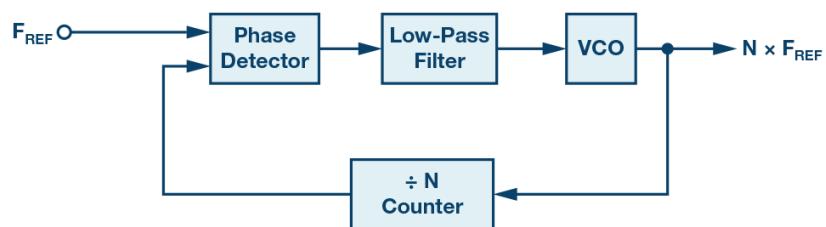

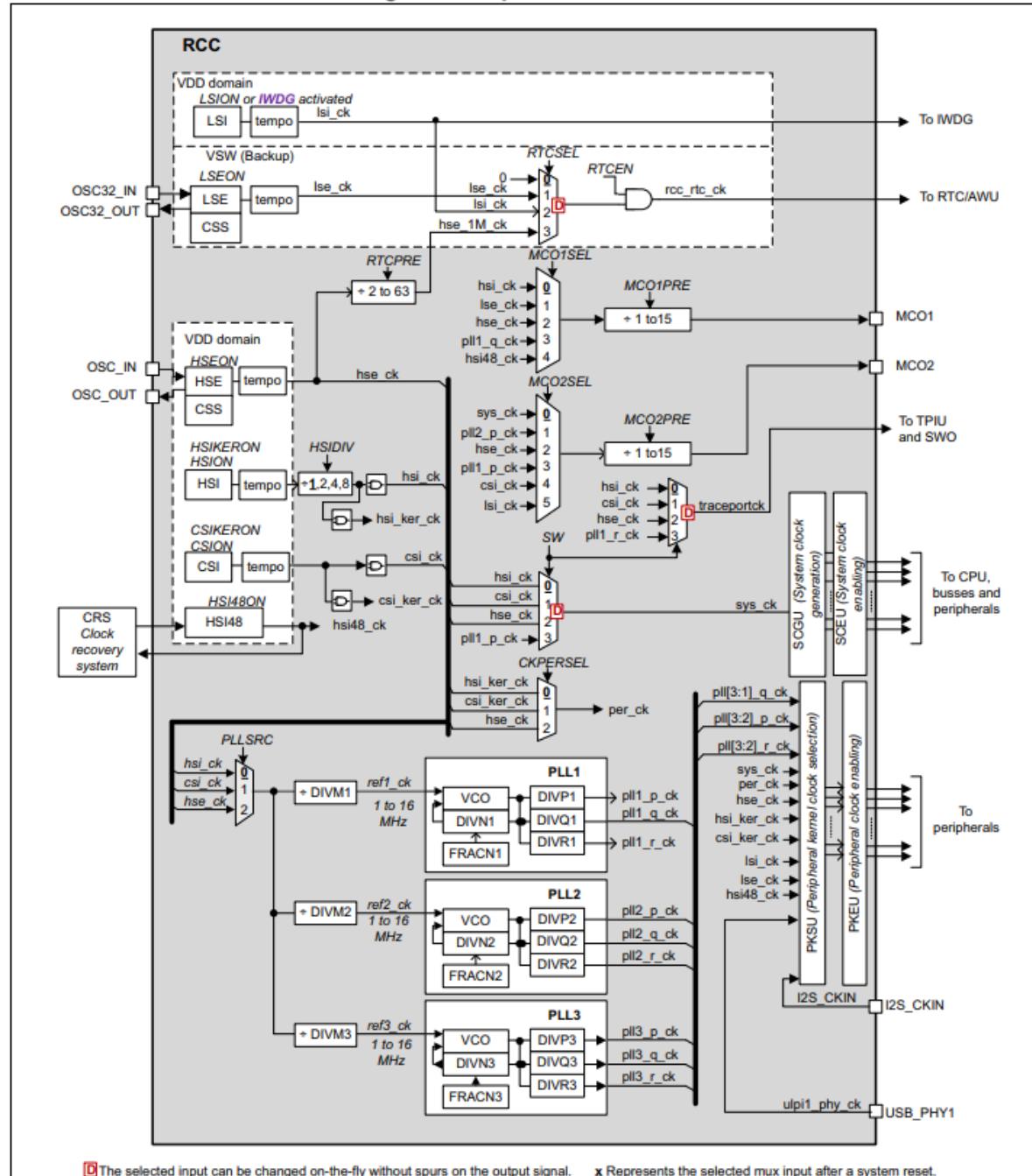

A [figura 1 do Datasheet](#) do microcontrolador mostra que o TIM6 está ligado ao barramento APB1 através de 16 linhas de *bits*. Ao criar um projeto vazio (“Empty”) no STM32CubeIDE, a fonte de sinal de relógio padrão selecionada é o HSI, pois o campo [RCC\\_CFGR\\_SW](#) são resetados em 0b000. Nesse processo, o campo HSIDIV no registrador [RCC\\_CR](#), como no campo [RCC\\_CDCFGR1\\_CDDPRE1](#), é configurado com o valor 1. Portanto, após um *reset* ou quando o microcontrolador é energizado, a frequência do sinal de *clock* geral está configurada em 64 MHz. O [barramento APB1 recebe o sinal da frequência 64MHz](#), pois o campo [RCC\\_CDCFGR1\\_HPRE](#) de HSIDIV é configurado como 1, e assim a frequência de entrada do *timer* é 64MHz.

4. Como o *timer* é de 16 *bits*, ele pode contar até, no máximo, 65536 pulsos (de 0 a 65535). Com um *clock* de 64MHz, o tempo máximo de contagem seria de 1024 $\mu$ s. Para ampliar o tempo de contagem para 500ms, usaremos o *prescaler* PSC do *timer*, também de 16 *bits*. Podemos dividir o *clock* por 64000 no *prescaler*, fazendo com que o contador principal receba um *clock* de 1kHz. Assim, cada unidade do *timer* corresponde a 1ms, e podemos configurar o *timer* para contar 500 pulsos.

**IMPORTANTE:** Tanto o contador do *prescaler* como o do *timer* em si são síncronos, ou seja, ao atingir o valor de contagem definido eles apenas serão zerados no próximo pulso de *clock*. Assim, para contar  $n$  pulsos, o contador deve contar de 0 até  $n - 1$ . Por isso, os valores definidos devem ser os calculados no parágrafo anterior subtraídos de 1. Ou seja, precisamos colocar o valor de 63999 no módulo de contagem do *prescaler* e 499 no módulo de contagem do contador principal.

5. É necessário ativar o *timer*, da mesma forma que ativamos o GPIOB. O TIM6 tem seu *clock gating* ativado pelo *bit* 4 do registrador [RCC\\_APB1LENR](#).

#### 8.7.43 RCC APB1 clock register ([RCC\\_APB1LENR](#))

Address offset: 0x148

Reset value: 0x0000 0000

|         |         |        |      |       |      |          |         |         |         |        |         |         |          |          |           |

|---------|---------|--------|------|-------|------|----------|---------|---------|---------|--------|---------|---------|----------|----------|-----------|

| UART8EN | UART7EN | DAC1EN | Res. | CECEN | Res. | Res.     | Res.    | I2C3EN  | I2C2EN  | I2C1EN | UART5EN | UART4EN | USART3EN | USART2EN | SPDIFRXEN |

| rw      | rw      | rw     |      | rw    |      |          |         | rw      | rw      | rw     | rw      | rw      | rw       | rw       | rw        |

| 15      | 14      | 13     | 12   | 11    | 10   | 9        | 8       | 7       | 6       | 5      | 4       | 3       | 2        | 1        | 0         |

| SPI3EN  | SPI2EN  | Res.   | Res. | Res.  | Res. | LPTIM1EN | TIM14EN | TIM13EN | TIM12EN | TIM7EN | TIM6EN  | TIM5EN  | TIM4EN   | TIM3EN   | TIM2EN    |

| rw      | rw      |        |      |       |      | rw       | rw      | rw      | rw      | rw     | rw      | rw      | rw       | rw       | rw        |

Para isso, teremos que adicionar a seguinte linha de código se usar as macros da interface CMSIS:

```

RCC->APB1LENR |= RCC_APB1LENR_TIM6EN;

```

6. Agora vamos configurar os parâmetros do *timer*. Antes da configuração, devemos gerar manualmente um evento de atualização para garantir que o TIM6 esteja corretamente inicializado e sincronizado no microcontrolador STM32H7. Para isso, ativamos o *bit* [TIM6\\_EGR\\_UG](#) e aguardamos a conclusão da operação.

```

TIM6->EGR |= TIM_EGR_UG_Msk; //forca atualizacao imediata de TIM6

while (TIM6->EGR & TIM_EGR_UG); //aguarda a conclusao do evento de atualizacao

```

O valor de divisão do *prescaler* é definido no registrador [TIM6\\_PSC](#) e o valor máximo de contagem é definido no registrador de *auto-reload* [TIM6\\_ARR](#). Ambos os registradores estão mapeados no espaço de endereçamento do processador e são acessados através da struct [TIM\\_TypeDef](#) da interface CMSIS definida no arquivo [stm32h7a3xxq.h](#).

```

1399 typedef struct

1400 {

1401     __IO uint32_t CR1;           /*!< TIM control register 1,          Address offset: 0x00 */

1402     __IO uint32_t CR2;           /*!< TIM control register 2,          Address offset: 0x04 */

1403     __IO uint32_t SMCR;          /*!< TIM slave mode control register, Address offset: 0x08 */

1404     __IO uint32_t DIER;          /*!< TIM DMA/interrupt enable register, Address offset: 0x0C */

1405     __IO uint32_t SR;            /*!< TIM status register,             Address offset: 0x10 */

1406     __IO uint32_t EGR;           /*!< TIM event generation register,  Address offset: 0x14 */

1407     __IO uint32_t CCMR1;          /*!< TIM capture/compare mode register 1, Address offset: 0x18 */

1408     __IO uint32_t CCMR2;          /*!< TIM capture/compare mode register 2, Address offset: 0x1C */

1409     __IO uint32_t CCER;           /*!< TIM capture/compare enable register, Address offset: 0x20 */

1410     __IO uint32_t CNT;           /*!< TIM counter register,           Address offset: 0x24 */

1411     __IO uint32_t PSC;           /*!< TIM prescaler,                 Address offset: 0x28 */

1412     __IO uint32_t ARR;           /*!< TIM auto-reload register,      Address offset: 0x2C */

1413     __IO uint32_t RCR;           /*!< TIM repetition counter register, Address offset: 0x30 */

1414     __IO uint32_t CCR1;          /*!< TIM capture/compare register 1, Address offset: 0x34 */

1415     __IO uint32_t CCR2;          /*!< TIM capture/compare register 2, Address offset: 0x38 */

1416     __IO uint32_t CCR3;          /*!< TIM capture/compare register 3, Address offset: 0x3C */

1417     __IO uint32_t CCR4;          /*!< TIM capture/compare register 4, Address offset: 0x40 */

1418     __IO uint32_t BDTR;          /*!< TIM break and dead-time register, Address offset: 0x44 */

1419     __IO uint32_t DCR;           /*!< TIM DMA control register,       Address offset: 0x48 */

1420     __IO uint32_t DMAR;          /*!< TIM DMA address for full transfer, Address offset: 0x4C */

1421     uint32_t RESERVED1;         /*!< Reserved, 0x50                */

1422     __IO uint32_t CCMR3;          /*!< TIM capture/compare mode register 3, Address offset: 0x54 */

1423     __IO uint32_t CCR5;           /*!< TIM capture/compare register5, Address offset: 0x58 */

1424     __IO uint32_t CCR6;           /*!< TIM capture/compare register6, Address offset: 0x5C */

1425     __IO uint32_t AF1;            /*!< TIM alternate function option register 1, Address offset: 0x60 */

1426     __IO uint32_t AF2;            /*!< TIM alternate function option register 2, Address offset: 0x64 */

1427     __IO uint32_t TISEL;          /*!< TIM Input Selection register, Address offset: 0x68 */

1428 } TIM_TypeDef;

```

Lembre-se de que os valores a serem escritos nos registradores são os valores calculados menos 1:

```

TIM6->PSC = 64000 - 1;

TIM6->ARR = 500 - 1;

```

7. Vamos ainda iniciar com o contador em zero. Para isso, basta escrever o valor diretamente no registrador que guarda a contagem atual:

```

TIM6->CNT = 0;

```

8. Precisamos agora desmascarar a interrupção, colocando “1” no *bit* 0 do registrador [TIM6\\_DIER](#), limpar a flag em [TIM6\\_SR](#) e configurar a prioridade (vamos usar o valor 1) e habilitar a interrupção no [NVIC](#), como foi feito no Roteiro 3.

```

TIM6->DIER |= TIM_DIER_UIE;

TIM6->SR = ~TIM_SR UIF_Msk;

```

Para determinar o vetor de interrupção associado ao TIM6, consultamos a [Tabela 123 do Manual de Referência](#), onde encontramos que o número do vetor é 54. A interface CMSIS define o tipo [IRQn\\_Type](#) como um tipo enumerado que inclui a constante [TIM6\\_DAC IRQn](#), com o valor 54, conforme definido no arquivo [stm32h7a3xxq.h](#). As funções CMSIS para configurar o nível de prioridade em “1” no *byte* 2 (54&~0xFFFFFFF) do registrador de prioridade [NVIC\\_IPRn](#), onde n = 54>>2 = 13 e para habilitar a interrupção da linha [IRQn](#) são, respectivamente [NVIC\\_SetPriority](#) e [NVIC\\_EnableIRQ](#), sendo essas funções definidas no arquivo

C:/users/ea701/STM32Cube/Repository/STM32Cube\_FW\_H7\_V1.11.2/Drivers/CMSIS/Include/core\_cm7.h.

```

NVIC_SetPriority(TIM6_DAC IRQn, 1);

NVIC_EnableIRQ(TIM6_DAC IRQn);

```

A macro **TIM6\_DAC IRQn** está definida em C:/users/ea701/STM32Cube/Repository/STM32Cube\_FW\_H7\_V1.11.2/Drivers/CMSIS/Device/ST/STM32H7xx/Include/stm32h7a3xxq.h.

Percebeu que não configuramos o controlador EXTI para rotear o sinal de interrupção como ocorreu com os sinais provenientes dos pinos de entrada dos módulos GPIO no [Roteiro 3](#)? Tem alguma ideia por onde os sinais circulam? Se não surgir nenhuma explicação plausível, não se apavore. Vamos entender isso mais adiante,

9. Até aqui, configuramos os parâmetros do contador e a sua interrupção. No código, ainda é necessário iniciar a contagem, habilitando o contador a receber os pulsos de *clock*. Isto é feito no *bit 0* do registrador de controle ([TIM6\\_CR1](#)):

```

TIM6->CR1 |= TIM_CR1_CEN;

```

10. Para finalizar, é necessário definir a ISR com o código que irá inverter o estado do LED. No arquivo `Startup/startup_stm32h7a3zitxq.s`, é declarada a função de nome **TIM6\_DAC1\_IRQHandler** como ISR da interrupção do TIM6.

```

199 .word TIM6_DAC1_IRQHandler          /* TIM6 global interrupt

200 .word TIM7_IRQHandler             /* TIM7 global interrupt

```

Antes da função *main*, insira a seguinte função:

```

void TIM6_DAC1_IRQHandler(void) {

static uint8_t status = 0;

if (TIM6->SR & TIM_SR_UIF) { // Testa a flag de atualização

// Limpa a flag de atualização escrevendo ZERO

TIM6->SR &= ~TIM_SR_UIF;

if (status) { // LED ligado

GPIOB->BSRR = GPIO_BSRR_BR0; // Desliga LED

status = 0;

} else { // LED desligado

GPIOB->BSRR = GPIO_BSRR_BS0; // Liga LED

status = 1;

}

}

}

```

Verifique o uso do registrador de estado [TIM6\\_SR](#) para confirmar se o *bit* de *flag* de interrupção está setado antes de tratar o evento. Conforme descrito no Manual de Referência, esse *bit* é automaticamente setado pelo *hardware* quando o contador atinge o valor configurado no **TIM6\_ARR** e o contador [TIM6\\_CNT](#) é resetado. O *bit* deve ser limpo utilizando a técnica de “*read/clear write0 (rc\_w0)*”, ou seja, escrevendo um valor que tem o *bit* de *flag* específico definido como “0” e todos os outros *bits* em “1”, para remover a solicitação de interrupção.

#### 46.4.4 TIMx status register (TIMx\_SR)(x = 6 to 7)

Address offset: 0x10

Reset value: 0x0000

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0            |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|--------------|

| Res. | UIF<br>rc_w0 |

Bits 15:1 Reserved, must be kept at reset value.

Bit 0 **UIF**: Update interrupt flag

This bit is set by hardware on an update event. It is cleared by software.

0: No update occurred.

1: Update interrupt pending. This bit is set by hardware when the registers are updated:

- At overflow or underflow regarding the repetition counter value and if UDIS = 0 in the TIMx\_CR1 register.

- When CNT is reinitialized by software using the UG bit in the TIMx\_EGR register, if URS = 0 and UDIS = 0 in the TIMx\_CR1 register.

Note que, neste caso, há apenas um evento de interrupção ativo (o periférico DAC1 está inativo) associado à linha IRQ54, conforme ilustrado no [diagrama de blocos na Figura 488 do Manual de Referência](#). Como é único o evento que pode gerar uma solicitação na linha IRQ54, não é necessário identificar a fonte do evento de interrupção que gerou a solicitação. Porém, é uma boa prática de programação testar o *flag* sempre, pois em uma eventual modificação do projeto, outras fontes de interrupção que usam o mesmo vetor podem ser adicionadas.

Assim, o código completo do arquivo “main.c” fica:

```

#include <stdint.h>

#include <stm32h7a3xxq.h>

void TIM6_DAC_IRQHandler(void) {

static uint8_t status = 0;

if (TIM6->SR & TIM_SR_UIF) { // Testa a flag de atualização

// Limpa a flag de atualização escrevendo ZERO

TIM6->SR &= ~TIM_SR_UIF;

if(status) { // LED ligado

GPIOB->BSRR = GPIO_BSRR_BR0; // Desliga LED

status = 0;

} else { // LED desligado

GPIOB->BSRR = GPIO_BSRR_BS0; // Liga LED

status = 1;

}

}

}

int main(void)

{

// Inicializa GPIOB, pino 0 (PB0)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN_Msk; // GPIOB clock enable

// PB0 como saída digital

GPIOB->MODER &= ~(GPIO_MODER_MODE0_Msk);

GPIOB->MODER |= GPIO_MODER_MODE0_0;

GPIOB->OTYPER &= ~(GPIO_OTYPER_OT0_Msk); // PB0 como push-pull

// Inicializa o TIM6

RCC->APB1LENR |= RCC_APB1LENR_TIM6EN; // clock gating

TIM6->PSC = 64000 - 1; // prescaler

TIM6->ARR = 500 - 1; // Auto-reload, modulo de contagem

TIM6->CNT = 0; // Zerando o contador

```

```

// Configura_interrupcao

TIM6->DIER |= TIM_DIER_UIE; // Mascara de_interrupcao de atualizacao

NVIC_SetPriority(TIM6_DAC IRQn, 1); // Prioridade 1

NVIC_EnableIRQ(TIM6_DAC IRQn); // Habilita_interrupcao

// Inicia a contagem de tempo

TIM6->CR1 |= TIM_CR1_CEN;

/* Loop forever */

for(;;);

}

```

11. Faça o “Build” e o “Debug” e veja o funcionamento do programa.

12. Vamos analisar e desmembrar o comportamento do módulo para compreender detalhadamente suas operações e características. Em primeiro lugar, reinicie o programa com “*Terminate and Relaunch*” (ícone quadrado vermelho e triângulo verde). Coloque um *breakpoint* na linha da instrução “`for(;;);`”.

Faça ações combinadas de “Pause” e “Resume” para ver a variação do conteúdo de `TIM6_CNT` e descobrir experimentalmente se o temporizador `TIM6` é de contagem progressiva ou regressiva e se as interrupções ocorrem em *overflow* ou *underflow*.

13. Vamos verificar se o fluxo de controle é deslocado periodicamente para a ISR `TIM6_DAC_IRQHandler`. Desloque o *breakpoint* para dentro de `TIM6_DAC_IRQHandler` e continue (“Resume”) a execução. Ao pausar o fluxo dentro da ISR, execute a ISR passo-a-passo, para monitorar o valor do *bit* de *flag* de interrupção `TIM6_SR UIF`. Qual instrução é responsável por limpá-lo? É uma operação de mascaramento ou de atribuição direta? Remova o *breakpoint* e continue (“Resume”) o fluxo de execução. Reinicie (“*Terminate and Relaunch*”) a execução.

14. Alternadamente, continue (Resume) e pause (“Pause”) a execução. Em cada pausa, ajuste o valor do *prescaler* em `TIM6_PSR`. Observe como a frequência de piscada do LED muda quando você aumenta o valor do prescaler. E como ela se comporta quando o valor do *prescaler* é reduzido? Essas variações nos intervalos de piscadas estão de acordo com suas expectativas?

## Projeto com o *SysTick* usando CMSIS

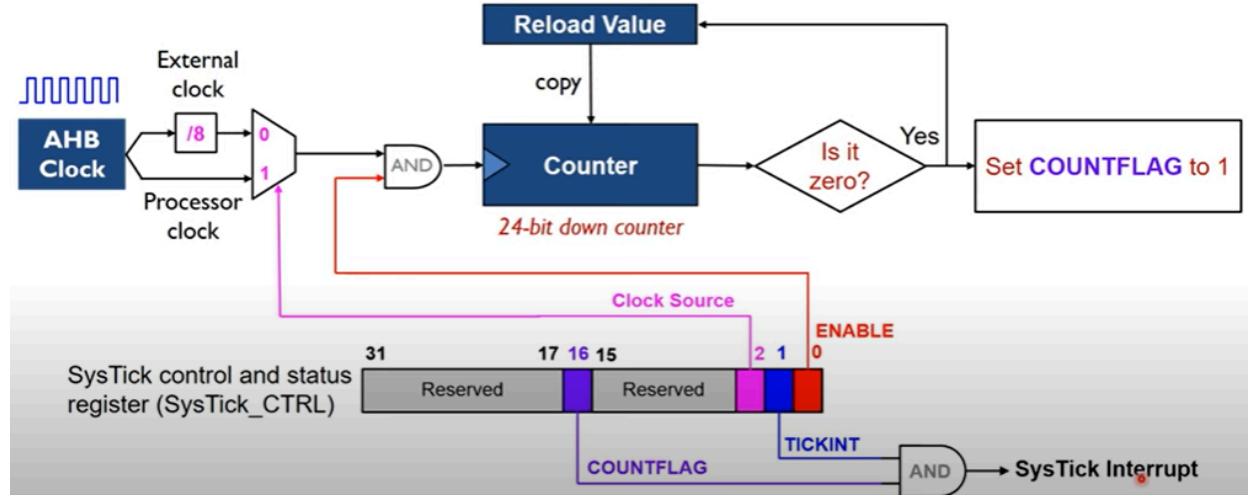

Se você precisasse desenvolver um sistema operacional em tempo real (em inglês, *Real Time Operating System*), onde a cada 1ms fosse necessário verificar novos processos e alternar entre aqueles em execução, o que você faria? Observe que nesse cenário, precisão absoluta nas interrupções periódicas não é apenas desejável. É essencial! Mas há um detalhe ainda mais crítico: essas interrupções precisam estar perfeitamente sincronizadas com o sinal de relógio do processador para garantir que o sistema funcione de forma eficiente e previsível. Como garantir essa sincronização? Felizmente, microcontroladores com arquitetura ARM Cortex-M já possuem um temporizador dedicado para essa tarefa: o *SysTick* (do inglês *System Tick*). Esse temporizador de 24 *bits* tem a grande vantagem de operar exatamente na frequência do processador, garantindo a máxima precisão e sincronização.

Com essa ferramenta à disposição, a ferramenta oferece o controle necessário para garantir a precisão do agendamento e o desempenho do sistema. Agora, vamos explorar como configurar o SysTick para gerar interrupções periódicas a cada 1ms, síncronas com o sinal de relógio do processador. Aprenderemos a usar essas interrupções para implementar uma função *Delay*, que interrompe a execução do programa por um tempo determinado em milissegundos. Siga as instruções a seguir.

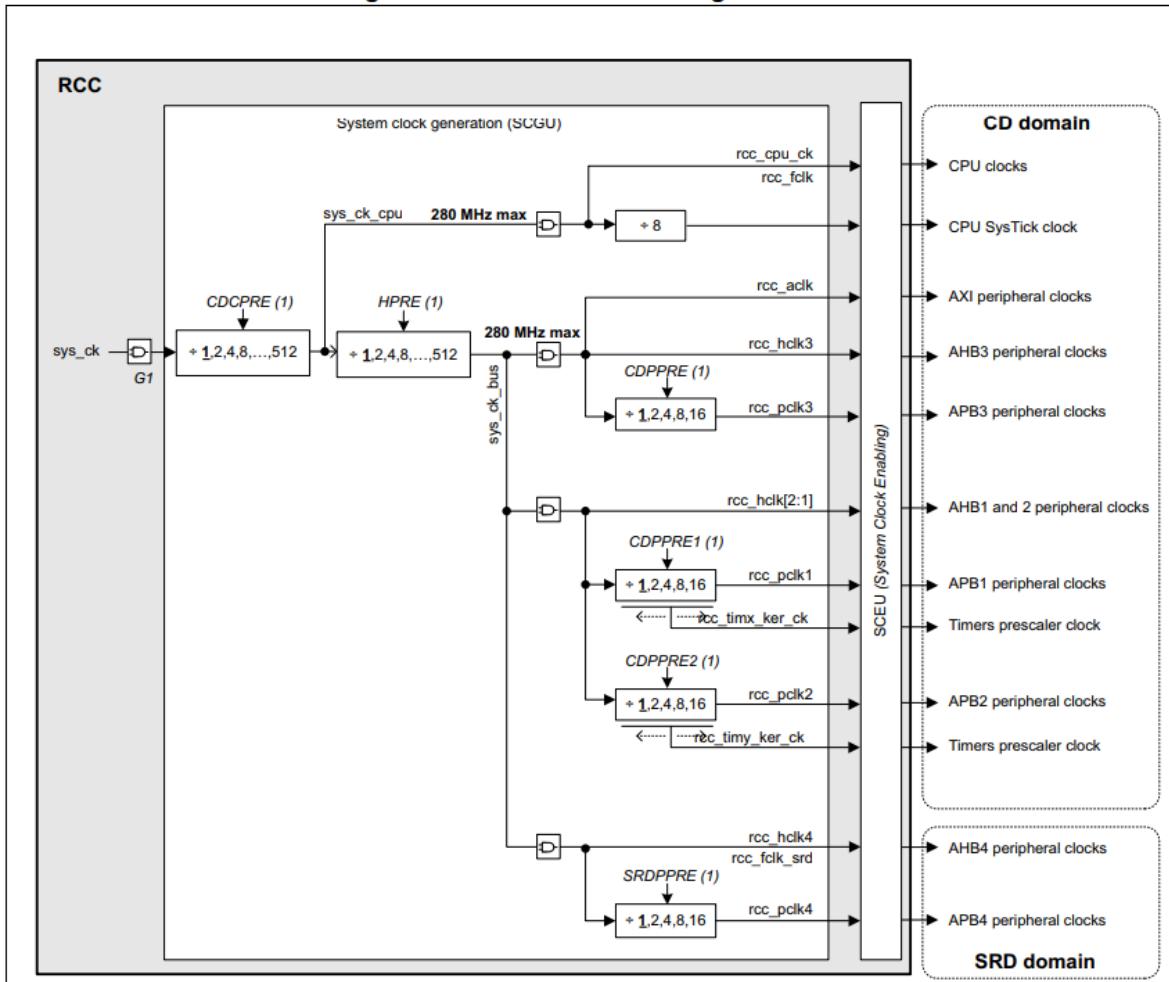

1. Crie o projeto “Delay\_1ms”, seguindo o mesmo procedimento utilizado no projeto anterior. O *timer SysTick* tem 4 registradores. Um deles, o SYST\_CALIB, é opcional, e guarda um valor de calibração fina para o temporizador; ele não será usado neste exemplo. Primeiro precisamos definir o valor máximo de contagem do *Systick* para a contagem de 1ms. A frequência inicial dos *clocks* AHB é de 64MHz. Vamos usar o *prescaler* RCC\_CDCFGR1\_CDCCPRE dividindo esta frequência por 8, assim teremos 8MHz no contador. Para contar 1ms, serão 8000 pulsos. Assim, devemos carregar no registrador SYST\_RVR (*Reload Value*) o valor 8000-1, pois o *Systick* também possui seu *reset* síncrono.

2. O segundo registrador que vamos configurar é o do valor corrente do contador. O registrador SYST\_CVR permite ler o valor atual, bem como modificar o valor ao ser escrito. Vamos carregar zero neste registrador.

3. Por fim, precisamos configurar o registrador SYST\_CSR (*SysTick Control and Status*). Este registrador usa apenas 3 *bits* para controle e um *bit* para indicar o status. Os *bits* de controle habilitam o *clock* no contador, permitindo que ele realize a contagem (*bit* 0 em “1”), habilitam a interrupção (*bit* 1 em “1”) e definem se a fonte do *clock* é externa(*bit* 2 em “0”) ou usa a mesma fonte do *clock* do processador (*bit* 2 em “1”). O *bit* 16 é o *flag* que, quando em “1”, indica que o contador chegou a zero, sendo apagado automaticamente quando o registrador é lido. O endereço da sua ISR está localizado na 16<sup>a</sup> posição da Tabela de Vetores de Interrupção, o que significa que o seu número do vetor é 15. **Obs:** Como não há uma linha IRQn específica associada ao SysTick, não é necessária nenhuma configuração no NVIC. A prioridade é pré-definida e a interrupção é permanentemente habilitada, podendo apenas ser mascarada.

Table 123. NVIC<sup>(1)</sup>

| Signal  | Priority | NVIC position | Acronym      | Description                                                                                 | Address offset              |

|---------|----------|---------------|--------------|---------------------------------------------------------------------------------------------|-----------------------------|

| -       | -        | -             | -            | Reserved                                                                                    | 0x0000 0000                 |

| -       | -3       | -             | Reset        | Reset                                                                                       | 0x0000 0004                 |

| -       | -2       | -             | NMI          | Non maskable interrupt.<br>The RCC Clock Security System (CSS) is linked to the NMI vector. | 0x0000 0008                 |

| -       | -1       | -             | HardFault    | All classes of fault                                                                        | 0x0000 000C                 |

| -       | 0        | -             | MemManage    | Memory management                                                                           | 0x0000 0010                 |

| -       | 1        | -             | BusFault     | Prefetch fault,<br>memory access fault                                                      | 0x0000 0014                 |

| -       | 2        | -             | UsageFault   | Undefined instruction or illegal state                                                      | 0x0000 0018                 |

| -       | -        | -             | -            | Reserved                                                                                    | 0x0000 001C-<br>0x0000 002B |

| -       | 3        | -             | SVCall       | System service call<br>via SWI instruction                                                  | 0x0000 002C                 |

| -       | 4        | -             | DebugMonitor | Debug monitor                                                                               | 0x0000 0030                 |

| -       | -        | -             | -            | Reserved                                                                                    | 0x0000 0034                 |

| -       | 5        | -             | PendSV       | Pendable request for system service                                                         | 0x0000 0038                 |

| -       | 6        | -             | SysTick      | System tick timer                                                                           | 0x0000 003C                 |

| wwdg_it | 7        | 0             | WWDG         | Window Watchdog interrupt                                                                   | 0x0000 0040                 |

4. Crie um projeto com suporte a CMSIS, similar ao anterior e inclua os caminhos dos arquivos-cabeçalho [stm32h7a3xxq.h e core\\_cm7.h](#). Nomeie o projeto como “Delay\_1ms” e abra o arquivo “main.c”. Antes da função “main()”, adicione a seguinte função para realizar a inicialização do Systick:

```

void SysTick_Init(void) {

// Clock de sistema: 64 MHz

// Systick usa o clock dividido por 8: 64 MHz / 8 = 8 MHz

// Precisamos de uma interrupção a cada 1ms, então:

// Contador = 8 MHz / 1000 = 8000 ticks

uint32_t reload_value = 8000 - 1; // Subtraímos 1 porque o contador vai de 0 a reload_value

// Configurando o Systick Reload Value

SysTick->LOAD = reload_value;

// Resetando o valor atual do contador

SysTick->VAL = 0;

// Configurando uso do clock da CPU

SysTick->CTRL |= SysTick_CTRL_CLKSOURCE_Msk;

// Configurando o Systick para usar o clock do processador

SysTick->CTRL |= SysTick_CTRL_CLKSOURCE_Msk;

// Iniciar o contador

SysTick->CTRL = SysTick_CTRL_ENABLE_Msk; // Habilita o Systick

}

```

Observe que utilizamos o tipo de dado `Systick_Type` e as macros da interface CMSIS, definido no arquivo-cabeçalho `core_cm7.h`, para acessar os registradores do módulo Systick.

```

976 /*

977   \brief Structure type to access the System Timer (SysTick).

978 */

979 typedef struct

980 {

981   __IOM uint32_t CTRL;           /*!< Offset: 0x000 (R/W) SysTick Control and Status Register */

982   __IOM uint32_t LOAD;          /*!< Offset: 0x004 (R/W) SysTick Reload Value Register */

983   __IOM uint32_t VAL;           /*!< Offset: 0x008 (R/W) SysTick Current Value Register */

984   __IM uint32_t CALIB;         /*!< Offset: 0x00C (R/) SysTick Calibration Register */

985 } SysTick_Type;

```

5. Precisamos ter uma variável que guarda o número de milissegundos restantes na contagem. Esta variável será decrementada pela ISR do *Systick*. Assim, deve ser uma variável global. Logo após as declarações “#include”, declare a variável:

```

uint32_t count; // ms restantes

```

6. Agora vamos implementar a ISR. Na tabela de vetores de interrupção montada no arquivo `startup_stm32h7a3zitxq.s`, o nome da função é definido como “*SysTick\_Handler*”.

```

125 .section .isr_vector, "a",%progbits

126 .type g_pfnVectors, %object

127

128 g_pfnVectors:

129 .word _estack

130 .word Reset_Handler

131 .word NMI_Handler

132 .word HardFault_Handler

133 .word MemManage_Handler

134 .word BusFault_Handler

135 .word UsageFault_Handler

136 .word 0

137 .word 0

138 .word 0

139 .word 0

140 .word SVC_Handler

141 .word DebugMon_Handler

142 .word 0

143 .word PendSV_Handler

144 .word SysTick_Handler

145 .word WWDG_IRQHandler           /* Window Watchdog interrupt */

146 .word PVD_PVM_IRQHandler        /* PVD through EXTI line */

147 .word RTC_TAMP_STAMP_CSS_LSE_IRQHandler /* RTC tamper, timestamp */

148 .word RTC_WKUP_IRQHandler       /* RTC Wakeup interrupt */

```

Assim, entre a declaração da variável global e a função de inicialização do *Systick*, escreva a ISR:

```

void SysTick_Handler(void) {

count--;

}

```

Com isso, a cada milissegundo o valor de “count” será decrementado de 1.

7. Resta ainda a definição da função “Delay”. A função deve carregar a variável “count” com o número de milissegundos da espera, ativar a interrupção do *Systick* para contagem, aguardar o valor chegar a zero, e então desativar *Systick*. Assim, depois da função de inicialização do *Systick*, escreva a função de “Delay”:

```

void Delay(uint32_t ms) {

count = ms; // carrega o valor em ms

SysTick->CTRL |= SysTick_CTRL_TICKINT_Msk;

SysTick->VAL = 0;

while(count); // Loop enquanto "count" é diferente de zero

SysTick->CTRL &= ~SysTick_CTRL_TICKINT_Msk;

}

```

8. Agora vamos implementar um pisca usando a função “Delay”. Na função “main.c” vamos configurar a fonte do *clock* do *Systick* para que seja a mesma do processador, configurar o divisor

de frequência em 8, configurar o pino de saída do LED verde como nos exemplos anteriores, inicializar o *Systick* com a interrupção desativada e alternar o LED entre os estados ligado e desligado usando o “Delay” para espaçar os instantes de alternância. A função “main()” fica assim:

```

int main(void)

{

// Configurar o divisor em 8

RCC->CDCFGR1 &= ~RCC_CDCFGR1_CDCPRE_DIV512_Msk;

RCC->CDCFGR1 |= RCC_CDCFGR1_CDCPRE_DIV8;

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN_Msk;

GPIOB->MODER &= ~(GPIO_MODER_MODE0_Msk);

GPIOB->MODER |= GPIO_MODER_MODE0_0;

GPIOB->OTYPER &= ~(GPIO_OTYPER_OT0_Msk);

SysTick_Init();

for(;;) {

GPIOB->BSRR = GPIO_BSRR_BS0; // Liga LED

Delay(500);

GPIOB->BSRR = GPIO_BSRR_BR0; // Desliga LED

Delay(500);

}

}

```

9. Você deve ter notado que não configuramos o controlador NVIC nem o EXTI, e que o bit de estado SYST\_CTRL\_COUNTFLAG do registrador SysTick->CTRL não foi limpo dentro da rotina de serviço *SysTick\_Handler*. Você conseguiria explicar por quê neste caso o projeto funcionou corretamente? Sei que pode parecer confuso, mas não se preocupem! Vamos explorar isso juntos mais adiante e entender por quê, neste caso específico, não precisamos configurar o NVIC nem limpar o *bit* de estado do SysTick.

10. Faça o “Build” e transfira, no modo “Debug”, o executável para o microcontrolador.

11. Usando combinadamente “Pause” e “Resume”, verifique se o SysTick é um temporizador de contagem progressiva ou regressiva e se a sua interrupção ocorre em *overflow* ou *underflow*. Explique o funcionamento do sistema implementado.

12. Você pode alternar o estado do LED verde diretamente na ISR “*SysTick\_Handler*”, semelhante ao que foi feito no projeto anterior. Valide essa abordagem implementando-a e verificando seu funcionamento.

## Projeto com o LPTIM usando CMSIS

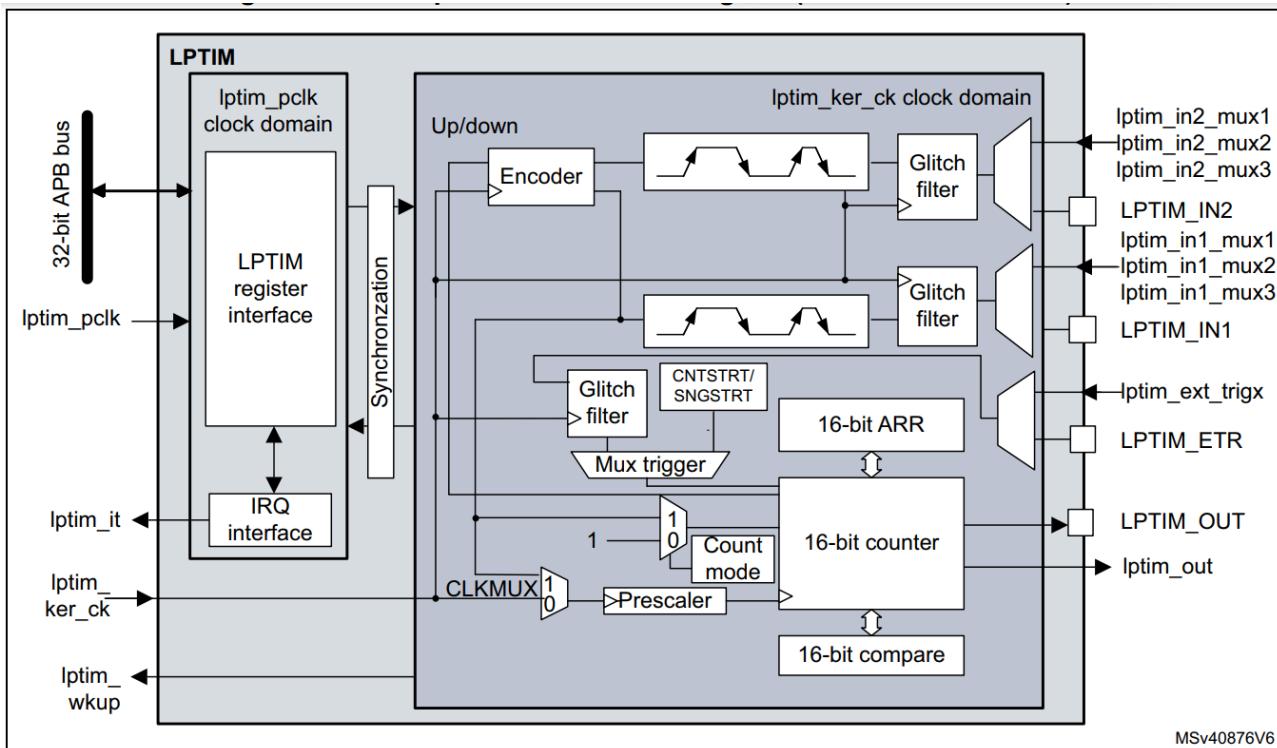

Imagine um sistema de controle de acesso por cartão. Ao inserir o cartão, o leitor gera um pulso único que aciona a abertura da catraca por um curto período, permitindo a passagem do usuário. Neste caso, o pulso único com uma duração exata desejada garante que a catraca seja aberta apenas uma vez por cartão, evitando que pessoas não autorizadas passem pela catraca. Já pensou como gerar um pulso único, controlando com precisão o momento exato de duas interrupções consecutivas em um temporizador de interrupções periódicas que vimos nos dois projetos anteriores? O desafio é criar um pulso com nível oposto ao do sinal original durante o restante do tempo. Parece complicado? Pois é! Mas com o temporizador de baixo consumo (em inglês, *Low*

*Power Timer - LPTIM*) do microcontrolador STM32H7A3, essa tarefa se torna muito mais fácil! Vamos descobrir juntos como isso pode ser feito passo-a-passo?

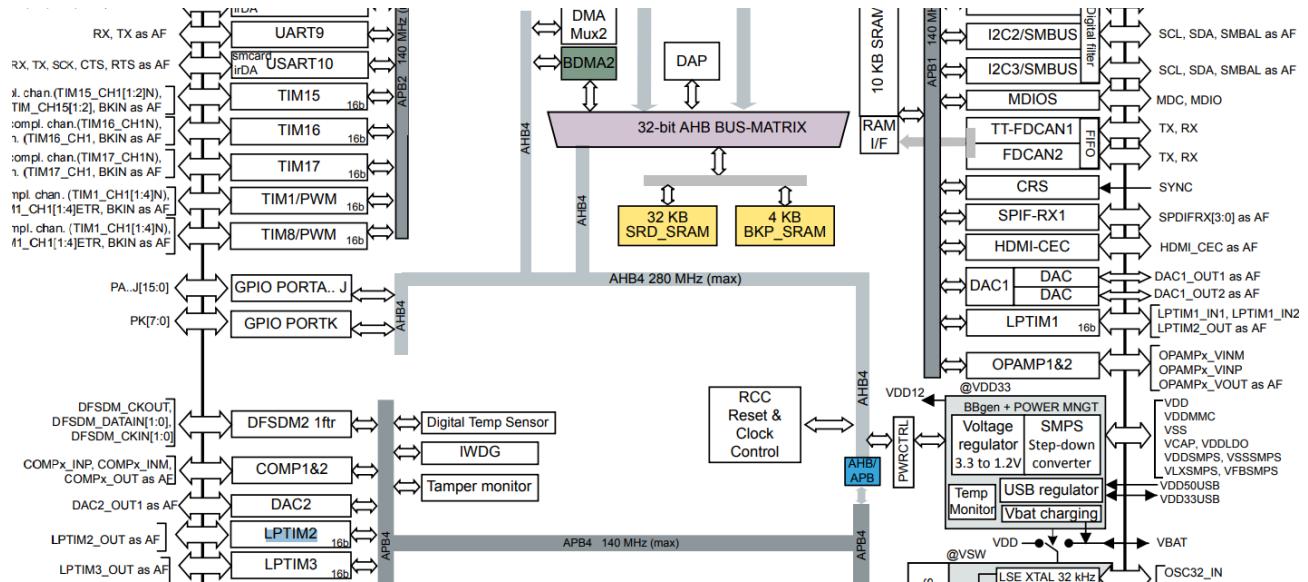

1. Crie o projeto “OneShot\_Bare\_CMSIS”, seguindo o mesmo procedimento utilizado nos projetos anteriores. Por padrão, o sinal de relógio do barramento APB4, onde os temporizadores LPTIM2 e LPTIM3 estão conectados, é de 64MHz após o *reset* com a seleção do HSI como fonte de clock.

2. Vamos definir a macro `pulse_length` e configurar o pino PB13 como saída para a forma de onda de pulso único gerada pelo LPTIM2, utilizando sua funcionalidade de saída de função especial/alternativa, em vez de um GPIO, no início da função “main”:

```

#define pulse_length 1000

int main(void)

{

// Ativar o clock do GPIOB

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN;

// Configurar PB13 como saída alternativa (AF3 para LPTIM2_OUT)

GPIOB->MODER &= ~(GPIO_MODER_MODE13_Msk);

GPIOB->MODER |= GPIO_MODER_MODE13_1; // Alternate function mode

GPIOB->AFR[1] &= ~(GPIO_AFRH_AFSEL13_Msk); // AF3 para PB13

GPIOB->AFR[1] |= (3 << GPIO_AFRH_AFSEL13_Pos);

}

```

3. Ativamos o sinal de relógio que alimenta LPTIM2 com RCC\_APB4ENR, adicionando a seguinte instrução:

```

RCC->APB4ENR |= RCC_APB4ENR_LPTIM2EN_Msk;

```

4. Antes de modificar qualquer registrador do LPTIM2, o *reset* do periférico deve ser feito através do registrador RCC\_APB4RSTR antes de ativá-lo, garantindo um estado inicial limpo. Adiciona-se as seguintes instruções:

```

RCC->APB4RSTR |= RCC_APB4RSTR_LPTIM2RST_Msk;

RCC->APB4RSTR &= ~RCC_APB4RSTR_LPTIM2RST_Msk;

```

5. Para configurar o registrador LPTIM\_CFGR, é necessário que LPTIM2 esteja desabilitado em LPTIM\_CR

```

LPTIM2->CR &= ~LPTIM_CR_ENABLE_Msk;

```

6. Selecione, em seguida, o *clock* interno como a base de tempo de LPTIM2

```

LPTIM2->CFG &= ~LPTIM_CFGR_CKSEL_Msk;

LPTIM2->CFG &= ~LPTIM_CFGR_COUNTMODE_Msk; // CNT incrementa com clock interno

```

7. Configure o divisor de frequência do *clock* interno de 64MHz em 32.

```

LPTIM2->CFG &= ~LPTIM_CFGR_PRESC_Msk;

LPTIM2->CFG |= (0x5UL << LPTIM_CFGR_PRESC_Pos);

```

8. Configure a fonte de disparo do pulso único ser por *software* a seguir.

```

LPTIM2->CFG_R &= ~LPTIM_CFGR_TRIGEN_Msk;

```

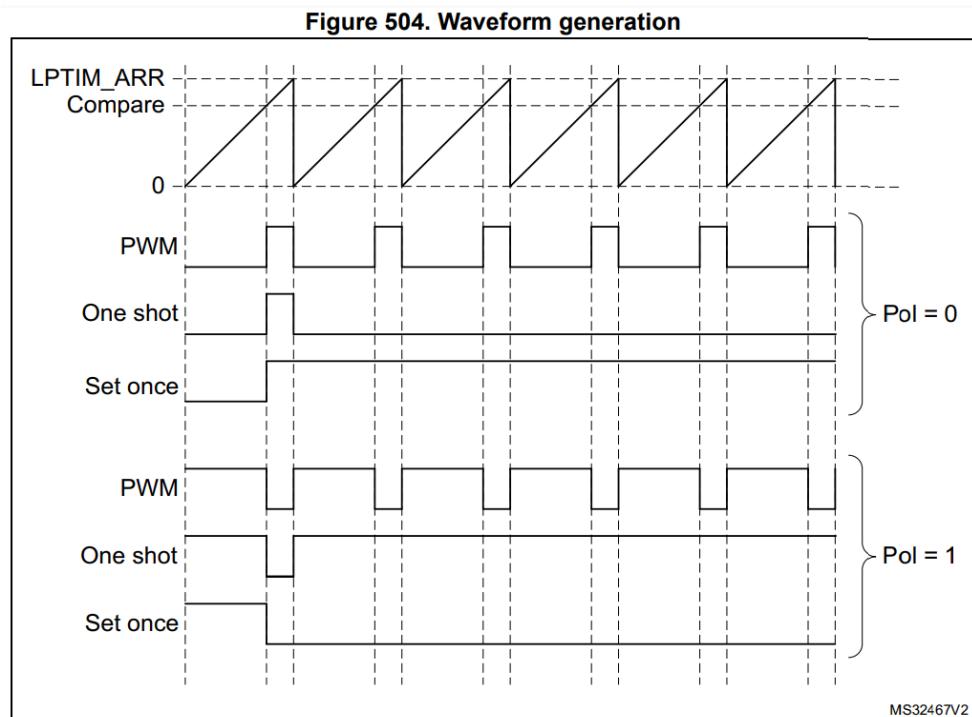

9. Configure a forma de onda ser do modo “pulso único” e o nível lógico deste pulso é “1” se o valor do contador LPTIM\_CNT for maior que LPTIM\_CMP, acrescentando

```

LPTIM2->CFG_R &= ~LPTIM_CFGR_WAVPOL_Msk; // Use nivel logico da comparacao

LPTIM2->CFG_R &= ~LPTIM_CFGR_WAVE_Msk;

```

10. Habilite LPTIM2 com LPTIM\_CR para configurar o restante dos registradores com

```

LPTIM2->CR |= LPTIM_CR_ENABLE;

```

11. Configure o valor do registrador LPTIM\_CMP para determinar o momento exato em que o pulso único terá início. Quando o contador LPTIM\_CNT atingir este valor, inicia-se o pulso único.

```

LPTIM2->CMP = pulse_length / 2;

```

12. Configure o valor do registrador LPTIM\_ARR para determinar o momento exato em que o pulso termina. Quando o contador chegar nesse valor, o valor do contador é resetado em zero e o valor do contador volta a ser menor do que o valor setado em LPTIM\_CMP.

```

LPTIM2->ARR = pulse_length*2; // Período (tamanho do pulso)

```

13. Por fim, configure o modo de operação one-shot para LPTIM2.

```

LPTIM2->CR |= LPTIM_CR_SNGSTRT;

```

14. Segue-se o código completo do arquivo “main.c”:

```

#include <stdint.h>

#include <stm32h7a3xxq.h>

#define pulse_length 1000

int main(void)

{

// Por padrao, frequencia do sinal de relogio eh 64MHz

// Ativar o clock do GPIOB

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN;

// Configurar PB13 como saida alternativa (AF3 para LPTIM2_OUT - Datasheet pg. 69)

GPIOB->MODER &= ~(GPIO_MODER_MODE13_Msk);

GPIOB->MODER |= GPIO_MODER_MODE13_1; // Alternate function mode

GPIOB->AFR[1] &= ~(GPIO_AFRH_AFSEL13_Msk); // AF3 para PB13 (pg. 521)

GPIOB->AFR[1] |= (3 << GPIO_AFRH_AFSEL13_Pos); // AF3 para PB13 (pg. 521)

// Habilitar o clock do LPTIM2 (pg. 457)

RCC->APB4ENR |= RCC_APB4ENR_LPTIM2EN_Msk;

// Resetar LPTIM2 para configuracao inicial (pg. 434)

RCC->APB4RSTR |= RCC_APB4RSTR_LPTIM2RST_Msk;

RCC->APB4RSTR &= ~RCC_APB4RSTR_LPTIM2RST_Msk; // default depois de Reset

// Garantir que o LPTIM2 esta desativado antes de configurar LPTIM_CFGR, pg. 1781

LPTIM2->CR &= ~LPTIM_CR_ENABLE_Msk;

// Habilitar o clock interno do LPTIM2

LPTIM2->CFG_R &= ~LPTIM_CFGR_CKSEL_Msk;

// Selecionar o prescaler (divisor=32 - pg. 1766)

LPTIM2->CFG_R &= ~LPTIM_CFGR_PRESC_Msk;

```

```

LPTIM2->CFG_R |= (0x5UL << LPTIM_CFGR_PRESC_Pos);

// Configurar a fonte de trigger (pg. 1766)

// Manual: "The LPTIM counter is started as soon as one of the

// CNTSTRT or the SNGSTRT bits is set by software."

LPTIM2->CFG_R &= ~LPTIM_CFGR_TRIGEN_Msk; // Trigger por software

// Configurar a forma de onda de saida (pg. 1770)

LPTIM2->CFG_R &= ~LPTIM_CFGR_WAVPOL_Msk; // Use nivel logico da comparacao

LPTIM2->CFG_R &= ~LPTIM_CFGR_WAVE_Msk; // Desativa "Set-once"

// Habilitar o LPTIM2

LPTIM2->CR |= LPTIM_CR_ENABLE;

// Definir periodo e comprimento do pulso (somente com LPTIM habilitado, pag 1783)

LPTIM2->ARR = pulse_length*2; // Periodo (tamanho do pulso)

LPTIM2->CMP = pulse_length / 2; // Inicio do pulso

// Ativar o modo de contador: one-shot mode (pg. 1767)

LPTIM2->CR |= LPTIM_CR_SNGSTRT;

/* Loop forever */

for(;;);

}

```

15. Faça o “Build” e transfira, no modo “Debug”, o código executável de extensão .elf para o microcontrolador.

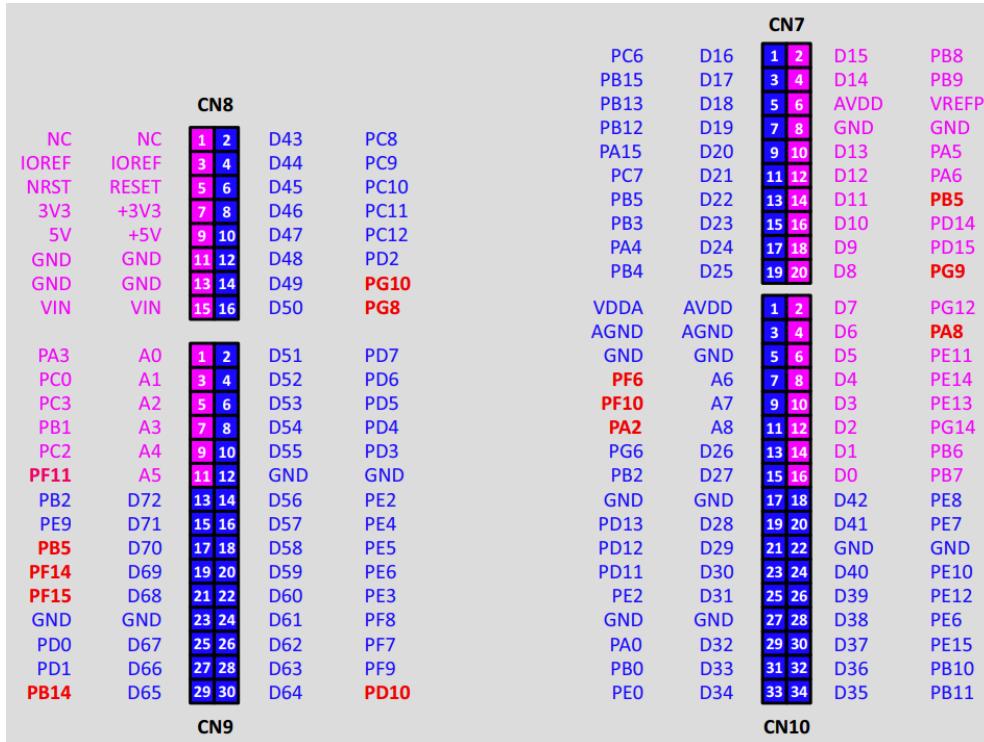

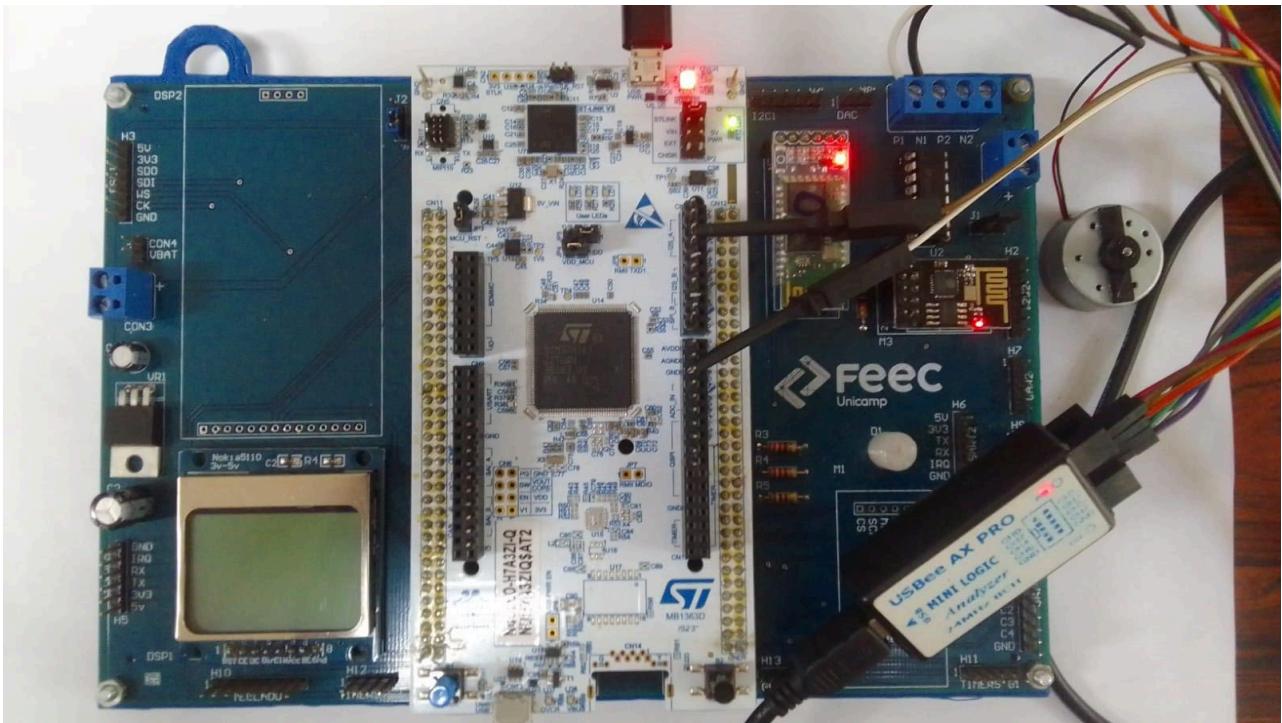

16. Conecte o Canal 0 do analisador lógico no pino PB13 da placa NUCLEO-144 e o seu terra num ponto GND da placa através dos conectores fêmeas Zio, CN7-5 e CN10-5, presentes na placa

A seguinte imagem ilustra uma forma de conexão.

17. Conecte o analisador a uma porta USB do *desktop* e abra o [aplicativo Logic 2.4.x](#). Assim que o aplicativo reconhecer a conexão, uma janela será exibida, permitindo que você visualize o sinal nos pinos através dos canais correspondentes aos pinos conectados. Os detalhes de operação do analisador lógico podem ser verificados no [vídeo](#). Utilize o maior valor de amostras por segundo que for possível e configure a aquisição para cerca de 10ms.

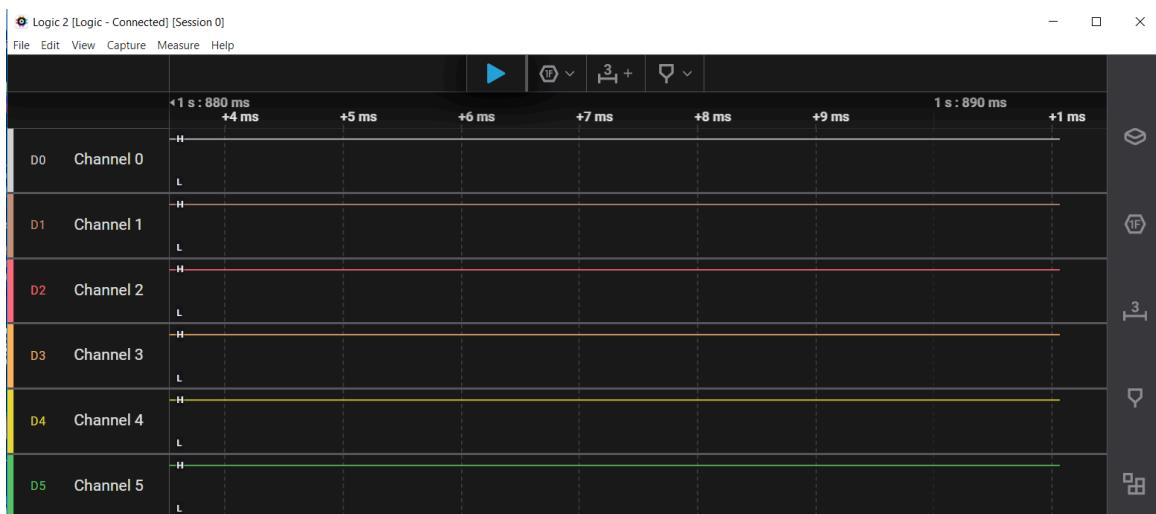

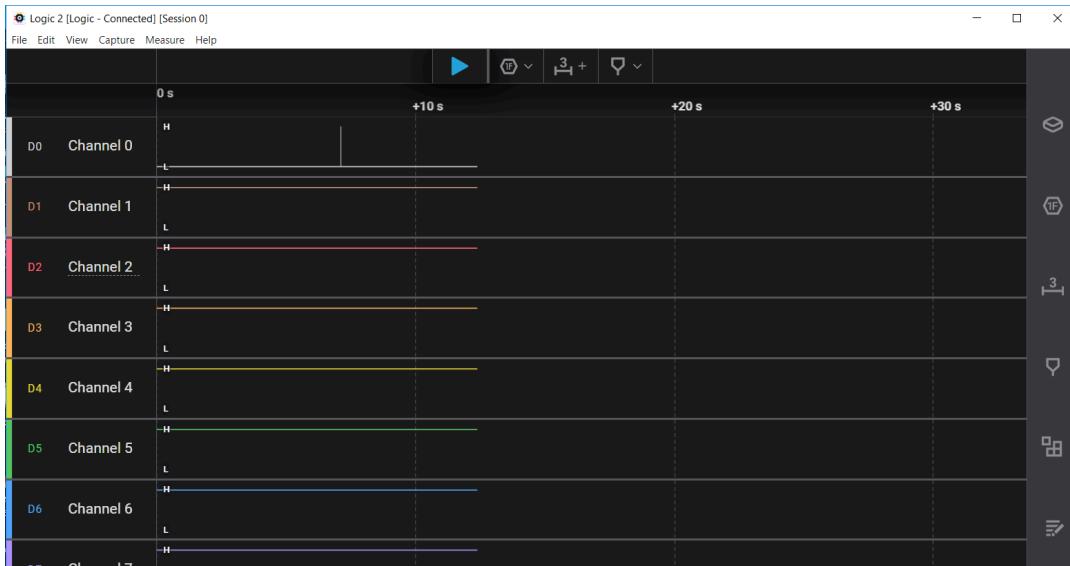

18. Coloque um *breakpoint* na seguinte linha de instrução e inicie a execução (“Resume”).

```

LPTIM2->CFGGR &= ~LPTIM_CFGGR_WAVE_Msk; // Desativa "Set-once"

```

19. Ao parar na linha de instrução, aumente a escala de tempo para dezenas de segundos e inicialize a captura do analisador clicando em cima do triângulo azul (“Start”) na barra de ferramenta superior. Retome (“Resume”) a execução do programa e monitore a forma de onda. Assim que aparecer um pulso, páre o analisador clicando em cima do quadrado azul (“Stop”).

20. Reduza a escala de tempo para microsegundos até que seja visível a largura do pulso único gerado. Meça a largura e verifique se é condizente com as configurações feitas nos registradores do temporizador LPTIM2.

21. Como podemos modificar o programa para gerar um pulso negativo (nível lógico baixo)? Não se preocupe se a resposta não estiver clara agora. Exploraremos as configurações em detalhes mais adiante.

22. Qual alteração no código transformará um pulso único em um degrau? Se a resposta ainda não surgiu, não se preocupe! Continue a leitura com atenção, pois a solução será explicada.

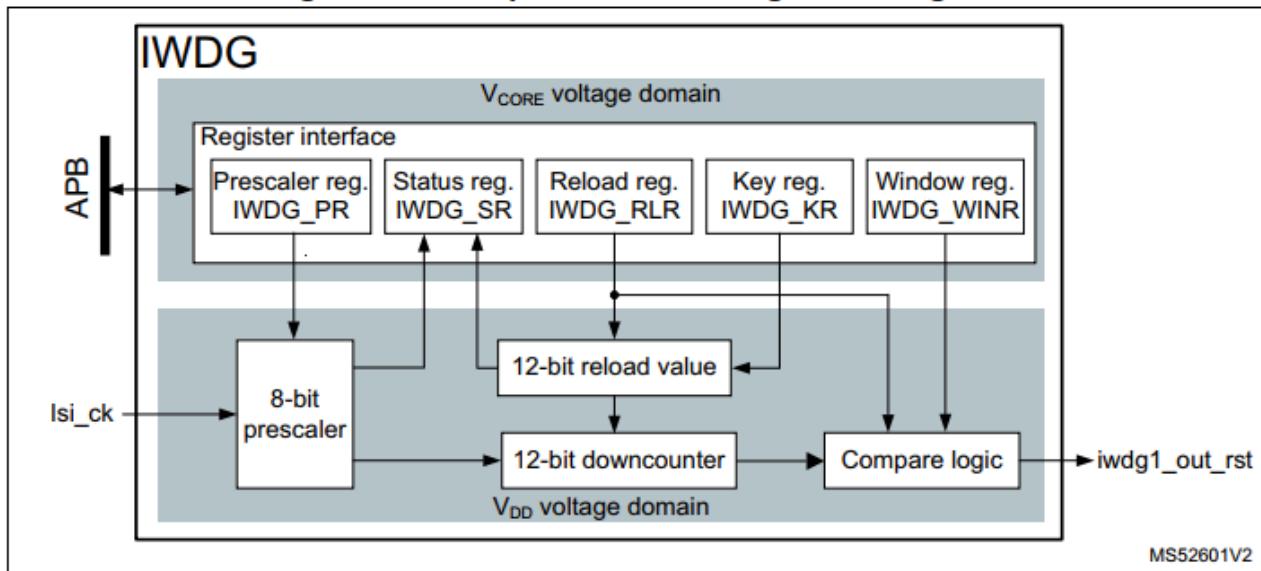

## Projeto com o *Watchdog* usando STM32CubeMX e CMSIS

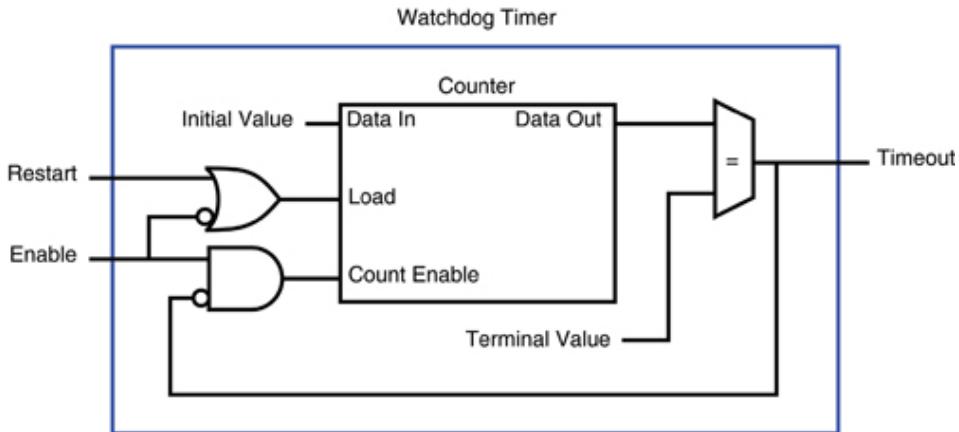

Imagine um carro com freios inteligentes: o microcontrolador recebe seus comandos e ajusta a pressão dos freios, garantindo uma frenagem precisa e segura. Mas e se o *software* desse microcontrolador travar? O resultado seria catastrófico: falha nos freios e um acidente! Em sistemas críticos como esse, detectar falhas não é suficiente. É preciso agir rápido, garantir que o sistema volte a funcionar antes que o problema se torne real. Desenvolver um sistema que detecta automaticamente falhas e se recupera sem intervenção humana parece coisa de ficção alguns anos atrás, certo? Mas essa tecnologia existe e está ao seu alcance! Uma estratégia usada em sistemas embarcados é o temporizador de vigilância (em inglês, *watchdog timer*), um verdadeiro cão de guarda digital. Esse temporizador monitora o sistema sem parar e, se algo der errado, ele age rápido: espera um pouco para ter certeza da falha e, se o problema persistir, reinicia o sistema. Com a tecnologia atual, muitos microcontroladores, como o STM32H7A3, já vêm com esse temporizador integrado, simplificando (e muito!) essa tarefa.

Vamos ilustrar a configuração de um *watchdog* do microcontrolador STM32H73A para criar um projeto onde você terá o controle da segurança do sistema! Considerando que o evento de “pressionamento do botão azul” seja “evidência da normalidade na operação”, o *watchdog* será alimentado (em inglês, *feed*) pelo evento de pressionamento e o LED amarelo se acenderá para confirmar que o botão foi pressionado. Se o botão azul não for pressionado em intervalos menores que 5 segundos, o *watchdog* entenderá que houve uma falha e reiniciará o sistema. Após a reinicialização, o LED verde permanecerá apagado por um tempo, indicando que o sistema foi reiniciado. Em seguida, o sistema voltará ao seu estado normal de monitoramento.

Vamos aprender, passo-a-passo, como configurar o *watchdog* independente, IWDG, do STM32H7A3 para realizar essa tarefa? O IWDG é um temporizador independente, com seu próprio oscilador interno (LSI), de forma que ele opera mesmo se o *clock* principal do sistema falhar. No universo dos microcontroladores STM32, ajustar os sinais de relógio independentes para o módulo IWDG pode parecer um desafio e está fora do escopo desta disciplina. Mas não se preocupe! O STM32CubeIDE, com seu editor gráfico intuitivo STM32CubeMX, torna essa tarefa muito mais simples. Com ele, você pode visualizar e ajustar cada detalhe do sistema de sinais de relógio, desde a frequência do núcleo até a velocidade dos periféricos, tudo de forma interativa e acessível, e gerar códigos adequados.

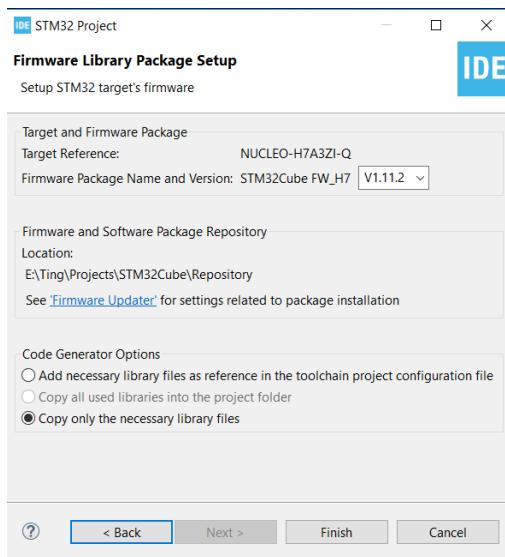

1. Crie um novo projeto da mesma forma que foi feito com os anteriores, exceto que na opção “*Targeted Project Type*” vamos manter o padrão “STM32Cube” para que o STM32CubeMX seja incluído. Dê o nome de “IWDG” a este projeto. Na sequência, se for clicado o botão “Next” abre-se uma janela para a configuração do pacote de biblioteca de *firmware*. Deixe as **opções padrão** e clique em *Finish*. Na janela anterior, pode-se clicar em “Finish” em vez de “Next” e omitir esta etapa.

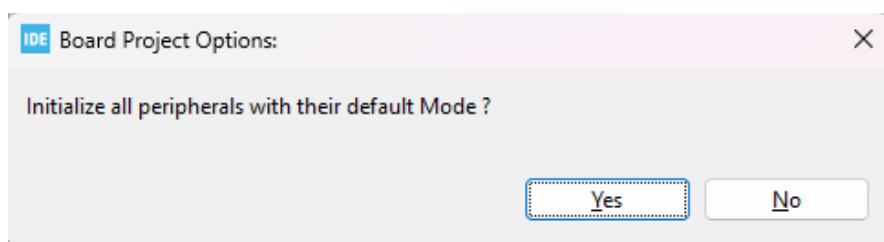

Como estamos trabalhando com uma placa que dispõe de alguns periféricos ligados ao microcontrolador, aparecerá uma janela perguntando se deseja iniciar os periféricos na configuração “default”. Clique em “No” para que o código gerado pelo STM32CubeIDE não inclua a inicialização dos periféricos da placa com os pinos desabilitados.

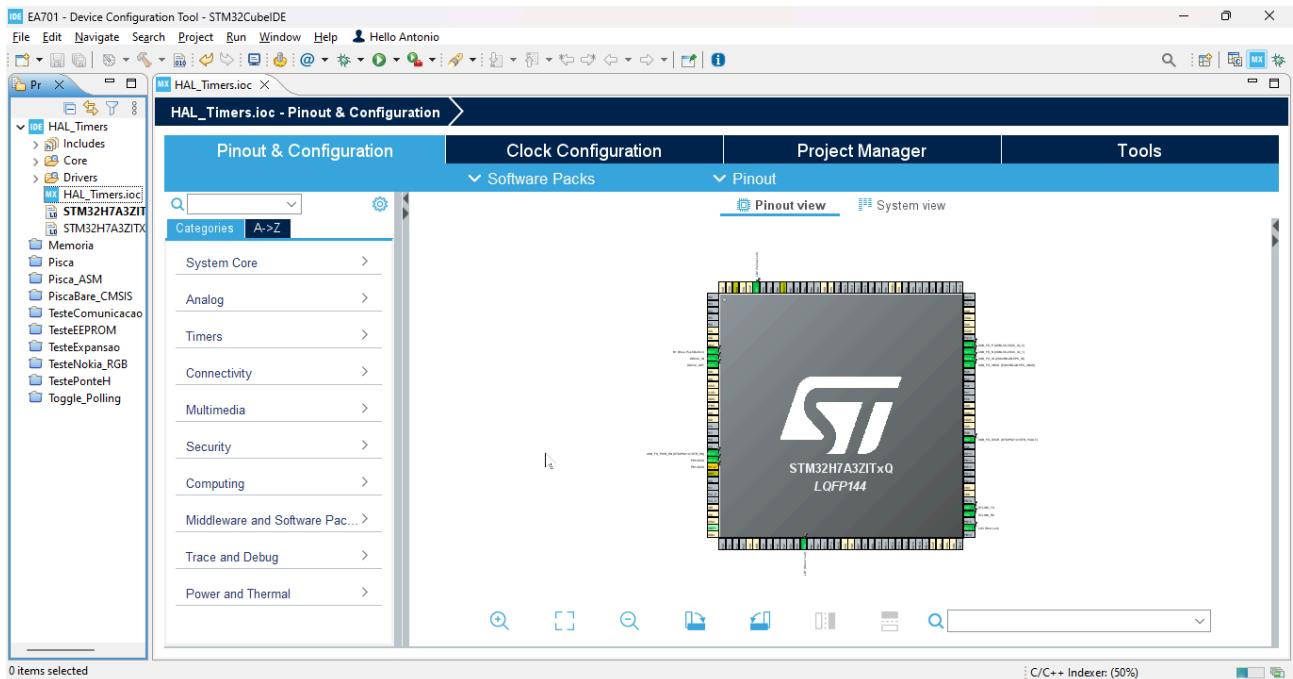

Após a instalação dos pacotes de suporte, o IDE entra na perspectiva de Inicialização, com o arquivo `IWDG.ioc` aberto no modo gráfico numa aba (este é o *plugin* STM32CubeMX do IDE). A

aba mostra graficamente numa janela todas as configurações de periféricos presentes em IWDG.ioc para que o módulo STM32CubeMX gere o código de inicialização dos mesmos. Dominando a tela, aparece uma representação física do microcontrolador, com controles de zoom intuitivos para aproximar e inspecionar cada detalhe, cada pino e cada conexão. À esquerda, há um painel com uma lista dos diversos periféricos do microcontrolador, bem como eventuais algoritmos de cálculo e recursos de *Middleware* (sistemas de arquivos, dispositivos USB, etc).

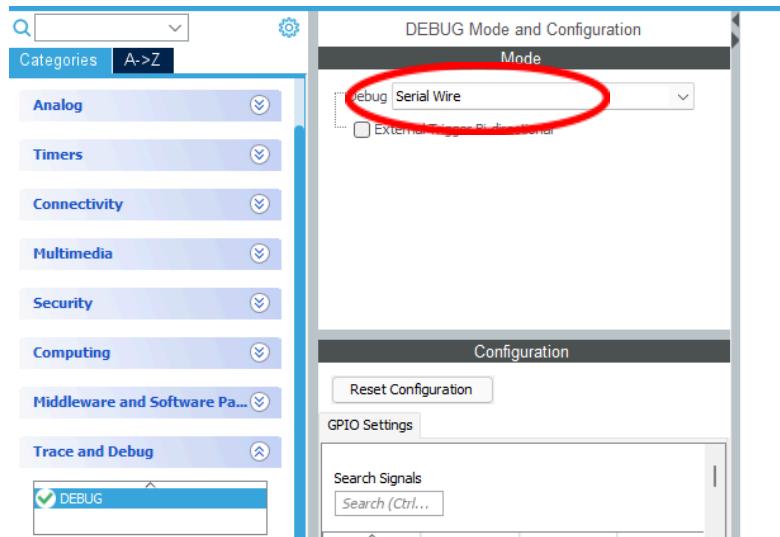

2. Dê um *zoom* na imagem do circuito integrado (clicar no ícone Maximize no canto direito superior) para que ele preencha a tela. Pode-se também clicar com o *mouse* sobre ele e arrastar para ajustar a posição. Vamos revisar os itens e configurar alguns deles. Clique sobre o item “*Trace and Debug*” e verá o item “*DEBUG*” abrir. Clique sobre o item e um novo painel irá abrir entre a lista e a representação física do controlador. Precisamos ativar o modo de depuração do microcontrolador, e para isso selecione “*Serial Wire*” na lista do item “*Debug*”.

Ao selecionar “*Serial Wire*”, o modo SWD de depuração, utilizado pelo depurador ST-LINK, é ativado. Observe como dois pinos (PA13 e PA14) na imagem “*Pinout view*” do microcontrolador agora aparecem em verde, com as funções selecionadas devidamente identificadas. Além disso, os dois pinos são automaticamente adicionados à lista de “*Configuration*”. Esta etapa é essencial se usarmos o *software* de alocação de pinos, pois estes pinos estão fisicamente conectados ao ST-LINK presente na placa NUCLEO-144. Ao ativá-los manualmente, garantimos que o IDE reconheça sua função de depuração e evite que sejam alocados para outras funções inadvertidamente no STM32CubeMX.

Vale ressaltar que, ao configurar os periféricos de um microcontrolador STM32 no STM32CubeMX, é fundamental observar a representação visual do circuito. Cada periférico ativado no *software* tem seus pinos correspondentes destacados em verde na tela, facilitando a configuração, a visualização e a depuração de projetos.

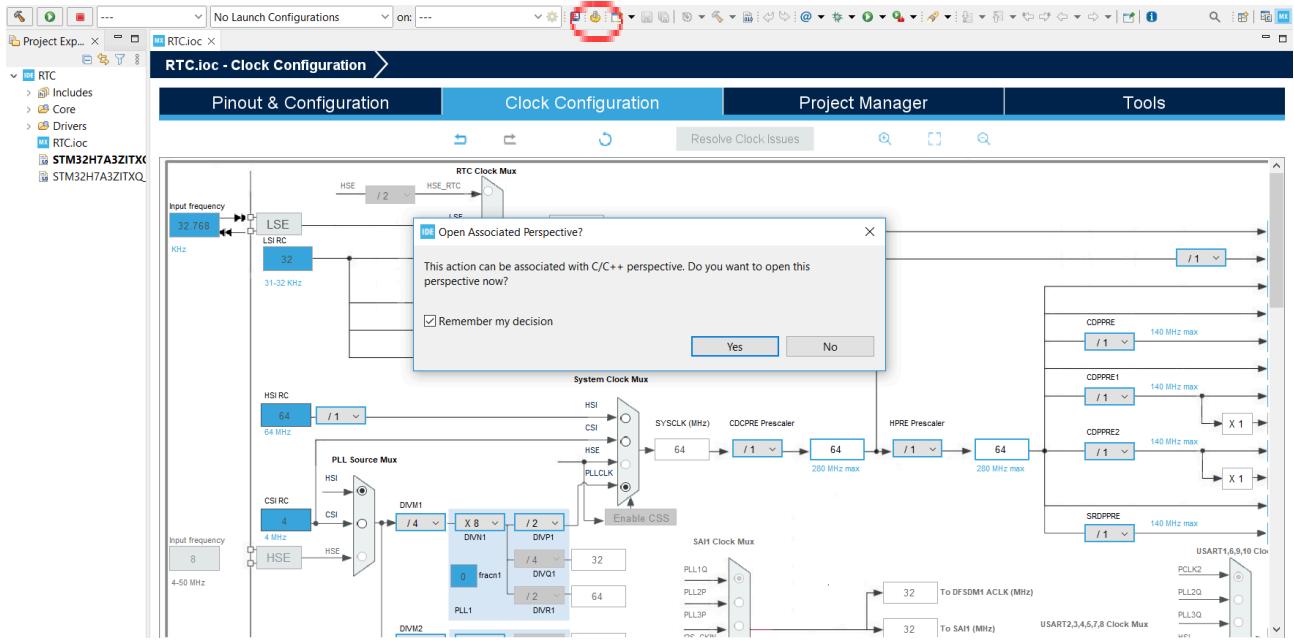

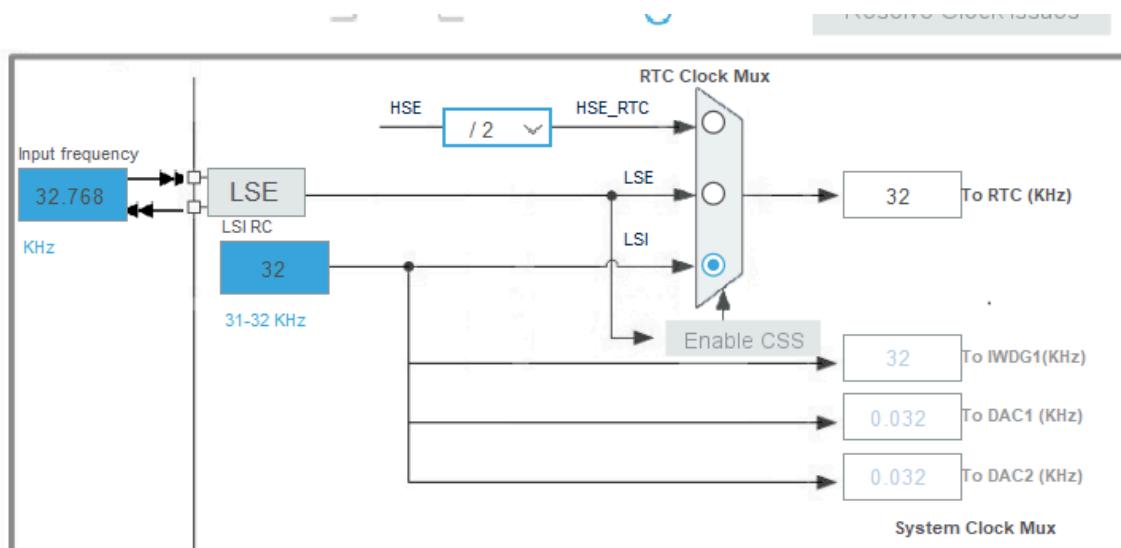

3. Clique na aba de “Clock Configuration” para ver a árvore de *clock*. Note que na parte superior há um bloco chamado “LSI RC”, com a caixa em azul e o valor 32 kHz dentro. Note que este é o oscilador interno (independente) usado pelo watchdog independente (IWDG) do STM32H7A3.

4. Salve o projeto e gere o código de inicialização em C clicando no ícone “Device Configuration Tool Code Generation”. Se for pela primeira vez, aparecerá uma janela *popup* perguntando se deve lembrar a decisão de chaveamento para a Perspectiva C/C++. Selecione “Yes” para que se abra a Perspectiva C/C++ assim que concluir a geração de códigos.

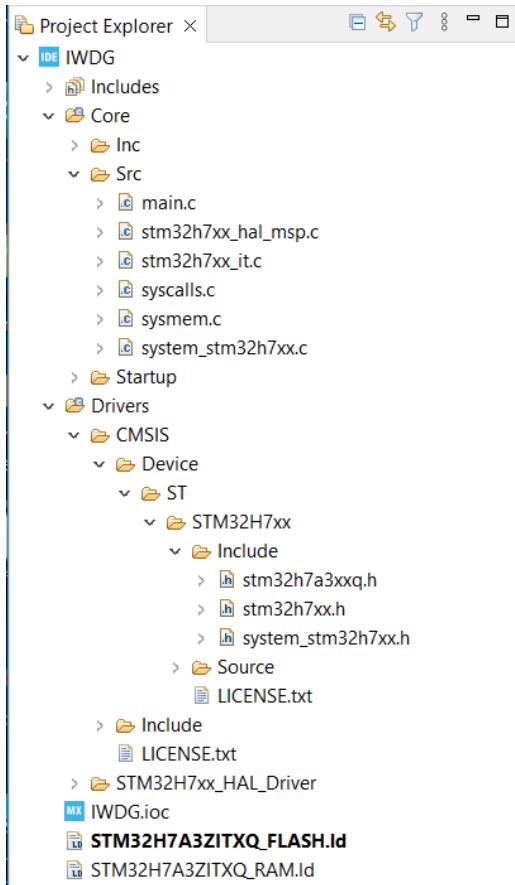

5. Os códigos gerados pelo STM32CubeMX apresentam uma estrutura diferente dos projetos que implementamos até agora. As principais diferenças são:

- Estrutura de pastas

- As pastas do desenvolvedor (`Inc` e `Src`) são movidas para dentro da pasta `Core`.

- Arquivos incluídos

- Os arquivos-cabeçalho que incluímos manualmente nos projetos anteriores agora estão integrados na pasta `Drivers/CMSIS/`.

- O arquivo `stm32h7xx_it.c` é adicionado à pasta `Src` para armazenar as rotinas de tratamento de interrupções separadamente.

- Conteúdo do arquivo `main.c`

- O arquivo `main.c` possui uma nova estrutura, dividida em segmentos pelos comentários `/* USER CODE BEGIN XXX */` e `/* USER CODE END XXX */`, onde `XXX` especifica o tipo de dado a ser inserido.

- Os dados inseridos entre esses comentários são preservados quando os códigos são regenerados após alterações na configuração.

Aprenderemos como utilizar cada segmento presente no `main.c` sob demanda.

Para entender como os módulos realmente funcionam, vamos criar nossas próprias funções em vez de usarmos as funções de inicialização dos módulos geradas automaticamente pelo STM32CubeMX no arquivo `main.c`. Essa prática nos permitirá aprofundar nosso conhecimento sobre o funcionamento desses módulos e ter uma compreensão muito mais clara de como o código é executado. Por isso, antes de adicionarmos os nossos códigos, vamos remover algumas linhas de instruções geradas. Em vez de simplesmente remover as linhas de instrução do código gerado, elas foram apenas comentadas (selecione a região a ser removida e aperte simultaneamente as teclas ‘CTRL’ e ‘/’). Essa abordagem permite que visualizemos claramente o que foi descartado, facilitando a compreensão das alterações feitas e fornecendo um histórico do código original. Além disso, caso seja necessário reverter alguma alteração, basta descomentar as linhas desejadas, tornando o processo mais rápido e eficiente.

(a) protótipos das funções

```

/* Private function prototypes -----*/

void SystemClock_Config(void);

//static void MX_GPIO_Init(void);

```

(b) chamadas das funções

```

/* Initialize all configured peripherals */

// MX_GPIO_Init();

```

(c) definição das funções

```

/***

// * @brief GPIO Initialization Function

// * @param None

// * @retval None

```

```

// */

//static void MX_GPIO_Init(void)

//{

//  GPIO_InitTypeDef GPIO_InitStruct = {0};

//  /* USER CODE BEGIN MX_GPIO_Init_1 */

//  /* USER CODE END MX_GPIO_Init_1 */

//

//  /* GPIO Ports Clock Enable */

//  __HAL_RCC_GPIOC_CLK_ENABLE();

//  __HAL_RCC_GPIOF_CLK_ENABLE();

//  __HAL_RCC_GPIOH_CLK_ENABLE();

//  __HAL_RCC_GPIOB_CLK_ENABLE();

//  __HAL_RCC_GPIOD_CLK_ENABLE();

//  __HAL_RCC_GPIOG_CLK_ENABLE();

//  __HAL_RCC_GPIOA_CLK_ENABLE();

//  __HAL_RCC_GPIOE_CLK_ENABLE();

//

//  /*Configure GPIO pin Output Level */

//  HAL_GPIO_WritePin(USB_FS_PWR_EN_GPIO_Port, USB_FS_PWR_EN_Pin, GPIO_PIN_RESET);

//

//  /*Configure GPIO pin Output Level */

//  HAL_GPIO_WritePin(GPIOB, LD1_Pin|LD3_Pin, GPIO_PIN_RESET);

//

//  /*Configure GPIO pin Output Level */

//  HAL_GPIO_WritePin(LD2_GPIO_Port, LD2_Pin, GPIO_PIN_RESET);

//

//  /*Configure GPIO pin : B1_Pin */

//  GPIO_InitStruct.Pin = B1_Pin;

//  GPIO_InitStruct.Mode = GPIO_MODE_INPUT;

//  GPIO_InitStruct.Pull = GPIO_NOPULL;

//  HAL_GPIO_Init(B1_GPIO_Port, &GPIO_InitStruct);

//

//  /*Configure GPIO pin : USB_FS_PWR_EN_Pin */

//  GPIO_InitStruct.Pin = USB_FS_PWR_EN_Pin;

//  GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;

//  GPIO_InitStruct.Pull = GPIO_NOPULL;

//  GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

//  HAL_GPIO_Init(USB_FS_PWR_EN_GPIO_Port, &GPIO_InitStruct);

//

//  /*Configure GPIO pins : LD1_Pin LD3_Pin */

//  GPIO_InitStruct.Pin = LD1_Pin|LD3_Pin;

//  GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;

//  GPIO_InitStruct.Pull = GPIO_NOPULL;

//  GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

//  HAL_GPIO_Init(GPIOB, &GPIO_InitStruct);

//

//  /*Configure GPIO pins : STLINK_RX_Pin STLINK_TX_Pin */

//  GPIO_InitStruct.Pin = STLINK_RX_Pin|STLINK_TX_Pin;

//  GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

//  GPIO_InitStruct.Pull = GPIO_NOPULL;

//  GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

//  GPIO_InitStruct.Alternate = GPIO_AF7_USART3;

//  HAL_GPIO_Init(GPIOD, &GPIO_InitStruct);

//

//  /*Configure GPIO pin : USB_FS_OVCR_Pin */

//  GPIO_InitStruct.Pin = USB_FS_OVCR_Pin;

//  GPIO_InitStruct.Mode = GPIO_MODE_IT_RISING;

//  GPIO_InitStruct.Pull = GPIO_NOPULL;

//  HAL_GPIO_Init(USB_FS_OVCR_GPIO_Port, &GPIO_InitStruct);

//

//  /*Configure GPIO pin : USB_FS_ID_Pin */

//  GPIO_InitStruct.Pin = USB_FS_ID_Pin;

//  GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

//  GPIO_InitStruct.Pull = GPIO_NOPULL;

//  GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

//  GPIO_InitStruct.Alternate = GPIO_AF10_OTG1_HS;

//  HAL_GPIO_Init(USB_FS_ID_GPIO_Port, &GPIO_InitStruct);

```

```

//

// /*Configure GPIO pins : USB_FS_N_Pin USB_FS_P_Pin */

// GPIO_InitStruct.Pin = USB_FS_N_Pin|USB_FS_P_Pin;

// GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

// GPIO_InitStruct.Pull = GPIO_NOPULL;

// GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

// HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);

//

// /*Configure GPIO pin : LD2_Pin */

// GPIO_InitStruct.Pin = LD2_Pin;

// GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;

// GPIO_InitStruct.Pull = GPIO_NOPULL;

// GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

// HAL_GPIO_Init(LD2_GPIO_Port, &GPIO_InitStruct);

//

// /*** USER CODE BEGIN MX_GPIO_Init_2 ***/

// /*** USER CODE END MX_GPIO_Init_2 ***/

//}

```

6. Vamos incluir os protótipos das funções que definiremos depois da linha `/* USER CODE BEGIN PFP */`

```

void delay(void);

void GPIO_Config(void);

void IWDG_Config(void);

```

7. Vamos agora adicionar a definição da função `IWDG_Config` segundo o [procedimento](#) recomendado no Manual de Referência logo abaixo da linha `/* USER CODE BEGIN 4 */`

```

void IWDG_Config(void) {

// Habilita o IWDG e configura timeout de 5s

IWDG1->KR = 0xCCCC; // Habilita o IWDG

IWDG1->KR = 0x5555; // Desbloqueia acesso aos registradores

IWDG1->PR = 0b100; // Prescaler 64 (LSI típico ~32kHz)

IWDG1->RLR = 2500; // Timeout de ~5s: (64 * 25000) / 32000 = ~5s

while (IWDG1->SR & (IWDG_SR_PVU_Msk || IWDG_SR_RVU_Msk ||

IWDG_SR_WVU_Msk)); // aguardar a conclusão

IWDG1->KR = 0xAAAA; // Alimenta o watchdog

}

```

Habilita-se o módulo escrevendo 0xCCCC no registrador de chaves `IWDG_KR`. Em seguida, escreve-se 0x5555 para desbloquear acesso aos registradores de IWDG. Com um sinal de relógio na frequência de 32kHz, configuramos o divisor de frequência em 64 pelo registrador `IWDG_PR` e o valor de recarga em 2500 pelo registrador `IWDG_RLR`. Assim, teremos os 32kHz divididos por 64, resultando em 500Hz a frequência do *clock* do contador de IWDG, e o período de recargas em  $25000/500=5s$ . Aguarda-se até que sejam concluídas as configurações monitorando os estados no registrador `IWDG_SR`. Para iniciar o monitoramento, realizamos a primeira recarga do contador escrevendo o valor hexadecimal 0xAAAA no registrador `IWDG_KR`. Essa ação “alimenta” o *watchdog*, iniciando a contagem regressiva.

8. Em seguida, incluímos a definição da função `GPIO_Config` para habilitar os pinos que controlam os LEDs amarelo e verde e o botão azul.

```

void GPIO_Config(void) {

// Habilita clock dos GPIOs B e E

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN |

```

```

RCC_AHB4ENR_GPIOCEN |

RCC_AHB4ENR_GPIOEEN;

// Configura PB0 (LED verde) como saída

GPIOB->MODER &= ~(GPIO_MODER_MODE0_Msk);

GPIOB->MODER |= GPIO_MODER_MODE0_0;

GPIOB->OTYPER &= ~GPIO_OTYPER_OT0_Msk; // PB0 como push-pull

// Configura PE1 (LED amarelo) como saída

GPIOE->MODER &= ~(GPIO_MODER_MODE1_Msk);

GPIOE->MODER |= GPIO_MODER_MODE1_0;

GPIOE->OTYPER &= ~GPIO_OTYPER_OT1_Msk; // PB0 como push-pull

// Configura PB13 (botão azul) como entrada (pull-down)

GPIOC->MODER &= ~(GPIO_MODER_MODE13_Msk); // Entrada Digital

}

```

9. Adicionamos também a definição da função `delay` cujo tempo de atraso foi obtido empiricamente.

```

void delay() {

uint32_t count = 50000000;

while (count--);

}

```

10. Vamos atualizar a função `main` para que realize a tarefa. Em primeiro lugar, insira as chamadas das seguintes funções de inicialização dos módulos GPIO e IWDG

```

/* Initialize all configured peripherals */

// MX_GPIO_Init();

GPIO_Config();

IWDG_Config();

```

Depois da linha `/* USER CODE BEGIN 2 */`, adicione as seguintes instruções para que após um *reset*, o programa mantém o LED verde apagado por um tempo antes de acendê-lo

```

delay();

GPIOB->BSRR = (1U << 0); // Acende LED verde

```

No laço de espera `while`, insira o seguinte bloco de instruções depois da linha `/* USER CODE BEGIN 3 */`

```

// Se botão azul for pressionado

if (GPIOC->IDR & (1U << 13)) {

GPIOE->BSRR = (1U << 1); // Acende LED amarelo

IWDG1->KR = 0xAAAA; // Alimenta o watchdog

} else {

GPIOE->BSRR = (1U << (1 + 16)); // Apaga LED amarelo

}

```

O código “alimenta” o *watchdog* quando o botão azul é acionado, escrevendo 0xAAAA no registrador IWDG\_KR. Ao mesmo tempo, o LED amarelo é aceso. Se o botão azul não for acionado, o LED amarelo será apagado. Se o botão não for apertado por um intervalo maior que 5s, o *watchdog* irá reiniciar o programa, apagando o LED e esperando um intervalo de tempo perceptível para acendê-lo.

11. Realize o “Build” e transfira o código executável no modo “Debug” para o microcontrolador. Execute (“Resume”) o programa. Após o LED verde acender, aperte o botão em intervalos menores

que 2s. Após 5s sem pressionar o botão, o LED se apagará e o programa será reiniciado. O LED verde permanecerá apagado até ser explicitamente aceso por uma instrução do programa, evidenciando que o sistema foi reiniciado.

12. Uma característica importante do módulo IWDG é o registrador de chave IWDG\_KR. Ele exige que uma chave específica seja escrita para que os demais registradores do IWDG possam ser modificados. Essa medida de segurança aumenta um pouco a complexidade, mas traz benefícios importantes. Você consegue imaginar quais? Se não souber, não se preocupe, discutiremos a importância desse registrador mais adiante.

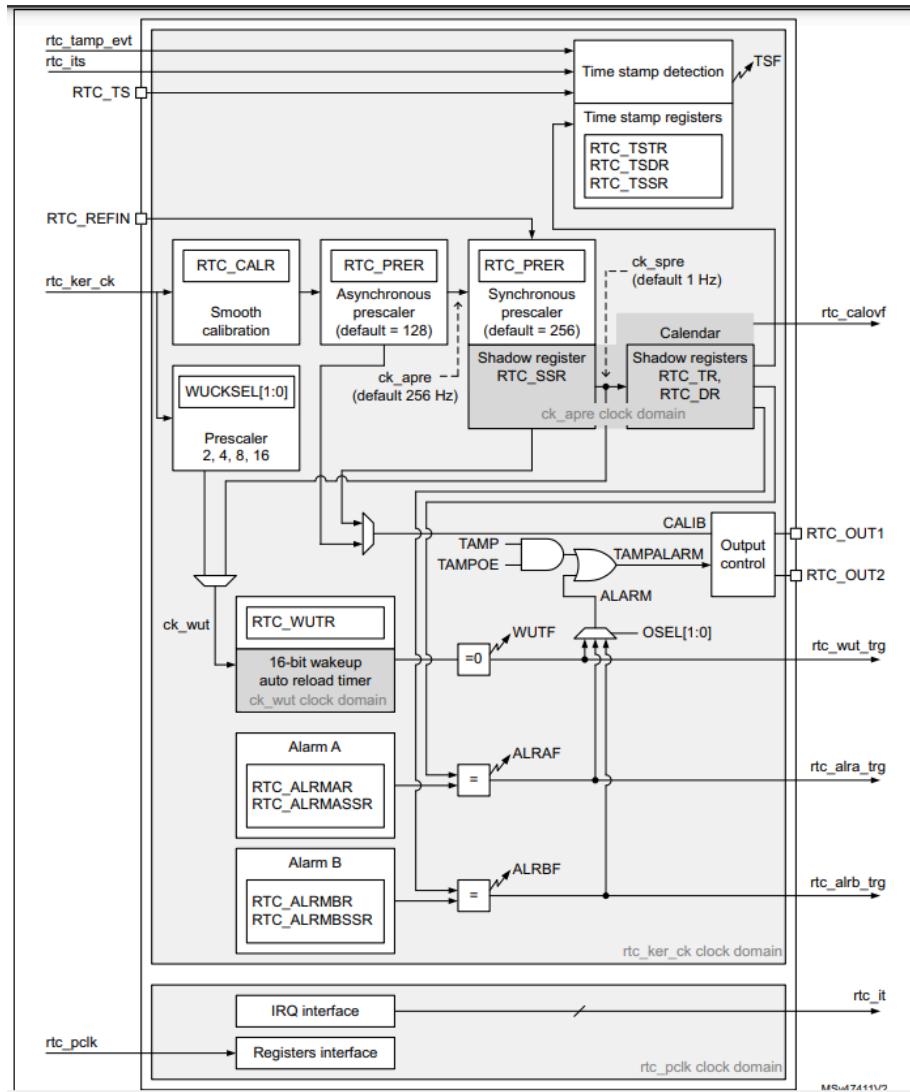

## Projeto com RTC usando STM32CubeMX e CMSIS

Agora vamos explorar o uso do RTC (do inglês *Real-Time Clock*) para controlar com precisão e confiabilidade a alternância do estado do LED amarelo da placa NUCLEO-144 a 1Hz. Além disso, configuramos o microcontrolador para que o LED verde seja acionado e alterne o seu estado em um horário específico todos os dias. Mas por que usar o RTC em vez dos temporizadores convencionais que já estudamos? A resposta está nas vantagens que ele oferece: maior precisão, compensação térmica, eficiência energética e facilidade na implementação de funções de relógio. Diferente dos temporizadores comuns, o RTC também conta com mecanismos de proteção contra alterações indevidas como temporizador *watchdog*, garantindo a integridade do sistema ao evitar modificações acidentais ou maliciosas. Outro grande diferencial do RTC do STM32H7A3 é sua fonte de clock independente como *watchdog*, permitindo que ele continue funcionando mesmo que o processador e outros periféricos parem. Isso o torna essencial para aplicações críticas, como sistemas de alarme confiáveis, que continuam operando sem falhas, relógios digitais de alta precisão, que mantêm a marcação do tempo sem interrupções, e dispositivos de coleta de dados, que garantem medições regulares mesmo durante quedas de energia.

Que tal verificarmos essas vantagens e a complexidade de programação adicional, implementando juntos o temporizador de **1 segundo** de alta precisão e um alarme que soa diariamente no horário 23:46:12, seguindo um passo-a-passo detalhado?

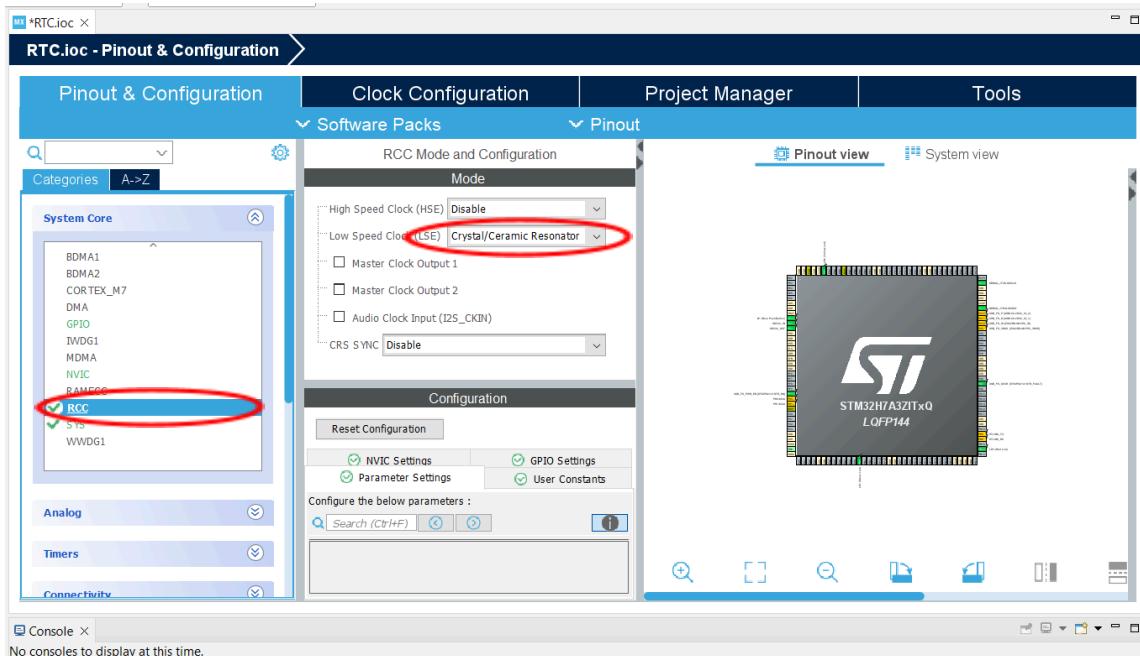

1. Crie o projeto “RTC” da mesma forma que foi feito com o projeto “IWDG”, selecionando “STM32Cube” na opção “*Targeted Project Type*” para incluir o plugin STM32CubeMX. Selecione ainda “Serial Wire” como o modo “DEBUG” no editor gráfico do arquivo RTC.ioc.

2. No mesmo edito, expanda o “*System Core*” no menu esquerdo, abra a configuração de “RCC” e selecione “Crystal/Ceramic Resonance” como a fonte do sinal de relógio LSE (do inglês, “*Low Speed Clock*”).

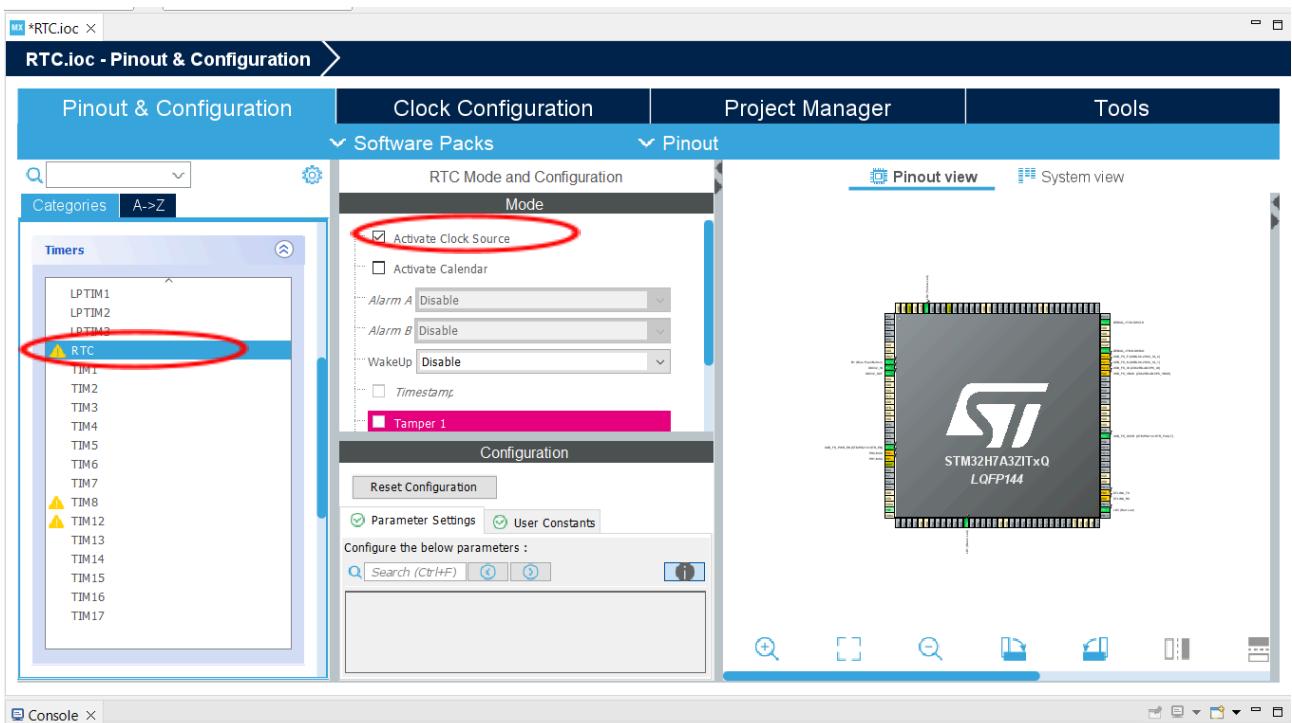

3. Expanda “Timers” no menu esquerdo, abra a configuração de “RTC” e ative a fonte de sinais de relógio para liberar a edição da fonte de sinais de relógio do RTC.

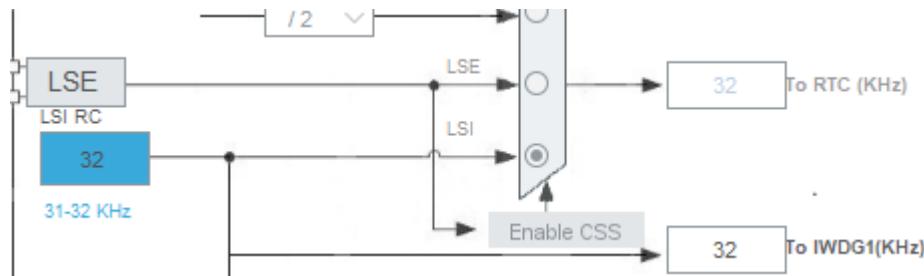

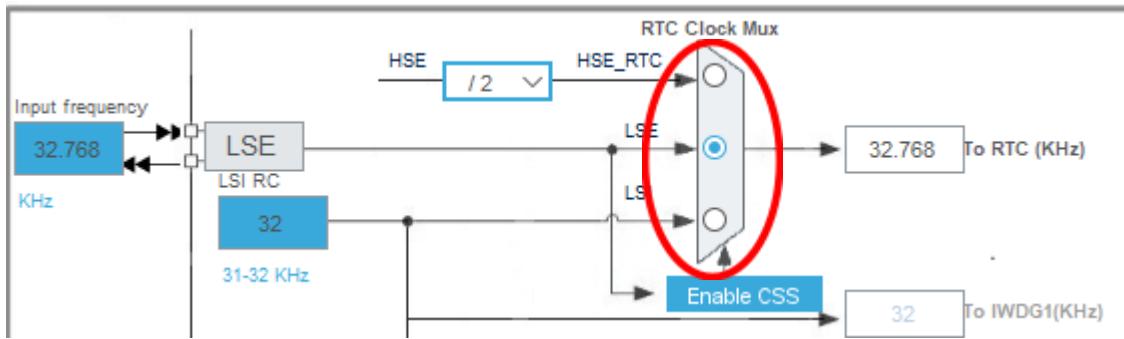

4. Clique na aba “Clock Configuration” para ver a “árvore” de distribuição de sinais de relógio. Na parte superior, há um bloco denominado LSE, que usa o cristal de 32.768kHz para gerar o clock de precisão de 1Hz. Mais à direita deste bloco, há um seletor de fonte, e a seleção deve ser modificada da entrada inferior para a do meio como ilustra a seguinte figura.

5. Para entender como os módulos GPIO e RTC realmente funcionam, vamos criar nossas próprias funções em vez de usarmos as funções de inicialização geradas automaticamente pelo STM32CubeMX no arquivo `main.c`. Comentamos as seguintes linhas de instruções.

(a) a variável global usada para processar dados referentes a RTC

```

/* Private variables -----*/

//RTC_HandleTypeDef hrtc;

```

(b) os protótipos dessas funções

```

/* Private function prototypes -----*/

void SystemClock_Config(void);

//static void MX_GPIO_Init(void);

//static void MX_RTC_Init(void);

```

(c) as chamadas dessas funções

```

/* Initialize all configured peripherals */

// MX_GPIO_Init();

// MX_RTC_Init();

```

(d) as definições dessas funções

```

/***

* @brief RTC Initialization Function

* @param None

* @retval None

*/

static void MX_RTC_Init(void)

{

/*

* USER CODE BEGIN RTC_Init_0

*/

/*

* USER CODE END RTC_Init_0

*/

/*

* USER CODE BEGIN RTC_Init_1

*/

/*

* USER CODE END RTC_Init_1

*/

/**

* Initialize RTC Only

*/

hrtc.Instance = RTC;

hrtc.Init.HourFormat = RTC_HOURFORMAT_24;

hrtc.Init.AsynchPrediv = 127;

hrtc.Init.SynchPrediv = 255;

hrtc.Init.OutPut = RTC_OUTPUT_DISABLE;

hrtc.Init.OutPutPolarity = RTC_OUTPUT_POLARITY_HIGH;

hrtc.Init.OutPutType = RTC_OUTPUT_TYPE_OPENDRAIN;

hrtc.Init.OutPutRemap = RTC_OUTPUT_REMAP_NONE;

if (HAL_RTC_Init(&hrtc) != HAL_OK)

{

Error_Handler();

}

}

```

```

// }

// /* USER CODE BEGIN RTC_Init_2 */

//

// /* USER CODE END RTC_Init_2 */

//

// */

// /**

// * @brief GPIO Initialization Function

// * @param None

// * @retval None

// */

// static void MX_GPIO_Init(void)

//{

//     GPIO_InitTypeDef GPIO_InitStruct = {0};

//     /* USER CODE BEGIN MX_GPIO_Init_1 */

//     /* USER CODE END MX_GPIO_Init_1 */

//

//     /* GPIO Ports Clock Enable */

//     __HAL_RCC_GPIOC_CLK_ENABLE();

//     __HAL_RCC_GPIOF_CLK_ENABLE();

//     __HAL_RCC_GPIOH_CLK_ENABLE();

//     __HAL_RCC_GPIOB_CLK_ENABLE();

//     __HAL_RCC_GPIOD_CLK_ENABLE();

//     __HAL_RCC_GPIOG_CLK_ENABLE();

//     __HAL_RCC_GPIOA_CLK_ENABLE();

//     __HAL_RCC_GPIOE_CLK_ENABLE();

//

//     /*Configure GPIO pin Output Level */

//     HAL_GPIO_WritePin(USB_FS_PWR_EN_GPIO_Port, USB_FS_PWR_EN_Pin, GPIO_PIN_RESET);

//

//     /*Configure GPIO pin Output Level */

//     HAL_GPIO_WritePin(GPIOB, LD1_Pin|LD3_Pin, GPIO_PIN_RESET);

//

//     /*Configure GPIO pin Output Level */

//     HAL_GPIO_WritePin(LD2_GPIO_Port, LD2_Pin, GPIO_PIN_RESET);

//

//     /*Configure GPIO pin : B1_Pin */

//     GPIO_InitStruct.Pin = B1_Pin;

//     GPIO_InitStruct.Mode = GPIO_MODE_INPUT;

//     GPIO_InitStruct.Pull = GPIO_NOPULL;

//     HAL_GPIO_Init(B1_GPIO_Port, &GPIO_InitStruct);

//

//     /*Configure GPIO pin : USB_FS_PWR_EN_Pin */

//     GPIO_InitStruct.Pin = USB_FS_PWR_EN_Pin;

//     GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;

//     GPIO_InitStruct.Pull = GPIO_NOPULL;

//     GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

//     HAL_GPIO_Init(USB_FS_PWR_EN_GPIO_Port, &GPIO_InitStruct);

//

//     /*Configure GPIO pins : LD1_Pin LD3_Pin */

//     GPIO_InitStruct.Pin = LD1_Pin|LD3_Pin;

//     GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;

//     GPIO_InitStruct.Pull = GPIO_NOPULL;

//     GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

//     HAL_GPIO_Init(GPIOB, &GPIO_InitStruct);

//

//     /*Configure GPIO pins : STLINK_RX_Pin STLINK_TX_Pin */

//     GPIO_InitStruct.Pin = STLINK_RX_Pin|STLINK_TX_Pin;

//     GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

//     GPIO_InitStruct.Pull = GPIO_NOPULL;

//     GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

//     GPIO_InitStruct.Alternate = GPIO_AF7_USART3;

//     HAL_GPIO_Init(GPIOD, &GPIO_InitStruct);

//

//     /*Configure GPIO pin : USB_FS_OVCR_Pin */

//     GPIO_InitStruct.Pin = USB_FS_OVCR_Pin;

//     GPIO_InitStruct.Mode = GPIO_MODE_IT_RISING;

```

```

// GPIO_InitStruct.Pull = GPIO_NOPULL;

// HAL_GPIO_Init(USB_FS_OVCR_GPIO_Port, &GPIO_InitStruct);

//

// /*Configure GPIO pin : USB_FS_ID_Pin */

// GPIO_InitStruct.Pin = USB_FS_ID_Pin;

// GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

// GPIO_InitStruct.Pull = GPIO_NOPULL;

// GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

// GPIO_InitStruct.Alternate = GPIO_AF10_OTG1_HS;

// HAL_GPIO_Init(USB_FS_ID_GPIO_Port, &GPIO_InitStruct);

//

// /*Configure GPIO pins : USB_FS_N_Pin USB_FS_P_Pin */

// GPIO_InitStruct.Pin = USB_FS_N_Pin|USB_FS_P_Pin;

// GPIO_InitStruct.Mode = GPIO_MODE_AF_PP;

// GPIO_InitStruct.Pull = GPIO_NOPULL;

// GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

// HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);

//

// /*Configure GPIO pin : LD2_Pin */

// GPIO_InitStruct.Pin = LD2_Pin;

// GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;

// GPIO_InitStruct.Pull = GPIO_NOPULL;

// GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_LOW;

// HAL_GPIO_Init(LD2_GPIO_Port, &GPIO_InitStruct);

//

///* USER CODE BEGIN MX_GPIO_Init_2 */

///* USER CODE END MX_GPIO_Init_2 */

//}

```

6. Vamos adicionar agora as nossas funções de configuração. Primeiro, os protótipos das nossas funções de inicialização dos pinos GPIO que alimentam os LEDs verde e amarelo e do RTC depois da linha `/* USER CODE BEGIN PFP */`

```

/* USER CODE BEGIN PFP */

void LD1_LD2_PInit(void);

void RTC_PInit(void);

/* USER CODE END PFP */

```

Em seguida, as suas chamadas depois da linha `/* USER CODE BEGIN 2 */`

```

/* USER CODE BEGIN 2 */

LD1_LD2_PInit();

RTC_PInit();

/* USER CODE END 2 */

```

7. Vamos iniciar com a definição da função `RTC_PInit` começando com a habilitação do sinal de relógio do RTC pelo registrador [RCC\\_APB4ENR](#).

```

void RTC_PInit(void) {

// Habilitar o sinal de ativação de RTC (por padrão, é habilitado no reset)

RCC->APB4ENR |= RCC_APB4ENR_RTCAPBEN_Msk;

}

```

9. Após um *reset* geral do sistema, os registradores do RTC são protegidos contra escritas acidentais. Essa proteção é controlada pelo *bit* DBP (do inglês *Disable Backup Power*) do registrador [PWR\\_CR1](#) presente em um módulo de controle de energia (PWR). É preciso setar esse *bit* e aguardar a habilitação da escrita nos registradores do RTC com as seguintes instruções.

```

PWR->CR1 |= PWR_CR1_DBP;

while (!(PWR->CR1 & PWR_CR1_DBP)); // Aguarda a habilitação

```

10. Apenas após essa habilitação, podemos selecionar LSE como a fonte do sinal de relógio do RTC com o registrador [BCC\\_BDCR](#). O código de ativação de LSE já foi gerado pelo STM32CubeMX. Devemos, no entanto, garantir uma configuração limpa do RTC antes da seleção, resetando todo o domínio de *backup* do RTC (registradores do RTC, os registradores de *backup* e a configuração da fonte de *clock* do RTC) através do *bit* VSRST do registrador [RCC\\_BDCR](#) e limpando a fonte de relógio antiga com o *reset* dos *bits* RCC\_BDCR\_RTCSEL

```

RCC->BDCR |= RCC_BDCR_VSWRST;

RCC->BDCR &= ~RCC_BDCR_RTCSEL;

```

Aí saímos do modo *reset* e setamos, por fim, LSE como a nova fonte de relógio

```

RCC->BDCR &= ~RCC_BDCR_VSWRST;

RCC->BDCR |= (RCC_BDCR_RTCEN_Msk |

RCC_BDCR_RTCSEL_1);

```

11. Com o RTC habilitado, podemos configurar os registradores do RTC. Porém, por segurança, esses registradores são protegidos dos acessos de escrita. Apenas com a escrita da chave de desbloqueio no registrador [RTC\\_WPR](#) é liberado o acesso de escrita a eles:

```

RTC->WPR = 0xCAU; // Desbloquear a protecao de escrita

RTC->WPR = 0x53U;

```

12. Com os registradores do RTC desprotegidos, podemos seguir o [procedimento](#) descrito no Manual de Referência para configurar o horário e o dia no RTC.

```

RTC->ICSR |= RTC_ICSR_INIT; // Configura o RTC para o modo de inicialização

while (!(RTC->ICSR & RTC_ICSR_INITF)); // Aguarda a inicialização do RTC

RTC->CR &= ~RTC_CR_FMT; // Configura o formato de hora para 24 horas

// Configura o pre-scaler do RTC

RTC->PRER = (127 << RTC_PRER_PREDIV_A_Pos) | (255 << RTC_PRER_PREDIV_S_Pos);

// Configurar a hora

RTC->TR = ((2 << RTC_TR_HT_Pos) | (3 << RTC_TR_HU_Pos) | // Horas (23)

(4 << RTC_TR_MNT_Pos) | (5 << RTC_TR_MNU_Pos) | // Minutos (45)

(1 << RTC_TR_ST_Pos) | (2 << RTC_TR_SU_Pos)); // Segundos (12)

// Configurar a data

RTC->DR = ((2 << RTC_DR_YT_Pos) | (5 << RTC_DR_YU_Pos) | // Ano (2025 - 2000 = 25)

(0 << RTC_DR_MT_Pos) | (2 << RTC_DR_MU_Pos) | // Mês (Fevereiro = 2)

(2 << RTC_DR_DT_Pos) | (4 << RTC_DR_DU_Pos)); // Dia (24)

RTC->ICSR &= ~RTC_ICSR_INIT; // Sair do modo de inicialização

```

Deve-se entrar no modo de inicialização usando o registrador [RTC\\_ICSR](#), configurar o formato do horário através de [RTC\\_CR](#), setar os divisores de frequência em [RTC\\_PRER](#), e inicializar o RTC com o horário e data desejados através dos registradores [RTC\\_TR](#) e [RTC\\_DR](#). Daí sair do modo de inicialização. Segundo a [Nota de Aplicação](#), o fator de divisão do *prescaler* assíncrono é definido como 128, e o fator de divisão síncrono como 256, para obter uma frequência de *clock* interna de 1 Hz a partir de uma fonte LSE de frequência 32,768 kHz.

13. Após a inicialização do sistema, é possível configurar alarmes de tempo real para gerar eventos de interrupção que serão acionados em momentos específicos ou após um período determinado.

```

// Configura o alarme A para gerar eventos periódicos de 1s

RTC->CR &= ~RTC_CR_ALRAE; // Desabilita o Alarme A

RTC->CR &= ~RTC_CR_ALRAIE; // Desativa a interrupção do alarme A

// Limpar a flag de interrupção do alarme A

RTC->SCR |= RTC_SCR_CALRAF_Msk;

while (!(RTC->ICSR & RTC_ICSR_ALRAWF)); // Aguarda pronto para configuração

RTC->ALRMAR &= ~(RTC_ALRMAR_PM); // Formato 24 horas

// Programa o evento alarme para cada segundo

RTC->ALRMAR |= (RTC_ALRMAR_MSK4 | RTC_ALRMAR_MSK3 | RTC_ALRMAR_MSK2 | RTC_ALRMAR_MSK1);

// Desconsiderar data, hora, minuto, segundo

// Habilita o Alarme A

RTC->CR |= RTC_CR_ALRAE;

// Habilita a interrupção do alarme

RTC->CR |= RTC_CR_ALRAIE;

// Configura o alarme B para gerar um único evento 1 minuto após o reset

RTC->CR &= ~RTC_CR_ALRBE; // Desabilita o alarme B

RTC->CR &= ~RTC_CR_ALRBIE; // Desativa a interrupção do alarme B

// Limpar flag de interrupção do alarme B

RTC->SCR |= RTC_SCR_CALRBF_Msk;

while !(RTC->ICSR & RTC_ICSR_ALRBWF)); // Aguarda pronto para configuração

RTC->ALRMBR &= ~(RTC_ALRMBR_PM); // Formato 24h

// Define o evento de alarme para ocorrer exatamente 1 minuto depois

RTC->ALRMBR = (RTC_ALRMAR_MSK4 |

(2 << RTC_ALRMBR_HT_Pos) | (3 << RTC_ALRMBR_HU_Pos) | // Horas (23)

(4 << RTC_ALRMBR_MNT_Pos) | ((5 + 1) << RTC_ALRMBR_MNU_Pos) | // Minutos

(1 << RTC_ALRMBR_ST_Pos) | (2 << RTC_ALRMBR_SU_Pos) ); // Segundos (12)

// Habilita o Alarme B

RTC->CR |= RTC_CR_ALRBE;

// Habilita interrupção do Alarme B

RTC->CR |= RTC_CR_ALRBIE;

```

Seguimos o [procedimento](#) recomendado no Manual de Referência. Em primeiro lugar, desabilitamos o alarme e sua interrupção com [RTC\\_CR](#), limpamos a *flag* de interrupção correspondente com [RTC\\_SCR](#) e aguardamos que o registrador [RTC\\_ICSR](#) indique que o alarme esteja pronto para programação. Em seguida, programamos pelos registradores [RTC\\_ALRMAR](#) ou [RTC\\_ALRMBR](#) os eventos de interrupção. E concluimos com a reabilitação do alarme e sua interrupção. Neste projeto, configuramos o alarme A para gerar eventos de interrupção periódica de 1s e o alarme B para gerar eventos de interrupção periódica diária às 23:46:12. Detalhes dessas configurações são encontradas na [Nota de Aplicação do RTC](#).

14. Reative a proteção contra escrita, garantindo que os registradores do RTC não sejam alterados inadvertidamente após a configuração.

```

RTC->WPR = 0xFFU; // Bloquear acesso de escrita

```

15. Habilite a interrupção do RTC Alarm no NVIC, permitindo que o microcontrolador atenda ao evento quando ele ocorrer. A posição do vetor de interrupção do RTC Alarm IRQn no STM32 é 41.

```

NVIC_SetPriority(RTC_Alarm_IRQn, 1); // Configura a prioridade da interrupção

NVIC_EnableIRQ(RTC_Alarm_IRQn); // Habilita a interrupção no NVIC

```

16. Habilite a interrupção do evento de entrada 17 do EXTI e configure a sensibilidade para a borda de subida

```

EXTI->IMR1 |= EXTI_IMR1_IM17_Msk; // habilita a interrupção do evento de entrada 17

EXTI->RTSR1 |= EXTI_RTSR1_TR17_Msk; // captura na borda de subida

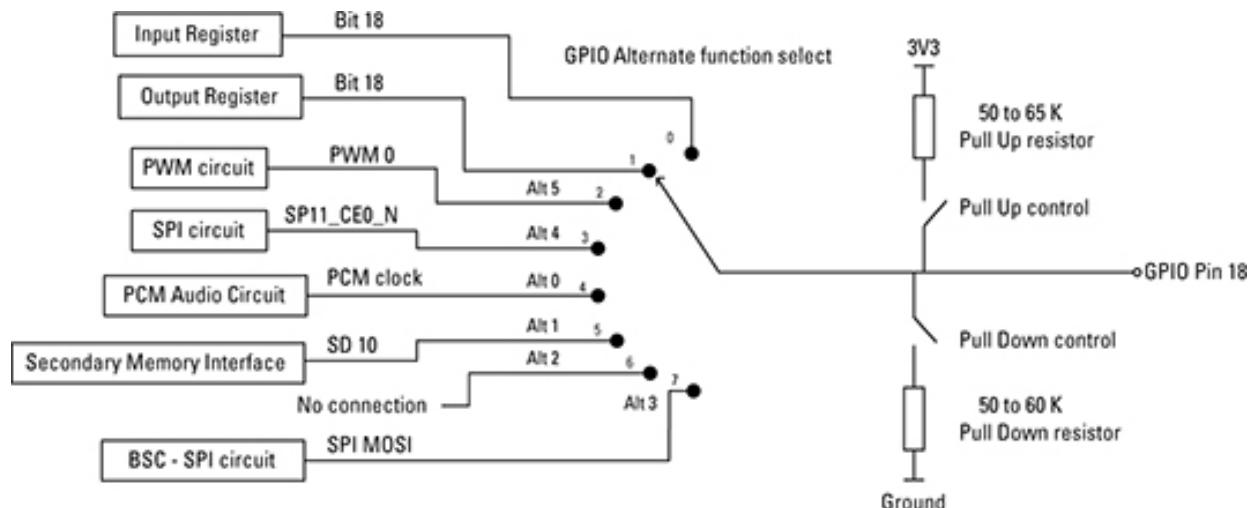

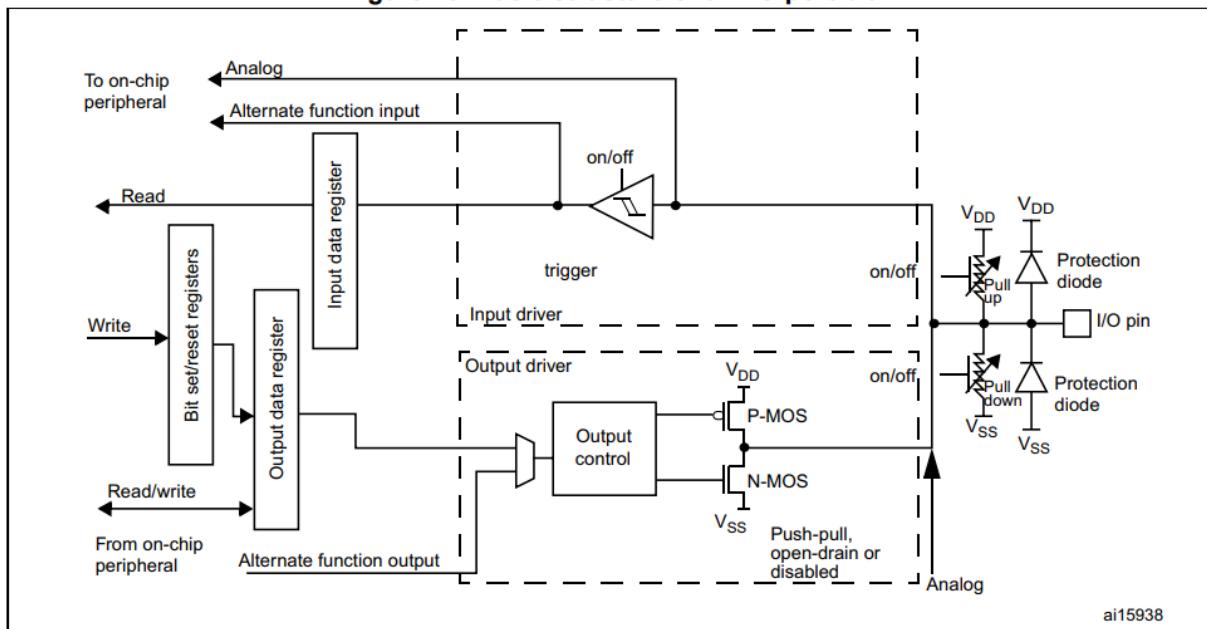

```