# **DISCIPLINA EA701**

## **Introdução aos Sistemas Embarcados**

**ROTEIRO 6: TEMPORIZADORES AVANÇADOS,

PINOS MULTIPLEXÁVEIS, PWM, OUTPUT COMPARE (OC), INPUT

CAPTURE (IC), RELÓGIO EXTERNO, INTERFACES (PONTE-H,

ENCODER)**

**Profs. Antonio A. F. Quevedo e Wu Shin-Ting**

**FEEC / UNICAMP**

**Revisado e modificado em abril de 2025 por Ting com auxílio do Chatgpt**

**Revisado em setembro de 2024**

This work is licensed under Creative Commons

Attribution-NonCommercial-ShareAlike 4.0 International. To view a copy of this

license, visit <https://creativecommons.org/licenses/by-nc-sa/4.0>

|                                    |           |

|------------------------------------|-----------|

| <b>INTRODUÇÃO</b>                  | <b>2</b>  |

| <b>PROJETOS-EXEMPLO</b>            | <b>3</b>  |

| Projeto de Output Compare          | 3         |

| Projeto de Input Capture           | 12        |

| Projeto de PWM                     | 20        |

| Projeto de Relógio Externo         | 25        |

| <b>FUNDAMENTOS TEÓRICOS</b>        | <b>30</b> |

| PRELIMINARES                       | 32        |

| OUTPUT COMPARE                     | 33        |

| INPUT CAPTURE                      | 34        |

| PWM                                | 35        |

| CONTADORES DE EVENTOS EXTERNOS     | 37        |

| LINEARIZAÇÃO DE CONTAGEM CÍCLICA   | 39        |

| UMA APLICAÇÃO IC/OC: CRONÔMETRO    | 40        |

| <b>INTERFACES COM MUNDO FÍSICO</b> | <b>41</b> |

| PONTE-H                            | 41        |

| ENCODERS                           | 43        |

| <b>STM32H7A3</b>                   | <b>45</b> |

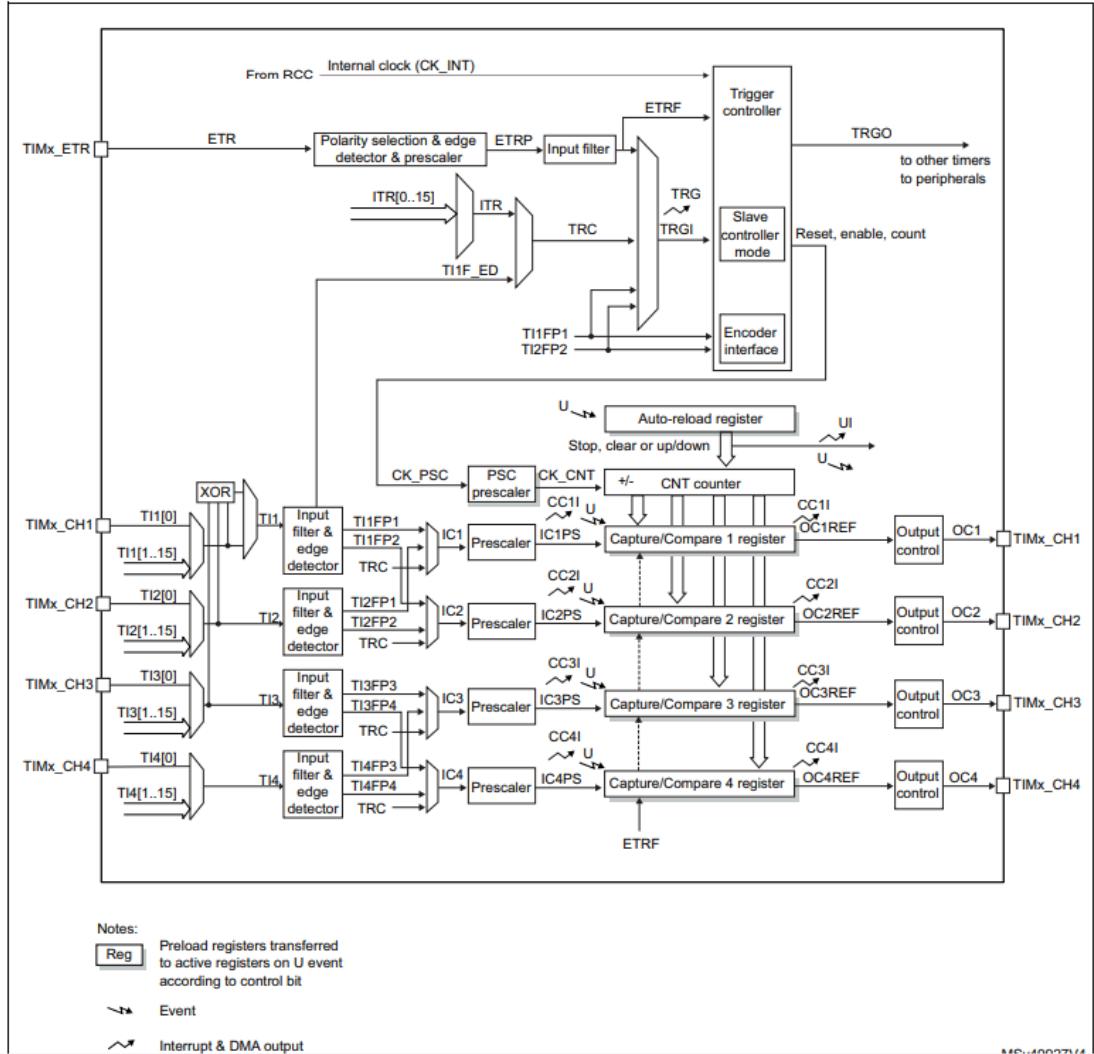

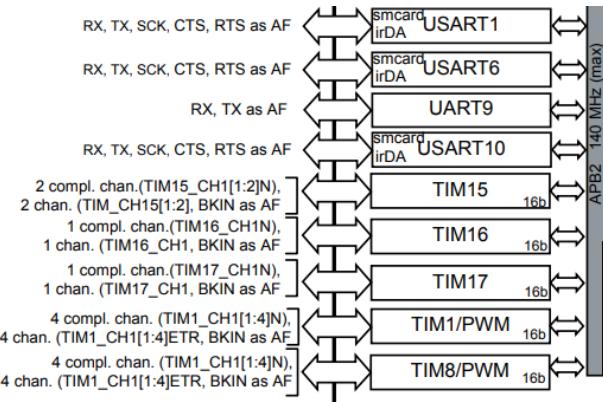

| TIM2/TIM3/TIM4/TIM5                | 46        |

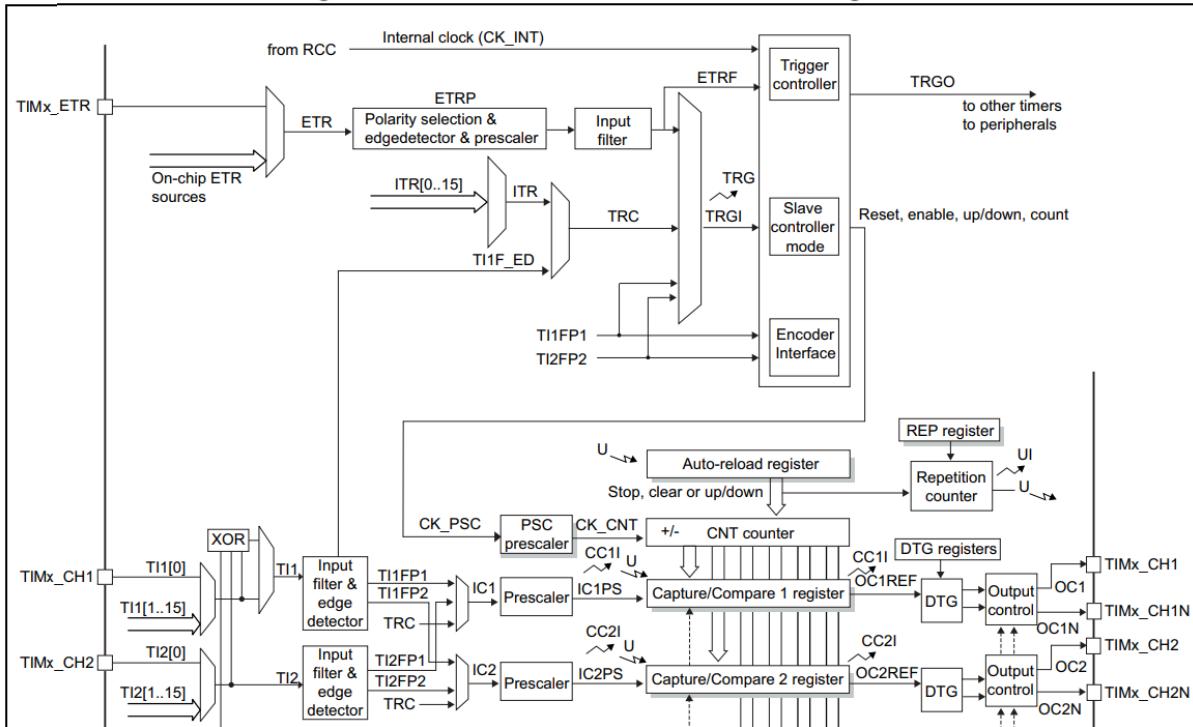

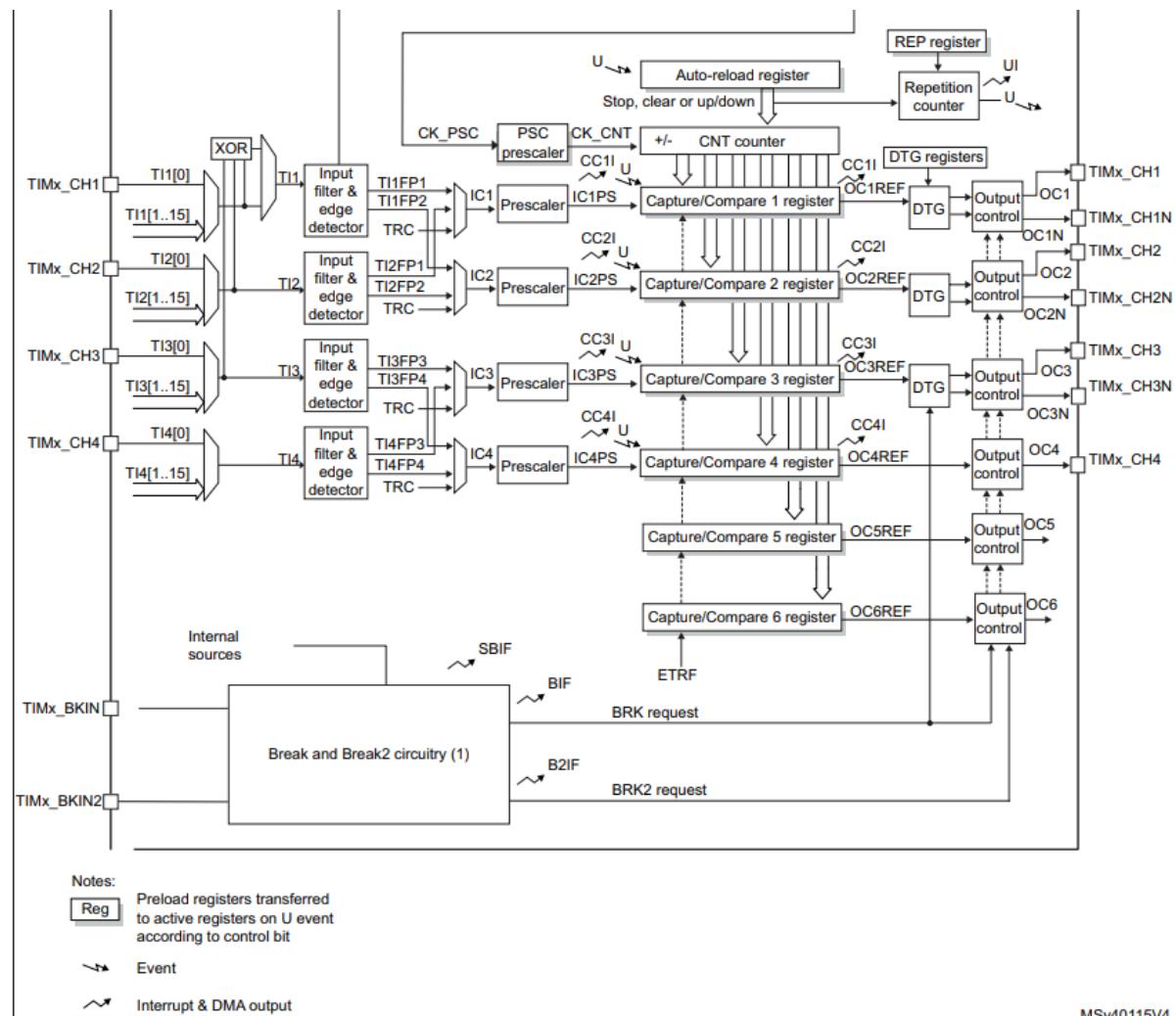

| TIM1/TIM8                          | 48        |

| Modo Output Compare                | 56        |

| Modo Input Capture                 | 58        |

| Modo PWM                           | 59        |

| Modo de Relógio Externo            | 62        |

| <b>STM32CubeMX</b>                 | <b>65</b> |

## INTRODUÇÃO

Dando continuidade ao estudo dos *timers*, exploraremos funções avançadas que estendem o *timer* padrão. A versatilidade dos temporizadores permite implementar funcionalidades que **interagem diretamente com o mundo físico**, oferecendo controle preciso de tempo e coordenação de eventos em tempo real. No Roteiro 6, exemplificamos temporizadores de pulso único, cujos sinais são acessíveis externamente. Neste roteiro, apresentaremos outras funcionalidades de interação com o mundo externo, como a **Captura de Entradas** (em inglês, *Input Capture* – IC), que registra o valor do contador no momento de um evento externo, e a **Comparação de Saídas** (em inglês, *Output Compare* – OC), que compara o valor do contador com um valor predefinido para executar ações específicas, como gerar pulsos. A **Modulação por Largura de Pulso** (em inglês, *Pulse Width Modulation* – PWM) permite a geração de sinais de saída com largura de pulso variável, controlando a potência fornecida a dispositivos. Além disso, o **Contador de Eventos Externos** (em inglês, *Pulse Counter*) realiza a contagem de pulsos ou eventos que ocorrem fora do microcontrolador.

Essas funcionalidades, padronizadas em muitos microcontroladores, facilitam o controle preciso de eventos temporais e a geração de sinais pulsados em intervalos definidos, encontrando aplicações em diversas áreas, desde o controle de LEDs e motores até sistemas de comunicação e medição de alta precisão.

Ao interagir com o mundo físico, deve-se considerar a interface entre o microcontrolador e o mundo físico, que pode envolver dispositivos com faixas de operação de tensão e corrente significativamente diferentes das que o microcontrolador pode diretamente fornecer ou tolerar. Muitos microcontroladores operam dentro de faixas de tensão e corrente bem limitadas, o que significa que suas saídas precisam ser adaptadas para controlar dispositivos externos que podem exigir tensões e correntes muito maiores ou menores. A integração bem-sucedida dessas funcionalidades avançadas dos temporizadores com o mundo físico frequentemente exige circuitos de interface, como *drivers* de potência, amplificadores ou conversores de nível, para garantir que o microcontrolador possa controlar dispositivos externos de forma segura e eficaz.

## PROJETOS-EXEMPLO

Abordaremos quatro problemas específicos que ilustram o uso das funcionalidades que envolvem interações com o mundo físico externo: a geração de sinais de saída sincronizados com um sinal de referência, a medição precisa de períodos de sinais, o controle de potência de alimentação de dispositivos e a contagem de eventos externos. As técnicas envolvidas incluem, respectivamente, comparação de saídas (OC), captura de entradas (IC), modulação por largura de pulso (PWM) e contador de eventos externos.

### Projeto de *Output Compare*

Você já pensou em gerar um sinal sincronizado com um sinal de referência? O desafio é o alinhamento preciso desses dois sinais devido às latências. Tem ideia como contornar este problema usando os temporizadores disponíveis nos microcontroladores? Vamos criar um projeto que demonstra como os temporizadores de um microcontrolador podem ser utilizados para superar esse desafio? O projeto é dividido em três partes:

- 1. Geração de sinais sincronizados em baixa frequência:** Utilizaremos um temporizador para gerar no modo OC sinais em baixa frequência com 2 valores distintos de comparação. Esses sinais demonstrarão como é possível gerar múltiplos sinais sincronizados com precisão.

- 2. Verificação da precisão em alta frequência:** Um segundo temporizador será configurado no modo OC para gerar um sinal em alta frequência.

- 3. Demonstração da latência de interrupções:** Um terceiro temporizador será utilizado para gerar um sinal periódico numa saída GPIO através de interrupções. Esse sinal

demonstrará, em comparação com o sinal gerado no modo OC, como a latência de interrupções pode afetar a precisão da geração de sinais temporais.

Os pinos de saída dos temporizadores serão conectados aos canais de um analisador lógico, permitindo verificar a precisão da sincronização em tempo real.

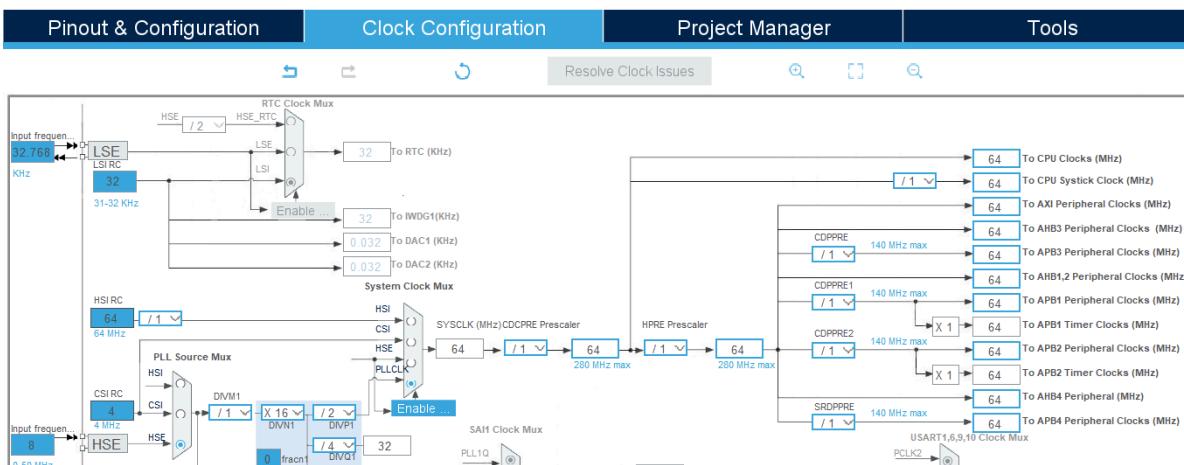

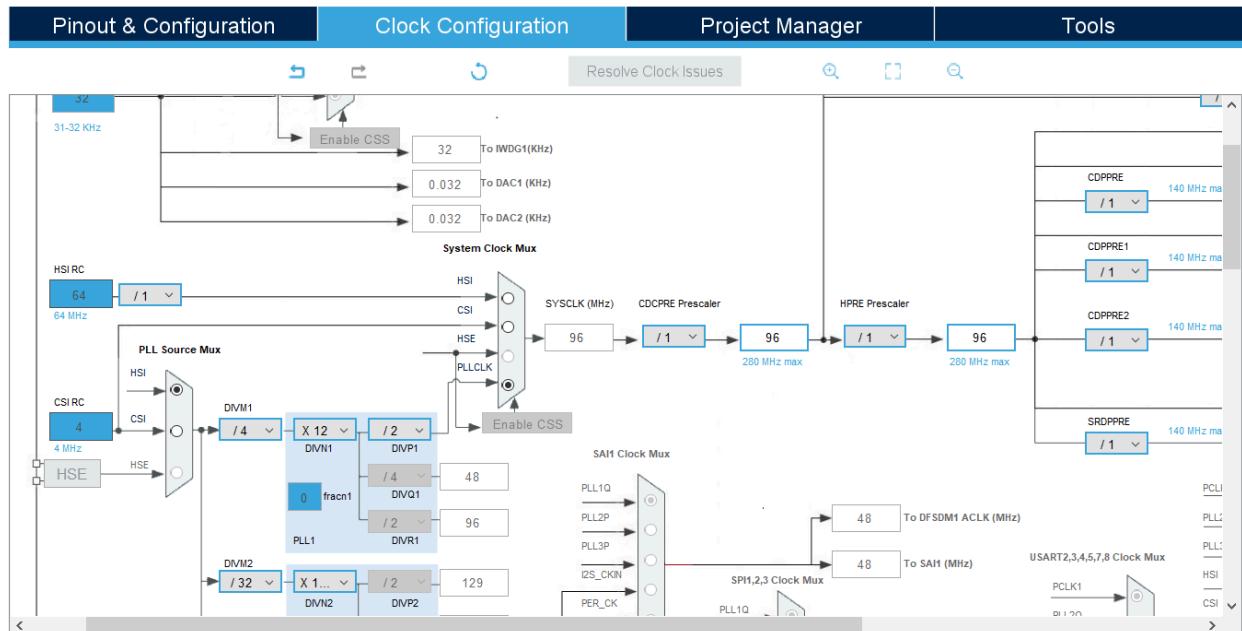

1. Crie um projeto usando o *Cube* com o nome “Output\_Compare”, **sem inicialização dos periféricos em modo default**. Ative o módulo *Debug* como “Serial Wire”. O projeto visa comparar sinais periódicos gerados por duas abordagens distintas: uma baseada em interrupções periódicas, que envolve a alteração programática dos estados do sinal, e outra utilizando o modo *Output Compare*, onde as mudanças são realizadas diretamente em *hardware*. A comparação desses métodos permitirá avaliar a precisão de cada abordagem na geração e controle de sinais periódicos. Na aba de configuração de *clock*, localize o bloco entre “*CDCPRE Prescaler*” e “*HPRE Prescaler*”, e mude o valor para 64 (MHz). O *Cube* irá calcular automaticamente os valores de multiplicação de frequência para que a frequência geral do sistema mude para o valor digitado.

2. Gere o código de configuração do sistema de sinais de relógio. Abra o arquivo *Core/Src/main.c*.

3. Comente (Remova) a declaração, a definição e a chamada da função *MX\_GPIO\_Init(void)*. Adicione a declaração das seguintes funções de configuração dos periféricos GPIOB, GPIOE, TIM1, TIM2 e TIM6 no escopo */\* USER CODE BEGIN PFP \*/*:

```

//static void MX_GPIO_Init(void);

/* USER CODE BEGIN PFP */

void PB11_PInit(void);

void PE11_PInit(void);

void PE9_PInit(void);

void TIM2C4_PInit(void);

void TIM1C2_PInit(void);

void TIM6_PInit(void);

/* USER CODE END PFP */

```

4. Vamos definir as funções de configuração dos pinos PB11 e PE11, multiplexados para os periféricos TIM2 e TIM1, respectivamente.

```

void PB11_PInit (void) {

// Ativa GPIOB (PB11)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN_Msk;

// Configurar PB11 como função alternativa

GPIOB->MODER &= ~GPIO_MODER_MODE11_Msk;

GPIOB->MODER |= GPIO_MODER_MODE11_1;

// Selecionar AF1 para PE11

GPIOB->AFR[1] &= ~(0xF << GPIO_AFRH_AFSEL11_Pos);

GPIOB->AFR[1] |= (1 << GPIO_AFRH_AFSEL11_Pos);

// Configurar PB11 como push-pull

GPIOB->OTYPER &= ~GPIO_OTYPER_OT11;

}

void PE11_PInit (void) {

// Ativa GPIOE (PE11)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOEEN_Msk;

// Configurar PE11 como função alternativa

GPIOE->MODER &= ~GPIO_MODER_MODE11_Msk;

GPIOE->MODER |= GPIO_MODER_MODE11_1;

// Selecionar AF1 para PE11

GPIOE->AFR[1] &= ~(0xF << GPIO_AFRH_AFSEL11_Pos);

GPIOE->AFR[1] |= (1 << GPIO_AFRH_AFSEL11_Pos);

// Configurar PE11 como push-pull

GPIOE->OTYPER &= ~GPIO_OTYPER_OT11;

}

```

De acordo com a [Tabela 9](#) e [Tabela 12](#) do *Datasheet*, a função alternativa para ambos os periféricos é AF1. O tipo de configuração de saída nos dois pinos é *push-pull*.

5. Vamos ainda definir a função de configuração do pino **PE9** para que ele seja um pino GPIO de saída *push-pull*, iniciando em nível baixo (que é o *default*), no escopo `/* USER CODE BEGIN 4 */`.

```

void PE9_PInit (void) {

// Ativa GPIOE (PE9)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOEEN_Msk;

// PE9 como saída digital

GPIOE->MODER &= ~(GPIO_MODER_MODE9_Msk);

GPIOE->MODER |= GPIO_MODER_MODE9_0;

GPIOE->OTYPER &= ~GPIO_OTYPER_OT9_Msk; // PE9 como push-pull

}

```

O pino será usado para mostrar o trem de pulsos gerado pelo TIM6 a ser configurado com a função de interrupções periódicas de 10µs.

6. Agora passamos para a configuração dos temporizadores, vamos começar com a configuração do temporizador básico, TIM6, para operar como um temporizador de

interrupção periódica (do inglês, *periodic interrupt timer* - PIT). Insira o seguinte código depois da definição da função **PE9\_PInit (void)**.

```

void TIM6_PInit(void) {

RCC->APB1LENR |= RCC_APB1LENR_TIM6EN; // Habilita clock de TIM6

TIM6->EGR |= TIM_EGR_UG_Msk; // atualizacao inicial dos registradores

while (TIM6->EGR & TIM_EGR_UG);

TIM6->CR1 &= ~TIM_CR1_CEN; // Desabilita o contador

TIM6->PSC = 64-1; // Prescaler, assumindo clock de 64 MHz, timer a 1 MHz

TIM6->ARR = 10-1; // Período do timer: 1/1MHz * 10 = 10us

TIM6->CR1 &= ~TIM_CR1_UDIS; // Habilita a geracao do evento de atualizacao

TIM6->DIER |= TIM_DIER_UIE; // Habilita a interrupcao

// Habilitar interrupcao TIM6 no NVIC

NVIC_SetPriority(TIM6_DAC_IRQn, 1); // Define a prioridade da interrupcao

NVIC_EnableIRQ(TIM6_DAC_IRQn); // Habilita a interrupcao TIM6

TIM6->CR1 |= TIM_CR1_CEN; // Habilita o contador

}

```

Como a frequência do sinal de relógio é 64 MHz, configuramos o *Prescaler* para “64-1” e o *autoreload* para “10-1”. Além disso, habilitamos a interrupção de TIM6 no NVIC (número de vetor 54) e configuramos sua prioridade de atendimento em 1, como habilitamos a geração de eventos de interrupção no TIM6. Assim, teremos uma interrupção periódica a cada 10µs.

7. Vamos configurar o TIM1 para o seu canal 2 operar no modo *Output Compare*. Insira a seguinte função de configuração de TIM1 depois da definição da função **TIM6\_PInit(void)**.

```

void TIM1C2_PInit(void) {

// Habilitar o clock para o Timer TIM1

RCC->APB2ENR |= RCC_APB2ENR_TIM1EN_Msk;

TIM1->EGR |= TIM_EGR_UG_Msk; // Atualizacão inicial dos registradores

while (TIM1->EGR & TIM_EGR_UG);

// Configurar PSC e ARR

TIM1->PSC = 64-1; // Prescaler

TIM1->ARR = 10-1; // Período

// Configurar o modo de operacao do canal TIM1_CH2 para Output Compare:

TIM1->CCMR1 &= ~(TIM_CCMR1_CC2S_1 | TIM_CCMR1_CC2S_0); // Modo Output Compare

// Configurar o sinal de saída do canal TIM1_CH2

TIM1->CCMR1 |= TIM_CCMR1_OC2M_1 | TIM_CCMR1_OC2M_0; // Modo Toggle

// Habilitar a precarga do valor de comparacao

TIM1->CCMR1 |= TIM_CCMR1_OC2PE;

// Configurar o valor de comparacao para 0

TIM1->CCR2 = 0;

// Habilitar a saida

TIM1->BDTR |= TIM_BDTR_MOE; // Master Output Enable

// Habilitar o canal TIM1_CH2

TIM1->CCER |= TIM_CCER_CC2E;

// Habilitar o Timer

```

```

TIM1->CR1 |= TIM_CR1_CEN; // Iniciar a contagem

}

```

Em cada *match*, ou seja quando o valor do contador do TIM1 fique igual ao conteúdo do registrador de comparação TIM1->CCR2, o sinal é alternado (*toggle*). Ajustamos a frequência do relógio do temporizador TIM1 para 1MHz, atribuindo “64-1” ao *Prescaler*. Setamos “10-1” como contagem máxima no *autoreload*. O valor de comparação é setado em “10”. Habilitamos também a pré-carga do valor de comparação, para que as modificações nos registradores de comparação sejam efetivadas apenas quando ocorrem eventos de atualização. Note que para o evento *match* ser reconhecido como um evento de interrupção, a máscara de interrupção do canal 2 precisa ser habilitada. Além disso, TIM1 precisa habilitar um *bit* de *Master Output Enable* para que as saídas dos canais sejam exteriorizadas nos pinos correspondentes. Por fim, o *timer* em si precisa ser habilitado para contar, através do *bit* CEN no registrador CR1.

**Obs: A comparação do valor do contador com o registrador de “captura/comparação” (*Capture/Compare Register* ou CCR) é assíncrona, portanto aqui não existe o fator “-1” usado no *prescaler* e no *autoreload*). Isto vale tanto no OC como no IC e no PWM.**

Entende por que os registradores são configurados de maneiras diferentes? Se não, sem problemas! Vamos explorar isso juntos mais adiante.

8. E adicionamos também, após a função **TIM1C2\_PInit(void)**, a definição da função que configura o canal 4 do temporizador TIM2 para o modo de operação OC com a alternância do nível do sinal de saída em cada *match*.

```

void TIM2C4_PInit(void) {

// Habilitar o clock para o Timer TIM2

RCC->APB1LENR |= RCC_APB1LENR_TIM2EN_Msk;

TIM2->EGR |= TIM_EGR_UG_Msk; // Atualização inicial dos registradores

while (TIM2->EGR & TIM_EGR_UG);

// Configurar PSC e ARR

TIM2->CR1 &= ~TIM_CR1_ARPE_Msk; // Desabilita precarga de autoreload

TIM2->PSC = 64-1; // Prescaler

TIM2->ARR = 65536-1; // Período

// Configurar o modo de operação do canal TIM2_CH4 para Output Compare:

TIM2->CCMR2 &= ~TIM_CCMR2_CC4S_Msk; // Modo Output Compare

// Configurar o sinal de saída do canal TIM1_CH2

TIM2->CCMR2 &= ~TIM_CCMR2_OC4M_Msk;

TIM2->CCMR2 |= TIM_CCMR2_OC4M_1 | TIM_CCMR2_OC4M_0; // Modo Toggle

// Habilitar a precarga do valor de comparação (pag 1551)

TIM2->CCMR2 |= TIM_CCMR2_OC4PE;

// Setar a polaridade

TIM2->CCER &= ~TIM_CCER_CC4P; // ativo alto

// Configurar o valor de comparação para 10

TIM2->CCR4 = 10;

//Habilitar a interrupção do canal 4

}

```

```

TIM2->DIER |= TIM_DIER_CC4IE; // Habilita a interrupcao

// Habilitar interrupcao TIM1 no NVIC

NVIC_SetPriority(TIM2 IRQn, 2); // Define a prioridade da interrupcao

NVIC_EnableIRQ(TIM2 IRQn); // Habilita a interrupcao TIM2 IRQn

// Habilitar o canal TIM1_CH2

TIM2->CCER |= TIM_CCER_CC4E;

// Habilitar o Timer

TIM2->CR1 |= TIM_CR1_CEN; // Iniciar a contagem

}

```

E, habilitamos a interrupção de TIM2, com a prioridade de atendimento em 2, no NVIC (número de vetor 27) e a geração de eventos de interrupção do canal 4 no TIM2. Usaremos essas interrupções para modificar o conteúdo do registrador de comparação como veremos adiante. Para que essas atualizações não conflictam com as atualizações dos sinais de saída, é importante habilitar a pré-carga do registrador *auto-reload*. Lembre-se do papel importante dos registradores pré-carga e sombra na integridade de dados destacado no Roteiro 5?

9. Por fim, dentro da área `/* USER CODE BEGIN 2 */`, chame as funções:

```

PE9_PInit();

TIM6_PInit();

PE11_PInit();

TIM1C2_PInit();

PB11_PInit();

TIM2C4_PInit();

```

Nada será feito no *loop* infinito.

10. Precisa-se ainda implementar as definições das rotinas de serviço, `void TIM2_IRQHandler (void)` e `void TIM6_DAC_IRQHandler (void)`, predeclaradas em `Startup/startup_stm32h7a3xxq.s` para tratamento das interrupções. Abra o arquivo `Core/Src/stm32h7xx_it.c` e insira depois de `/* USER CODE BEGIN 1 */` a definição

```

void TIM6_DAC_IRQHandler (void)

{

static uint8_t pinon = 0; // estado logico do pino

if (TIM6->SR | TIM_SR_UIF) {

//Altera o estado logico do pino PE9

TIM6->SR *= ~TIM_SR_UIF; // limpa o bit de estado

if(pinon) {

pinon = 0;

GPIOE->BSRR = GPIO_BSRR_BR9; // reset pino PE9

} else {

pinon = 1;

GPIOE->BSRR = GPIO_BSRR_BS9; // set pino PE9

}

}

}

```

Note que é necessário limpar a *flag*, escrevendo 0 no *bit* de *Update Interrupt Flag* (veja no [Manual de Referência](#) que as *flags* deste registrador são limpas escrevendo-se o *bit* 0 (rc\_w0) nos mesmos). Na sequência, inverte-se a variável de estado do pino e o nível lógico em PE9. Aqui vamos gerar uma onda quadrada no pino PE9, alternando o nível do sinal de saída em cada *match*.

11. Em seguida, insira a definição da segunda rotina de serviço:

```

void TIM2_IRQHandler (void)

{

static uint16_t cnt=0;

if(TIM2->SR & TIM_SR_CC4IF) { //Flag interrupcao TIM1_CH2

TIM2->SR &= ~TIM_SR_CC4IF; // Limpa flag

if (TIM2->CCR4 == 10 && cnt < 3) {

cnt++;

} else if (TIM2->CCR4 == 10 && cnt == 3) {

cnt = 0;

TIM2->CCR4 = TIM2->ARR/4; // proxima transicao em 0

} else if (TIM2->CCR4 == TIM2->ARR/4 && cnt < 3) {

cnt++;

} else if (TIM2->CCR4 == TIM2->ARR/4 && cnt == 3){

cnt = 0;

TIM2->CCR4 = 10; // proxima transicao em 5

}

}

}

```

A cada *match*, o *hardware* realiza o *toggle* do pino instantaneamente, e ativa uma interrupção ([IRQ 28](#)). Note que a interrupção tem uma latência, mas o *toggle* sempre ocorrerá no instante preciso. Inicialmente, a rotina de serviço verifica se ocorreu um evento de OC no canal 4 do TIM2. Se este for o caso, a *flag* é limpa segundo a política de limpeza rc\_w0. Para demonstrar que o *toggle* se repita periodicamente em intervalos precisos para valores de distintos no registrador TIM2->CCR4, definimos 2 valores de comparação, 10 e TIM2->ARR/4. Esses valores são setados depois de 3 períodos de contagem máxima, seguindo a lógica programada e atualizados apenas quando ocorrem os eventos de atualização.

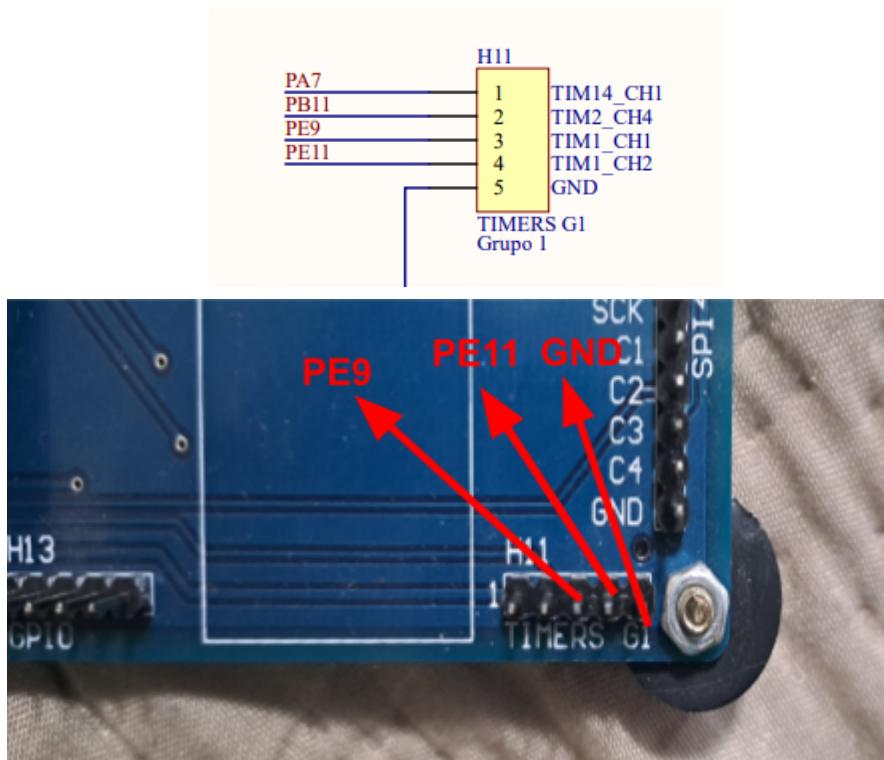

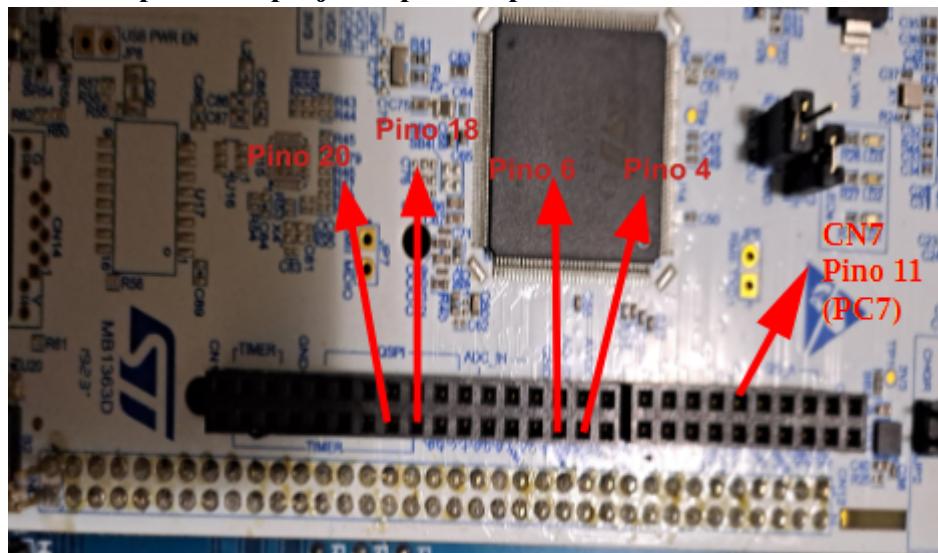

11. Realize um *Build* no código, verificando se não há erros. Transfira o código executável para o microcontrolador no modo *Debug*. Antes de realizar o *Debug*, vamos ligar o analisador lógico nos pinos de saída. Conecte o canal 2 do analisador lógico ao [pino 2 do Header H11 \(PB11\)](#), o [canal 1 ao pino 4 \(PE11\)](#) e [canal 0 ao pino 3 do mesmo Header \(PE9\)](#), além do pino GND do analisador ao pino 5 do mesmo *Header* (GND). As figuras abaixo mostram os pontos de conexão, sob duas distintas perspectivas.

Em seguida, conecte o analisador a uma porta USB do desktop e abra o [aplicativo Logic 2.4.x](#).

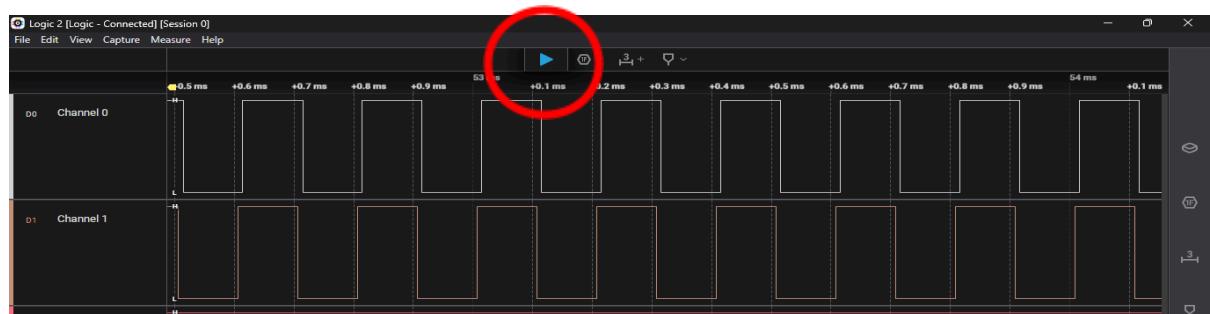

11. Transfira o programa executável ao microcontrolador no modo *Debug*. Inicie a execução do programa. Clique na seta azul do aplicativo para inicializar a captura dos sinais nos pinos PB11, PE9 e PE11 pelo analisador lógico. Para párar a coleta, basta clicar no quadrado azul no mesmo local.

12. A frequência do sinal de relógio dos contadores dos três temporizadores, TIM6, TIM1 e TIM2, é 64MHz. Meça os períodos (larguras dos pulsos em nível alto) dos sinais capturados nos pinos e preencha a tabela abaixo

| Pino | TIMx->PSC | TIMx->ARR | TIMx->CCRn | Período Estimado | Período Medido |

|------|-----------|-----------|------------|------------------|----------------|

|      |           |           |            |                  |                |

|      |           |           |            |                  |                |

|      |           |           |            |                  |                |

Os valores observados (medidos) são condizentes com os esperados (estimados)? As larguras dos pulsos positivos (nível 1) dependem do valor de comparação configurados? Você saberia justificar a sua resposta? Se tiver dúvidas, continue os exercícios. A explicação será apresentada mais adiante.

13. Compare a configuração dos registradores dos temporizadores TIM1/TIM2 com TIM6. Qual(is) deles permite(m) configurar o modo de operação OC? Através de qual(is) registrador(es)?

14. Na configuração do TIM2, a pré-carga do valor máximo (em inglês, *autoreload*) foi desabilitada, enquanto no TIM1, a pré-carga do valor de comparação (TIM1->CCR2) foi habilitada. O que é pré-carga de um registrador? O que é um evento de atualização? O que aconteceria se removêssemos essas instruções? Como você acha que o comportamento do sistema seria afetado? Não se preocupe se a resposta não vier à mente agora! Vamos desvendarmos juntos os segredos por trás dessas configurações mais adiante.

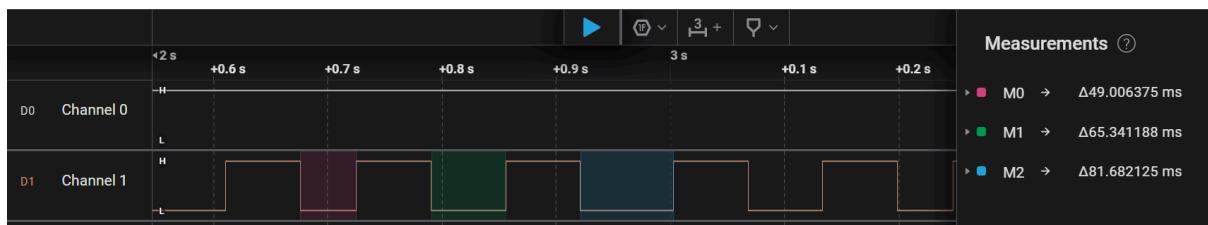

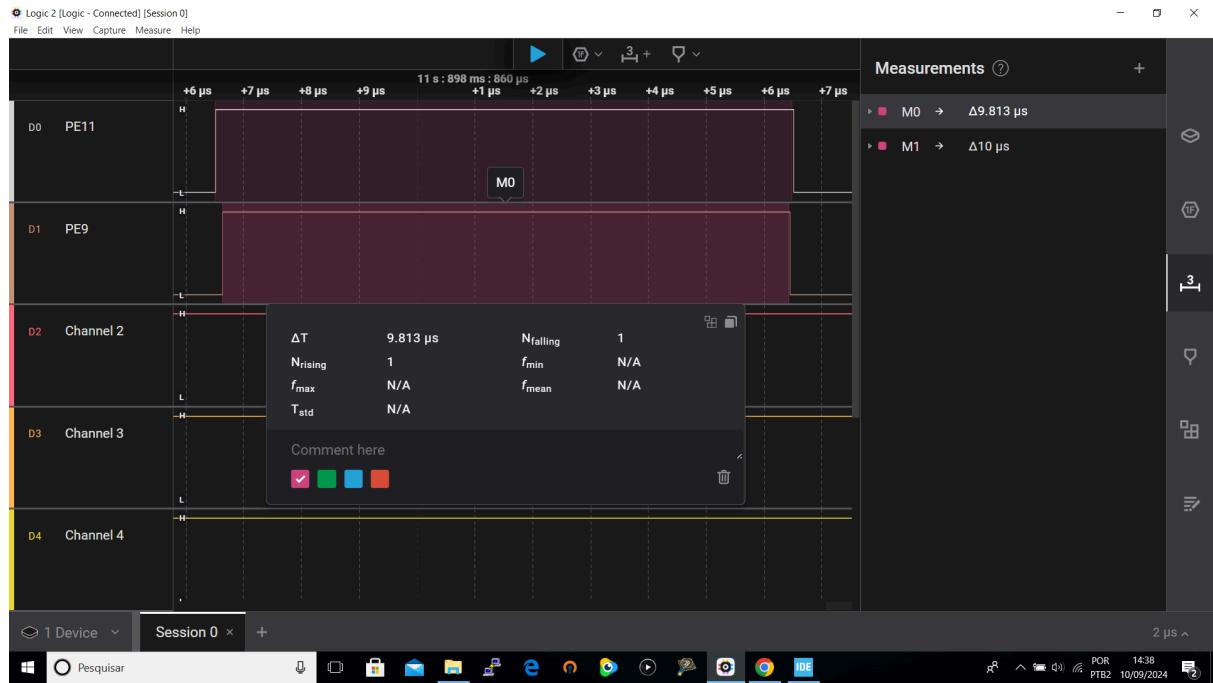

15. Você consegue identificar três pulsos em nível baixo com larguras diferentes na forma de onda capturada no pino PB11 (Canal 2)? Observe a figura abaixo e compare com suas medições. Agora, reflita: Os valores que você mediu concordam com os mostrados na imagem capturada que se segue? Qual parte do código pode estar gerando essa variação? Esses valores fazem sentido com a configuração programada? Se ainda não tem certeza, não se preocupe! As explicações mais adiante vão te ajudar a entender exatamente o que está acontecendo.

16. Agora vamos comparar o grau de precisão dos períodos dos sinais gerados de duas formas diferentes: o modo OC do canal TIM1\_CH2 (Canal 1) e as interrupções periódicas do temporizador TIM6 (Canal 0). Sabemos que, em ambos os casos, o período do *timer* é de

10µs, o que significa que cada sinal deve permanecer 10µs em nível alto e 10µs em nível baixo, totalizando um período completo de 20µs.

Aumente a resolução (*zoom in*) da sua captura de sinal e meça os tempos em nível alto e baixo nos dois canais, como a imagem capturada. Compare os valores medidos com os apresentados na imagem capturada. Tente responder as seguintes perguntas: Qual dos dois sinais está mais próximo do valor esperado? Por quê há diferenças entre eles? O que pode estar influenciando essas variações? Se tiver dúvidas, vamos investigar juntos!

15. Compare as instruções usadas na configuração do canal TIM1\_CH2 e do temporizador TIM6. Qual das duas abordagens envolve menos registradores adicionais para gerar resultados bem similares?

## Projeto de *Input Capture*

Você já precisou medir intervalos de tempo com alta precisão? Em muitos projetos eletrônicos e sistemas embarcados, é essencial capturar a diferença de tempo entre eventos assíncronos, como a detecção de bordas de subida e descida de um sinal. Para isso, utilizaremos a funcionalidade *Input Capture* (IC), uma ferramenta que mede com exatidão esses intervalos. No projeto em questão, vamos gerar uma onda assimétrica usando laços simples e GPIO, medir os tempos em nível alto e baixo dessa onda, detectando as bordas de subida e descida, e comparar os valores medidos com os obtidos por um analisador lógico. O desafio está em como garantir que nossa medição seja precisa e eficiente? Será que conseguimos reduzir ao máximo os erros? Vamos descobrir com o seguinte projeto que mede

o intervalo entre dois instantes assíncronos, definidos por um par de bordas de descida/subida?

1. Crie o projeto usando o *Cube*, com o nome “Input\_Capture”, **sem a inicialização dos periféricos**. Ative o módulo *Debug* como “Serial Wire”. Entre no editor gráfico de “Clock Configuration” e configure a frequência do sistema em 96 MHz em uma das janelas embaixo dos quais tem o texto “280 MHz max.”

2. Gere o código de configuração do sistema de sinais de relógio. Abra o arquivo Core/Src/main.c.

3. Comente (Remova) a declaração, a definição e a chamada da função `MX_GPIO_Init(void)`. Adicione a declaração das seguintes funções de configuração dos periféricos GPIOA, GPIOB e TIM1 e de interface entre o arquivo `main.c` e `stm32h7xx_it.c` no escopo `/* USER CODE BEGIN PFP */`:

```

void PA8_PInit (void);

void PE11_PInit (void);

void TIM1C2_PInit(void);

void le_dados_captura (uint16_t *arg1, uint16_t *arg2, uint16_t *arg3, uint8_t

*arg4);

void set_last_edge (uint8_t i);

```

**Observação:** Evitar variáveis globais e utilizar a passagem de valores via funções são práticas essenciais para o desenvolvimento de *software* robusto, manutenível e reutilizável. Essas técnicas promovem a modularidade, o encapsulamento e facilitam a depuração e o teste do código.

4. Vamos inserir a definição da função de configuração do pino PA8 para o modo de operação GPIO com o tipo de saída *push-pull* no escopo `/* USER CODE BEGIN 4 */`

```

void PA8_PInit (void) {

// Ativa GPIOE (PE9)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOAEN_Msk;

// PE9 como saida digital

GPIOA->MODER &= ~(GPIO_MODER_MODE8_Msk);

GPIOA->MODER |= GPIO_MODER_MODE8_0;

GPIOA->OTYPER &= ~GPIO_OTYPER_OT8_Msk; // PA8 como push-pull

}

```

O pino PA8 servirá como nosso gerador de onda assimétrica, alimentando o pino PE11.

5. O pino PE11 é multiplexado para o canal TIM1\_CH2 configurado no modo de operação IC. Insira após a definição de **PA8\_PInit (void)** a seguinte função

```

void PE11_PInit (void) {

// Ativa GPIOE (PE11)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOEEN_Msk;

// Configurar PE11 como função alternativa

GPIOE->MODER &= ~GPIO_MODER_MODE11_Msk;

GPIOE->MODER |= GPIO_MODER_MODE11_1;

// Selecionar AF1 para PE11

GPIOE->AFR[1] &= ~(0xF << GPIO_AFRH_AFSEL11_Pos);

GPIOE->AFR[1] |= (1 << GPIO_AFRH_AFSEL11_Pos);

}

```

Observe que, servindo agora como pino de entrada, a sua configuração é ligeiramente diferente da configuração do projeto anterior.

6. Por fim, precisamos definir logo a seguir a função de configuração do canal TIM1\_CH2 para operar no modo de operação IC, sensível às duas bordas (de subida e descida)

```

void TIM1C2_PInit(void) {

// Habilitar o clock para o Timer TIM1

RCC->APB2ENR |= RCC_APB2ENR_TIM1EN_Msk;

TIM1->EGR |= TIM_EGR_UG_Msk; // Atualização inicial dos registradores

while (TIM1->EGR & TIM_EGR_UG);

// Configurar PSC e ARR

TIM1->CR1 &= ~TIM_CR1_ARPE_Msk; // Desabilita precarga de autoreload

TIM1->PSC = 96-1; // Prescaler

TIM1->ARR = 65536-1; // Período

// Configurar o modo de operação do canal TIM1_CH2 para Input:

TIM1->CCMR1 &= ~(TIM_CCMR1_CC2S_1 | TIM_CCMR1_CC2S_0);

TIM1->CCMR1 |= TIM_CCMR1_CC2S_0; // PE11 mapeado na entrada TI1 (página 1522)

// Configurar a detecção de ambas bordas

TIM1->CCER |= (TIM_CCER_CC2NP | TIM_CCER_CC2P); // Detecção de ambas bordas

// Habilitar a interrupção do canal 2

TIM1->DIER |= TIM_DIER_CC2IE; // Habilita a interrupção

// Habilitar interrupção TIM1 no NVIC

NVIC_SetPriority(TIM1_CC IRQn, 1); // Define a prioridade da interrupção

NVIC_EnableIRQ(TIM1_CC IRQn); // Habilita a interrupção TIM1_CC IRQn

}

```

```

// Habilitar o canal TIM1_CH2

TIM1->CCER |= TIM_CCER_CC2E;

// Habilitar o Timer

TIM1->CR1 |= TIM_CR1_CEN; // Iniciar a contagem

}

```

Para configurar o *timer* TIM1 com um clock de 96 MHz, iniciamos definindo um prescaler de 96, que atua como um divisor da frequência do *clock*, seguido pela configuração de um valor máximo de contagem, conhecido como *auto-reload*, para 65536. Essa combinação de configurações garante que cada incremento no contador TIM1->CNT corresponda a um intervalo de tempo de 1µs. Adicionalmente, habilitamos a interrupção do TIM1 no NVIC, utilizando o [vetor de interrupção 27](#), e asseguramos a geração de eventos de interrupção no canal TIM1\_CH2. Por fim, para controlar a prioridade de atendimento da interrupção, definimos o nível de prioridade como 1.

7. Vamos abrir agora o arquivo `Core/Src/stm32h7xx_it.c` para incluir a rotina de serviço que calcula os intervalos de tempo entre a borda de subida e descida. Para isso, vamos declarar algumas variáveis na área `/* USER CODE BEGIN 1 */`

```

uint16_t last_capture=0;

uint16_t duration_high=0;

uint16_t duration_low=0;

uint8_t last_edge;

uint16_t current_capture;

int32_t tmp;

```

antes de inserir a rotina de serviço

```

void TIM1_CC_IRQHandler (void)

{

if(TIM1->SR & TIM_SR_CC2IF) { //Flag interrupcao TIM1_CH2

current_capture = (uint16_t)TIM1->CCR2; // Flag e limpo na leitura do

CCRx

if (last_capture == 0) {

last_capture = current_capture;

}

tmp = current_capture - last_capture;

if (last_edge == 0) {

// Borda de subida (fim de nível baixo, inicio de nível alto)

if (tmp >= 0) {

duration_low = (uint16_t) tmp;

} else {

duration_low = (uint16_t)(TIM1->ARR + 1 + tmp);

}

last_edge = 1; // Próxima borda será de descida

} else {

// Borda de descida (fim de nível alto, inicio de nível

baixo

}

}

}

```

```

if (tmp >= 0) {

duration_high = (uint16_t) tmp;

} else {

duration_high = (uint16_t)(TIM1->ARR + 1 + tmp);

}

last_edge = 0; // Próxima borda será de subida

}

// Atualize o último valor de captura

last_capture = current_capture;

}

}

```

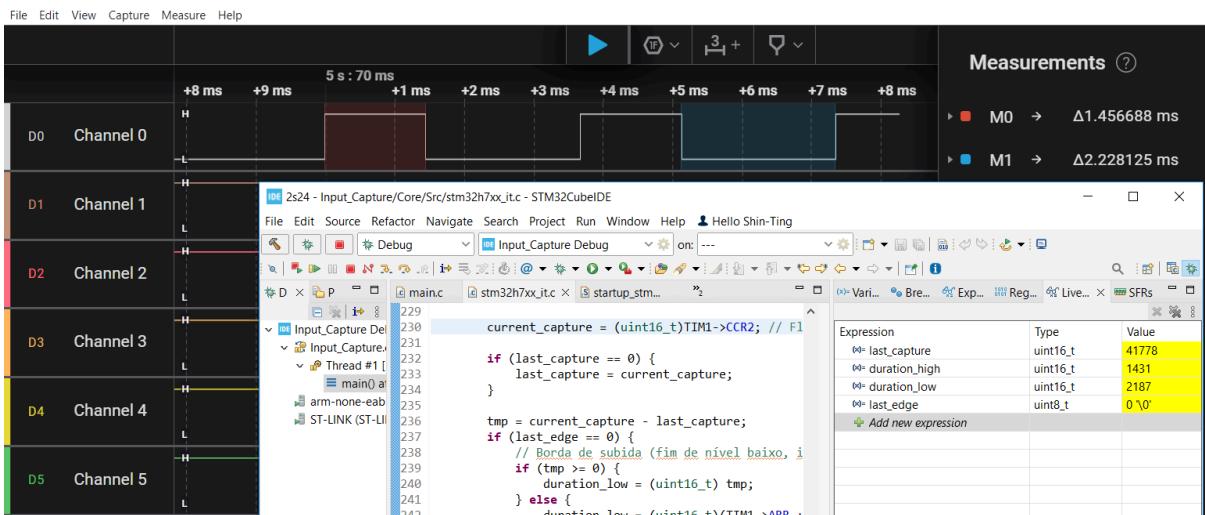

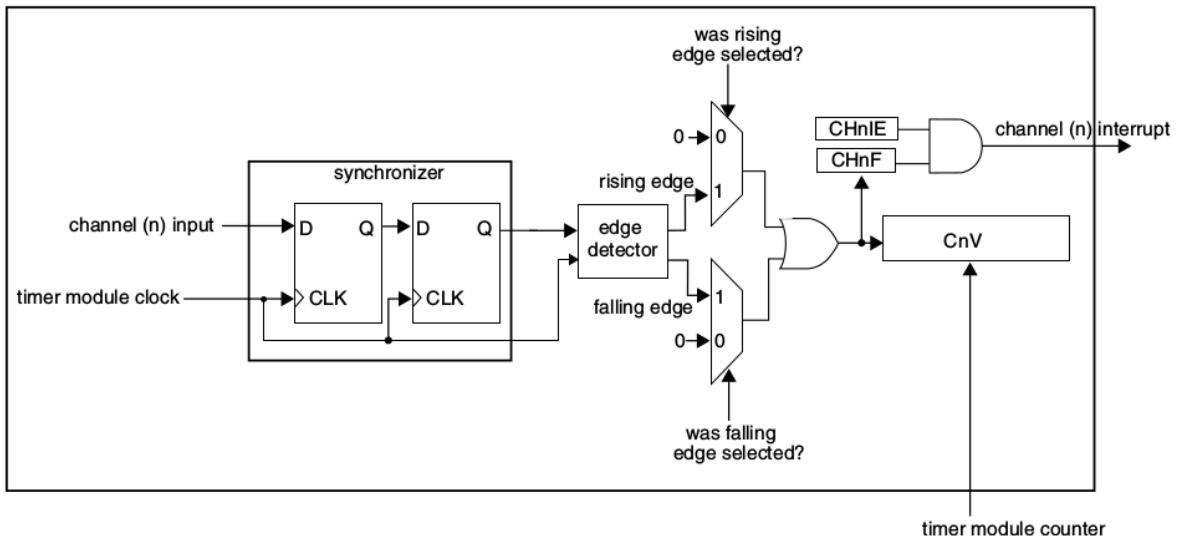

Essencialmente, a rotina de serviço calcula, na captura de uma borda, a quantidade de contagens entre duas capturas sucessivas, diferenciando-a entre pulsos de nível alto (duration\_high) e pulsos de nível baixo (duration\_low). Inicialmente, ela verifica se o evento foi gerado em TIM1\_CH2 (PE11). Em seguida, usa a função para ler o valor presente no registrador TIM1->CCR2. Na sequência, dependendo da última borda, calcula o valor do tempo em nível alto ou em nível baixo, atualizando a borda e o último valor lido.

É importante ressaltar que quando ocorre um evento de IC no pino de um canal do *timer*, o valor do contador do *timer* é imediatamente (via *hardware*) copiado no registrador CCR do canal correspondente. Assim, o registrador CCR guarda a informação do momento exato em que o evento ocorreu. Mesmo que haja a latência de interrupção, o que será usado nos cálculos não é o valor atual do contador (que pode ter mudado durante a latência), mas o valor de CCR, que corresponde ao valor de contagem **no momento do evento de IC**. Isto garante a alta precisão nas medições.

Note que o registrador CCR2 é de 32 *bits*, apesar de o contador ser de 16 *bits*. Assim, é realizado um *cast* para 16 *bits* ao se copiar o valor na variável current\_capture. Se o valor é lido como de 16 *bits* sem sinal, quando ocorrer um *overflow* no contador, o mesmo *overflow* ocorrerá no cálculo da diferença entre a captura atual e a anterior. Assim, o valor calculado será sempre o número de pulsos contabilizados entre eventos sucessivos. Como exemplo, imagine que o valor lido é 60000 e o valor anterior é 50000. A variável “duration\_\*” irá guardar o valor 10000, ou seja, 10ms. Imagine que mais 10000 pulsos sejam contados antes do próximo evento. Neste caso, o contador irá contar mais 10000 pulsos totalizando  $700000 = 0b1\ 0001\ 0001\ 0111\ 0000$  pulsos. Como o contador só tem 16 *bits*, somente  $0b0001\ 0001\ 0111\ 0000 = 4464$  é considerado. Isso equivale a contar 5536 pulsos e voltar a zero (*overflow*), contando mais 4464 pulsos antes do evento. Assim, no próximo cálculo, a variável “duration\_\*” será  $4464 - 60000 = -5536$  que, por *rollover*, deve ser ajustado somando 65536 que resulta em 10000.

Observe ainda que neste caso, não inserimos a instrução `TIM1->SR &= ~TIM_SR_CC2IF;` para limpar a *flag*, pois o acesso de leitura ao registrador TIM1->CCR2 limpa automaticamente a flag.

8. Para a passagem dos dados entre os arquivos main.c e stm32h7xx\_it.c, vamos implementar mais duas funções:

```

void le_dados_captura (uint16_t *arg1, uint16_t *arg2, uint16_t *arg3, uint8_t *arg4) {

*arg1 = last_capture;;

*arg2 = duration_high;

*arg3 = duration_low;

*arg4 = last_edge;

}

```

```

void set_last_edge (uint8_t i) {

last_edge = i;

}

```

e declarar os seus protótipos tanto em main.c (área `/* USER CODE BEGIN PFP */`) quanto em stm32h7xx\_it.c (também na área `/* USER CODE BEGIN PFP */`).

```

void le_dados_captura (uint16_t *arg1, uint16_t *arg2, uint16_t *arg3, uint8_t *arg4);

void set_last_edge (uint8_t i);

```

9. Agora vamos declarar as variáveis locais de `main()`, uma variável para definir o estado inicial do sinal lido em PE11 e outra variável para gerar *delays* (não muito exatos) através de laços. Na área `/* USER CODE BEGIN 2 */`, declare as variáveis:

```

GPIO_PinState pin_state;

uint32_t i;

```

10. Vamos incluir na área `/* USER CODE BEGIN 2 */` da função `main` as chamadas das funções de configuração dos periféricos

```

PA8_PInit();

PE11_PInit();

TIM1C2_PInit();

```

e instruções de detecção do nível inicial do sinal no pino de entrada PE11

```

//Estado inicial de PE11

pin_state = GPIOE->IDR & GPIO_IDR_ID11_Msk;

if (pin_state == GPIO_PIN_SET) {

set_last_edge (1); // Inicia em nível alto, então a primeira borda será

de descida

} else {

set_last_edge (0); // Inicia em nível baixo, então a primeira borda será

de subida

}

```

11. Para gerar um trem de pulsos no pino PA8 que vai alimentar o pino PE11 de entrada do canal TIM1\_CH2, vamos incluir o seguinte bloco de instruções na área `/* USER CODE BEGIN 3 */`, dentro do laço infinito

```

for(i = 0; i < 13000; i++){}

GPIOA->BSRR = GPIO_BSRR_BS8;

for(i = 0; i < 8000; i++){}

GPIOA->BSRR = GPIO_BSRR_BR8;

//Atualiza os dados de captura

uint16_t arg1, arg2, arg3;

uint8_t arg4;

le_dados_captura (&arg1, &arg2, &arg3, &arg4);

```

12. Realize um *Build* e verifique se não há erros. Antes de executar o programa, precisamos interligar a saída da onda (PA8) à entrada TIM1\_CH2 (PE11). Para isso, vamos usar os headers fêmea da placa NUCLEO, conforme mostra a figura a seguir. **Obs: Esta figura serve de referência para este projeto e para os próximos.**

Existem 4 conectores pretos de linha dupla (conectores Zio) organizados em duas fileiras na placa. O conector embaixo à direita é o CN10, e nele podemos acessar PA8 (pino 4) e PE11 (pino 6). Note que PE11 deste *header* e o PE11 do *header* H11 correspondem a dois acessos distintos ao pino físico PE11 do microcontrolador.

|       |       | CN8   |     | CN7  |      |      |       |

|-------|-------|-------|-----|------|------|------|-------|

| NC    | NC    | 1 2   | D43 | PC8  | PC6  | D16  | 1 2   |

| IOREF | IOREF | 3 4   | D44 | PC9  | PB15 | D17  | 3 4   |

| NRST  | RESET | 5 6   | D45 | PC10 | PB13 | D18  | 5 6   |

| 3V3   | +3V3  | 7 8   | D46 | PC11 | PB12 | D19  | 7 8   |

| 5V    | +5V   | 9 10  | D47 | PC12 | PA15 | D20  | 9 10  |

| GND   | GND   | 11 12 | D48 | PD2  | PC7  | D21  | 11 12 |

| GND   | GND   | 13 14 | D49 | PG10 | PB5  | D22  | 13 14 |

| VIN   | VIN   | 15 16 | D50 | PG8  | PB3  | D23  | 15 16 |

| PA3   | A0    | 1 2   | D51 | PD7  | PA4  | D24  | 17 18 |

| PC0   | A1    | 3 4   | D52 | PD6  | AGND | AVDD | 1 2   |

| PC3   | A2    | 5 6   | D53 | PD5  | PC1  | D16  | 3 4   |

| PB1   | A3    | 7 8   | D54 | PD4  | PC5  | D17  | 5 6   |

| PC2   | A4    | 9 10  | D55 | PD3  | PA2  | D18  | 7 8   |

| PF11  | A5    | 11 12 | GND | GND  | PG6  | D22  | 9 10  |

| PB2   | D72   | 13 14 | D56 | PE2  | PB2  | D27  | 11 12 |

| PE9   | D71   | 15 16 | D57 | PE4  | GND  | D28  | 13 14 |

| PB5   | D70   | 17 18 | D58 | PE5  | PD13 | D29  | 15 16 |

| PF14  | D69   | 19 20 | D59 | PE6  | PD12 | D30  | 17 18 |

| PF15  | D68   | 21 22 | D60 | PE3  | PD11 | D31  | 19 20 |

| GND   | GND   | 23 24 | D61 | PF8  | PE2  | D32  | 21 22 |

| PDO   | D67   | 25 26 | D62 | PF7  | GND  | D33  | 23 24 |

| PDI   | D66   | 27 28 | D63 | PF9  | PA0  | D34  | 25 26 |

| PB14  | D65   | 29 30 | D64 | PD10 | PB0  | D35  | 27 28 |

|       |       |       |     |      | PE0  | D36  | 29 30 |

|       |       |       |     |      |      | D37  | 31 32 |

|       |       |       |     |      |      | D38  | 33 34 |

|       |       |       |     |      |      | D39  | 35    |

|       |       |       |     |      |      | D40  | D35   |

|       |       |       |     |      |      | D41  | D35   |

|       |       |       |     |      |      | D42  | D35   |

|       |       |       |     |      |      | D43  | D35   |

|       |       |       |     |      |      | D44  | D35   |

|       |       |       |     |      |      | D45  | D35   |

|       |       |       |     |      |      | D46  | D35   |

|       |       |       |     |      |      | D47  | D35   |

|       |       |       |     |      |      | D48  | D35   |

|       |       |       |     |      |      | D49  | D35   |

|       |       |       |     |      |      | D50  | D35   |

|       |       |       |     |      |      | D51  | D35   |

|       |       |       |     |      |      | D52  | D35   |

|       |       |       |     |      |      | D53  | D35   |

|       |       |       |     |      |      | D54  | D35   |

|       |       |       |     |      |      | D55  | D35   |

|       |       |       |     |      |      | D56  | D35   |

|       |       |       |     |      |      | D57  | D35   |

|       |       |       |     |      |      | D58  | D35   |

|       |       |       |     |      |      | D59  | D35   |

|       |       |       |     |      |      | D60  | D35   |

|       |       |       |     |      |      | D61  | D35   |

|       |       |       |     |      |      | D62  | D35   |

|       |       |       |     |      |      | D63  | D35   |

|       |       |       |     |      |      | D64  | D35   |

|       |       |       |     |      |      | D65  | D35   |

|       |       |       |     |      |      | D66  | D35   |

|       |       |       |     |      |      | D67  | D35   |

|       |       |       |     |      |      | D68  | D35   |

|       |       |       |     |      |      | D69  | D35   |

|       |       |       |     |      |      | D70  | D35   |

|       |       |       |     |      |      | D71  | D35   |

|       |       |       |     |      |      | D72  | D35   |

|       |       |       |     |      |      | D73  | D35   |

|       |       |       |     |      |      | D74  | D35   |

|       |       |       |     |      |      | D75  | D35   |

|       |       |       |     |      |      | D76  | D35   |

|       |       |       |     |      |      | D77  | D35   |

|       |       |       |     |      |      | D78  | D35   |

|       |       |       |     |      |      | D79  | D35   |

|       |       |       |     |      |      | D80  | D35   |

|       |       |       |     |      |      | D81  | D35   |

|       |       |       |     |      |      | D82  | D35   |

|       |       |       |     |      |      | D83  | D35   |

|       |       |       |     |      |      | D84  | D35   |

|       |       |       |     |      |      | D85  | D35   |

|       |       |       |     |      |      | D86  | D35   |

|       |       |       |     |      |      | D87  | D35   |

|       |       |       |     |      |      | D88  | D35   |

|       |       |       |     |      |      | D89  | D35   |

|       |       |       |     |      |      | D90  | D35   |

|       |       |       |     |      |      | D91  | D35   |

|       |       |       |     |      |      | D92  | D35   |

|       |       |       |     |      |      | D93  | D35   |

|       |       |       |     |      |      | D94  | D35   |

|       |       |       |     |      |      | D95  | D35   |

|       |       |       |     |      |      | D96  | D35   |

|       |       |       |     |      |      | D97  | D35   |

|       |       |       |     |      |      | D98  | D35   |

|       |       |       |     |      |      | D99  | D35   |

|       |       |       |     |      |      | D100 | D35   |

|       |       |       |     |      |      | D101 | D35   |

|       |       |       |     |      |      | D102 | D35   |

|       |       |       |     |      |      | D103 | D35   |

|       |       |       |     |      |      | D104 | D35   |

|       |       |       |     |      |      | D105 | D35   |

|       |       |       |     |      |      | D106 | D35   |

|       |       |       |     |      |      | D107 | D35   |

|       |       |       |     |      |      | D108 | D35   |

|       |       |       |     |      |      | D109 | D35   |

|       |       |       |     |      |      | D110 | D35   |

|       |       |       |     |      |      | D111 | D35   |

|       |       |       |     |      |      | D112 | D35   |

|       |       |       |     |      |      | D113 | D35   |

|       |       |       |     |      |      | D114 | D35   |

|       |       |       |     |      |      | D115 | D35   |

|       |       |       |     |      |      | D116 | D35   |

|       |       |       |     |      |      | D117 | D35   |

|       |       |       |     |      |      | D118 | D35   |

|       |       |       |     |      |      | D119 | D35   |

|       |       |       |     |      |      | D120 | D35   |

|       |       |       |     |      |      | D121 | D35   |

|       |       |       |     |      |      | D122 | D35   |

|       |       |       |     |      |      | D123 | D35   |

|       |       |       |     |      |      | D124 | D35   |

|       |       |       |     |      |      | D125 | D35   |

|       |       |       |     |      |      | D126 | D35   |

|       |       |       |     |      |      | D127 | D35   |

|       |       |       |     |      |      | D128 | D35   |

|       |       |       |     |      |      | D129 | D35   |

|       |       |       |     |      |      | D130 | D35   |

|       |       |       |     |      |      | D131 | D35   |

|       |       |       |     |      |      | D132 | D35   |

|       |       |       |     |      |      | D133 | D35   |

|       |       |       |     |      |      | D134 | D35   |

|       |       |       |     |      |      | D135 | D35   |

|       |       |       |     |      |      | D136 | D35   |

|       |       |       |     |      |      | D137 | D35   |

|       |       |       |     |      |      | D138 | D35   |

|       |       |       |     |      |      | D139 | D35   |

|       |       |       |     |      |      | D140 | D35   |

|       |       |       |     |      |      | D141 | D35   |

|       |       |       |     |      |      | D142 | D35   |

|       |       |       |     |      |      | D143 | D35   |

|       |       |       |     |      |      | D144 | D35   |

|       |       |       |     |      |      | D145 | D35   |

|       |       |       |     |      |      | D146 | D35   |

|       |       |       |     |      |      | D147 | D35   |

|       |       |       |     |      |      | D148 | D35   |

|       |       |       |     |      |      | D149 | D35   |

|       |       |       |     |      |      | D150 | D35   |

|       |       |       |     |      |      | D151 | D35   |

|       |       |       |     |      |      | D152 | D35   |

|       |       |       |     |      |      | D153 | D35   |

|       |       |       |     |      |      | D154 | D35   |

|       |       |       |     |      |      | D155 | D35   |

|       |       |       |     |      |      | D156 | D35   |

|       |       |       |     |      |      | D157 | D35   |

|       |       |       |     |      |      | D158 | D35   |

|       |       |       |     |      |      | D159 | D35   |

|       |       |       |     |      |      | D160 | D35   |

|       |       |       |     |      |      | D161 | D35   |

|       |       |       |     |      |      | D162 | D35   |

|       |       |       |     |      |      | D163 | D35   |

|       |       |       |     |      |      | D164 | D35   |

|       |       |       |     |      |      | D165 | D35   |

|       |       |       |     |      |      | D166 | D35   |

|       |       |       |     |      |      | D167 | D35   |

|       |       |       |     |      |      | D168 | D35   |

|       |       |       |     |      |      | D169 | D35   |

|       |       |       |     |      |      | D170 | D35   |

|       |       |       |     |      |      | D171 | D35   |

|       |       |       |     |      |      | D172 | D35   |

|       |       |       |     |      |      | D173 | D35   |

|       |       |       |     |      |      | D174 | D35   |

|       |       |       |     |      |      | D175 | D35   |

|       |       |       |     |      |      | D176 | D35   |

|       |       |       |     |      |      | D177 | D35   |

|       |       |       |     |      |      | D178 | D35   |

|       |       |       |     |      |      | D179 | D35   |

|       |       |       |     |      |      | D180 | D35   |

|       |       |       |     |      |      | D181 | D35   |

|       |       |       |     |      |      | D182 | D35   |

|       |       |       |     |      |      | D183 | D35   |

|       |       |       |     |      |      | D184 | D35   |

|       |       |       |     |      |      | D185 | D35   |

|       |       |       |     |      |      | D186 | D35   |

|       |       |       |     |      |      | D187 | D35   |

|       |       |       |     |      |      | D188 | D35   |

|       |       |       |     |      |      | D189 | D35   |

|       |       |       |     |      |      | D190 | D35   |

|       |       |       |     |      |      | D191 | D35   |

|       |       |       |     |      |      | D192 | D35   |

|       |       |       |     |      |      | D193 | D35   |

|       |       |       |     |      |      | D194 | D35   |

|       |       |       |     |      |      | D195 | D35   |

|       |       |       |     |      |      | D196 | D35   |

|       |       |       |     |      |      | D197 | D35   |

|       |       |       |     |      |      | D198 | D35   |

|       |       |       |     |      |      | D199 | D35   |

|       |       |       |     |      |      | D200 | D35   |

|       |       |       |     |      |      | D201 | D35   |

|       |       |       |     |      |      | D202 | D35   |

|       |       |       |     |      |      | D203 | D35   |

|       |       |       |     |      |      | D204 | D35   |

|       |       |       |     |      |      | D205 | D35   |

|       |       |       |     |      |      | D206 | D35   |

|       |       |       |     |      |      | D207 | D35   |

|       |       |       |     |      |      | D208 | D35   |

|       |       |       |     |      |      | D209 | D35   |

|       |       |       |     |      |      | D210 | D35   |

|       |       |       |     |      |      | D211 | D35   |

|       |       |       |     |      |      | D212 | D35   |

|       |       |       |     |      |      | D213 | D35   |

|       |       |       |     |      |      | D214 | D35   |

|       |       |       |     |      |      | D215 | D35   |

|       |       |       |     |      |      | D216 | D35   |

|       |       |       |     |      |      | D217 | D35   |

|       |       |       |     |      |      | D218 | D35   |

|       |       |       |     |      |      | D219 | D35   |

|       |       |       |     |      |      | D220 | D35   |

|       |       |       |     |      |      | D221 | D35   |

|       |       |       |     |      |      | D222 | D35   |

|       |       |       |     |      |      | D223 | D35   |

|       |       |       |     |      |      | D224 | D35   |

|       |       |       |     |      |      | D225 | D35   |

|       |       |       |     |      |      | D226 | D35   |

|       |       |       |     |      |      | D227 | D35   |

|       |       |       |     |      |      | D228 | D35   |

|       |       |       |     |      |      | D229 | D35   |

|       |       |       |     |      |      | D230 | D35   |

|       |       |       |     |      |      | D231 | D35   |

|       |       |       |     |      |      | D232 | D35   |

|       |       |       |     |      |      | D233 | D35   |

|       |       |       |     |      |      | D234 | D35   |

|       |       |       |     |      |      | D235 | D35   |

|       |       |       |     |      |      | D236 | D35   |

|       |       |       |     |      |      | D237 | D35   |

|       |       |       |     |      |      | D238 | D35   |

|       |       |       |     |      |      | D239 | D35   |

|       |       |       |     |      |      | D240 | D35   |

|       |       |       |     |      |      | D241 | D35   |

|       |       |       |     |      |      | D242 | D35   |

|       |       |       |     |      |      | D243 | D35   |

|       |       |       |     |      |      | D244 | D35   |

|       |       |       |     |      |      | D245 | D35   |

|       |       |       |     |      |      | D246 | D35   |

|       |       |       |     |      |      | D247 | D35   |

|       |       |       |     |      |      | D248 | D35   |

|       |       |       |     |      |      | D249 | D35   |

|       |       |       |     |      |      | D250 | D35   |

|       |       |       |     |      |      | D251 | D35   |

|       |       |       |     |      |      | D252 | D35   |

|       |       |       |     |      |      | D253 | D35   |

|       |       |       |     |      |      | D    |       |

14. Dê uma pausa (“Pause”) na execução e veja os valores das variáveis de tempo alto e baixo (use a aba “Expressions”). **Lembre que, como o clock do Timer 1 é de 1MHz, os valores calculados nas variáveis já estão em  $\mu$ s.** Compare com os valores medidos no analisador. Lembre que, da mesma forma que no OC, a latência do hardware é imperceptível. Os recursos de OC e IC permitem que os eventos sejam executados ou detectados sem atrasos de *software*.

|             | Valor calculado (PE11) | Valor medido (PA8) |

|-------------|------------------------|--------------------|

| Nível Alto  |                        |                    |

| Nível Baixo |                        |                    |

15. Neste projeto, configuramos a frequência-base do sistema para 96 MHz ao utilizar o modo Input Capture (IC). Mas será que isso afeta a resolução da captura? Se aumentarmos a frequência, conseguimos medir intervalos de tempo menores com mais exatidão? Ou existe um limite para essa relação? O que você acha? Se ainda não sabe a resposta, não se preocupe! Vamos explorar essa questão mais adiante e entender como a frequência impacta a precisão da captura.

## Projeto de PWM

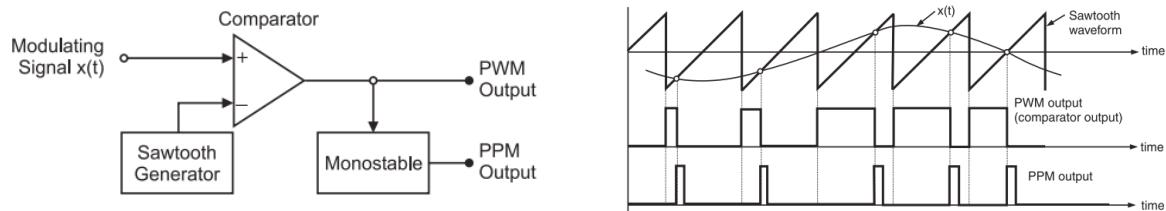

Controlar a potência entregue a uma carga é um desafio em sistemas eletrônicos e automotivos. Mas como fazer isso de forma eficiente, sem desperdiçar energia ou sobrecarregar componentes? Imagine tentar controlar a velocidade de um motor DC ajustando diretamente a tensão aplicada. Esse método pode ser ineficiente, gerar aquecimento excessivo e exigir circuitos complexos. Agora, e se houvesse uma solução que permitisse um controle preciso e flexível com mínima perda de energia?

Neste projeto, você descobrirá como a modulação por largura de pulso (em inglês, *Pulse Width Modulation* – PWM) simplifica esse controle. Vamos explorar como um temporizador dedicado pode gerar um sinal PWM para regular a velocidade de um motor DC de 5V. Ao final, você verá como o uso de um PWM “pronto” reduz significativamente a complexidade do sistema e melhora sua eficiência.

1. Crie um projeto novo usando o *Cube*, com o nome “PWM”, com a opção “**Initialize all peripherals with their default!**” desabilitada. Ative o módulo *Debug* como “Serial Wire”. Entre na aba “Clock Configuration” e modifique a frequência do *clock* do sistema para **96MHz**. Gere o código e abra o arquivo Core/Src/main.c. Comente (Remova) a declaração, a definição e a chamada da função `MX_GPIO_Init(void)`.

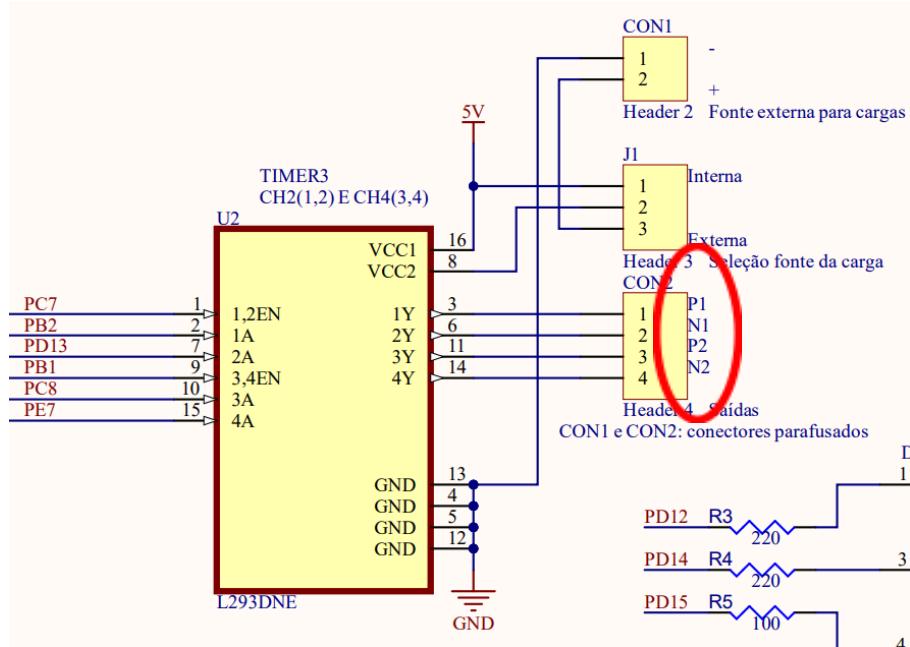

O projeto consiste em gerar um sinal PWM no canal TIM3\_CH2 para controlar a velocidade de um motor DC de 5 V, conectados nos pinos P1 e N1 mostrados no excerto do esquemático da [Placa de Expansão do NUCLEO](#).

2. Vamos configurar o *timer* e o canal a ser utilizado com a função `PWM_PInit`. Os parâmetros de configuração são o modo de operação PWM para o canal `TIM3_CH2`, divisor (*prescaler*) em 9600, contagem máxima do contador (*autoreload*) em 100. Para isso, incluimos o protótipo da função no escopo `/* USER CODE BEGIN PFP */`

```

e a sua definição no escopo /* USER CODE BEGIN 4 */

/**

* @brief: Inicializacao do PWM

*/

void PWM_PInit(void) {

// Habilitar o clock para o Timer 3

RCC->APB1LENR |= RCC_APB1LENR_TIM3EN_Msk;

```

```

TIM3->EGR |= TIM_EGR_UG_Msk;

while (TIM3->EGR & TIM_EGR_UG);

// Configurar PSC e ARR

TIM3->PSC = 9600-1; // Prescaler

TIM3->ARR = 100-1; // Período

TIM3->CCR2 = 0; // Duty cycle 0%

// Configuração do modo PWM

TIM3->CCMR1 &= ~ (TIM_CCMR1_CC2S_Msk); // Direcao do canal Output

TIM3->CCMR1 &= ~ (TIM_CCMR1_OC2M_Msk); // Modo PWM 1

TIM3->CCMR1 |= (TIM_CCMR1_OC2M_1 |

TIM_CCMR1_OC2M_2 |

TIM_CCMR1_OC2M_3); // Modo PWM 1 assimetrico

TIM3->CCMR1 |= TIM_CCMR1_OC2PE; // Habilita preload para o canal

2

TIM3->CCMR1 &= ~TIM_CCMR1_OC2FE; // Desabilita modo rapido

//Direcao de contagem

TIM3->CR1 &= ~TIM_CR1_DIR_Msk;

}

```

3. Para controlar o motor, utilizaremos uma Ponte-H, um circuito eletrônico que permite controlar a direção e a velocidade de motores DC. Nossa placa de expansão possui dois circuitos integrados com Pontes-H, e utilizaremos a Ponte-H número 1. O controle da velocidade do motor será feito através de um sinal PWM gerado no pino PC7 do microcontrolador. Este sinal modulará a potência aplicada ao motor, permitindo um controle preciso da velocidade. Além da velocidade, a direção do motor é controlada pela polaridade da tensão aplicada, que é definida por duas entradas digitais da Ponte-H. Para garantir o funcionamento correto, estas entradas devem estar sempre em estados lógicos opostos: uma em nível alto e a outra em nível baixo. Na Ponte-H 1, estas entradas estão conectadas aos pinos PB2 e PD13 do microcontrolador. Para configurar corretamente estes pinos, implementaremos a função `GPIO_PInit`. Esta função será responsável por inicializar os pinos PC7, PB2 e PD13 com as configurações necessárias para o controle da direção do motor. O protótipo desta função será inserido na área `/* USER CODE BEGIN PFP */` do arquivo `main.c`

```

void GPIO_PInit(void);

```

e a sua definição no escopo `/* USER CODE BEGIN 4 */`

```

/**

* @brief Inicializacao de PA7

*/

void GPIO_PInit(void) {

// Habilitar o clock para o GPIO

RCC->AHB4ENR |= (RCC_AHB4ENR_GPIOBEN |

RCC_AHB4ENR_GPIOCEN |

RCC_AHB4ENR_GPIODEN );

```

```

// Configurar o pino correspondente ao TIM3_CH2 (PC7)

GPIOC->MODER &= ~(GPIO_MODER_MODE7_Msk); // Limpar modos

GPIOC->MODER |= GPIO_MODER_MODE7_1; // Modo alternativo

// Selecionar a função alternativa para TIM3_CH2 (AF2)

GPIOC->AFR[0] &= ~(GPIO_AFRL_AFSEL7); // AF2 para PC7

GPIOC->AFR[0] |= (GPIO_AFRL_AFSEL7_1); // AF2 para PC7

// Configurar o pino correspondente a ponte H

GPIOB->MODER &= ~(GPIO_MODER_MODE2_Msk); // Limpar modos

GPIOB->MODER |= GPIO_MODER_MODE2_0; // GP Output

GPIOB->OTYPER &= ~GPIO_OTYPER_OT2_Msk; // Push-pull

GPIOD->MODER &= ~(GPIO_MODER_MODE13_Msk); // Limpar modos

GPIOD->MODER |= GPIO_MODER_MODE13_0; // GP Output

GPIOD->OTYPER &= ~GPIO_OTYPER_OT13_Msk; // Push-pull

}

```

Os pinos de controle da direção são configurados como GPIO do tipo de saída *push-pull*, enquanto os pinos de sinais PWM são multiplexados para o canal TIM3\_CH2, assumindo uma função alternativa.

4. Adicionamos ainda na função GPIO\_PInit a configuração do pino PC13 em que o botão azul da placa NUCLEO está conectado. É um pino de entrada no modo GPIO.

```

// Configurar o botão azul

// Configurar o pino correspondente a ponte H

GPIOC->MODER &= ~(GPIO_MODER_MODE13_Msk); // Limpar modos

```

5. Na área `/* USER CODE BEGIN PFP */`, vamos declarar o protótipo da função que vamos criar para iniciar a contagem no *timer*:

```

void Iniciar(void);

```

Inserimos a sua definição na área `/* USER CODE BEGIN 4 */`

```

void Iniciar(void) {

GPIOB->BSRR = GPIO_BSRR_BS2_Msk; // P1 da ponte H em nível alto

GPIOD->BSRR = GPIO_BSRR_BR13_Msk; // N1 da ponte em nível baixo

TIM3->CCER |= TIM_CCER_CC2E_Msk; // Habilitar saída do canal 2

// Habilitar o Timer

TIM3->CR1 |= TIM_CR1_CEN_Msk; // Iniciar o timer

}

```

6. Vamos também declarar as variáveis dentro do contexto da função main. Na área `/* USER CODE BEGIN 1 */`, inserimos

```

uint8_t increase_motor = 1; // 1 - cresce velocidade; 0 - reduz velocidade

uint8_t pwm_motor = 0; // Valor PWM para o motor

uint8_t dir_motor = 0; // Sentido de rotação

```

7. Agora vamos iniciar o *timer* e seu canal. Na área `/* USER CODE BEGIN 2 */`, chame a função de inicialização:

```

PWM_PInit();

GPIO_PInit();

Iniciar();

```

Inicialmente, colocamos o pino P1 da ponte (PB2) em nível alto, mantendo o pino N1 no nível baixo padrão na inicialização. Assim, o motor pode girar em um sentido, com velocidade dependente do ciclo de trabalho do PWM gerado pelo TIM3\_CH2.

8. No *loop* infinito vamos fazer um *polling* no botão azul da placa (PC13). A cada apertar do botão, o *Duty Cycle* do PWM do motor aumenta em 10%. Ao chegar a 100%, o DC passa a diminuir 10% a cada apertar do botão. Ao retornar a 0%, o sentido de rotação é invertido e volta-se a aumentar o DC em 10%. Após a linha `/* USER CODE BEGIN 3 */`, escreva o código:

```

while(!(GPIOC->IDR & GPIO_IDR_ID13));

if(increase_motor) {

pwm_motor += 10;

if(pwm_motor == 100) {

increase_motor = 0;

}

} else {

pwm_motor -= 10;

if(pwm_motor == 0) {

increase_motor = 1;

TIM3->CCR2 = 0;

if(dir_motor) {

dir_motor = 0;

GPIOB->BSRR = GPIO_BSRR_BS2; // P1 da ponte em

nível alto

GPIOD->BSRR = GPIO_BSRR_BR13; // N1 da ponte em

nível baixo

} else {

dir_motor = 1;

GPIOB->BSRR = GPIO_BSRR_BR2; // P1 da ponte em

nível baixo

GPIOD->BSRR = GPIO_BSRR_BS13; // N1 da ponte em

nível alto

}

}

}

TIM3->CCR2 = pwm_motor;

while(GPIOC->IDR & GPIO_IDR_ID13);

```

Note que a maior parte do código envolve o *polling* do botão e o cálculo do novo valor de DC, com a eventual mudança entre aumento ou redução do DC, além da mudança de sentido de rotação. O detalhe importante é que o novo valor de DC é guardado na variável “pwm\_motor”.

9. Realize o *Build*. Conecte o motor DC nos terminais “P1” e “N1” do conector CON2. Transfira o código executável para o microcontrolador e inicie a execução do programa. Pressione o botão azul várias vezes e veja o comportamento do motor.

10. Conecte o analisador lógico no pino PC7 do conector CN7 do NUCLEO (que corresponde ao PWM do motor). Veja a figura usada no projeto de *Input Capture*. Pressione o botão até uma velocidade intermediária no motor. Faça uma captura no analisador, registre o valor do TIM3\_CCR2 e meça o período total e o tempo em nível alto, calculando o *Duty Cycle*. Compare com os valores calculados em função dos parâmetros do *Timer* 3. Faça isto para 3 valores de *Duty Cycle*.

15. Faça uma pausa no programa e mude manualmente o valor no registrador TIM3\_CCR2 para que o *Duty Cycle* seja de 30% a mais e 30% a menos. Retorne a execução do programa e faça nova captura com o analisador lógico, verificando se o DC foi modificado corretamente. Há alguma relação entre o ciclo de trabalho e a velocidade do motor?

16. Modifique o *preescaler* do Timer 3 (TIM3->PSC) para obter um período PWM cinco vezes maior (defina TIM3->PSC para 48000, frequência em 20Hz) e cinco vezes menor (defina TIM3->PSC para 1920, frequência em 500z). Mantendo o ciclo de trabalho constante (mesma potência média), analise se há alguma relação entre a frequência do sinal PWM e o momento em que o motor começa a girar. Com base na teoria de funcionamento de motores DC, como você interpreta o comportamento observado?

17. Neste e nos dois projetos anteriores, tivemos oportunidade de configurar os canais dos temporizadores para 3 modos de operação mais aplicados, IC, OC e PWM. Mas você já parou para observar o padrão que se repete em todas essas configurações? Embora cada modo de operação tenha suas particularidades, a base da configuração permanece a mesma! Apenas a especificação do modo de operação se altera, como se estivéssemos trocando as lentes de uma câmera para capturar diferentes perspectivas do mesmo cenário. Nesta perspectiva, quais registradores permitem a distinção entre os modos IC, OC e PWM? Quais *bits* específicos são os responsáveis?

## Projeto de Relógio Externo

Em sistemas embarcados, a necessidade de contar eventos com precisão é uma demanda comum em diversas aplicações, como medição de fluxo em sensores industriais,

monitoramento de pulsos em encoders e controle de motores. No entanto, implementar essa contagem via *software* pode ser ineficiente, especialmente em sistemas que precisam responder rapidamente a outros eventos críticos. Uma solução é o uso de um contador de eventos externos dedicado, capaz de realizar a contagem automaticamente e com alta precisão, sem sobrecarregar o processador principal. Além de simplificar a implementação, esse método reduz a latência e melhora a confiabilidade do sistema, pois evita a necessidade de interrupções constantes ou *polling* intensivo. Alguns desses contadores são equipados de filtros, que ajudam a atenuar interferências e ruídos nos sinais de entrada, para garantir que as contagens permaneçam exatas mesmo na presença de interferências.

Neste projeto, implementaremos um contador de eventos externos usando o temporizador TIM1. O pino PE7 receberá um sinal digital externo. Esse pino é especificamente definido para a função de *trigger* de *clock* externo para o contador integrado ao TIM1, garantindo a contagem apenas de sinais válidos, ideal para aplicações industriais e científicas. Como realimentação visual do estado do contador, o LED verde (PB0) pisca a cada incremento do contador TIM1, o LED amarelo acende quando a contagem atinge 10 e apaga em 20, o LED vermelho acende em 20 e o contador é resetado. Se o botão azul for pressionado, apaga-se o LED vermelho e reinicia o ciclo de contagem.

1. Crie um projeto novo usando o *Cube*, com o nome “Contador\_Externo”, com a opção **“Initialize all peripherals with their default!” desabilitada**. Ative o módulo *Debug* como “Serial Wire”. Entre na aba “Clock Configuration” e modifique a frequência do *clock* do sistema para **96MHz**. Gere o código e abra o arquivo Core/Src/main.c. Comente (Remova) a declaração, a definição e a chamada da função `MX_GPIO_Init(void)`.

2. Vamos declarar as funções de configuração dos periféricos utilizado no projeto na área `/*`

```

USER CODE BEGIN PFP */

void GPIO_Perif_PInit (void);

void PE8_PInit (void);

void PE7_PInit (void);

void TIM1_PInit(void);

```

3. E vamos definir cada uma das funções na área `/* USER CODE BEGIN 4 */`. Em primeiro lugar, a seguinte função de configuração dos periféricos no NUCLEO para atuação e realimentação visual:

```

void GPIO_Perif_PInit (void) {

// LED verde

// Ativa GPIOB (PB0)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOBEN_Msk;

// PB0 como saída digital

GPIOB->MODER &= ~(GPIO_MODER_MODE0_Msk);

GPIOB->MODER |= GPIO_MODER_MODE0_0;

GPIOB->OTYPER &= ~GPIO_OTYPER_OT0_Msk; // PB0 como push-pull

// LED vermelho

// Ativa GPIOB (PB14)

// PB14 como saída digital

GPIOB->MODER &= ~(GPIO_MODER_MODE14_Msk);

```

```

GPIOB->MODER |= GPIO_MODER_MODE14_0;

GPIOB->OTYPER &= ~GPIO_OTYPER_OT14_Msk; // PB14 como push-pull

// LED amarelo

// Ativa GPIOE (PE1)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOEEN_Msk;

// PE1 como saida digital

GPIOE->MODER &= ~(GPIO_MODER_MODE1_Msk);

GPIOE->MODER |= GPIO_MODER_MODE1_0;

GPIOE->OTYPER &= ~GPIO_OTYPER_OT1_Msk; // PB0 como push-pull

// Botao azul

// Ativa GPIOC (PC13)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOCEN_Msk;

// PC13 como entrada digital

GPIOC->MODER &= ~(GPIO_MODER_MODE13_Msk);

// Configuracao de entrada

GPIOC->PUPDR &= ~(GPIO_PUPDR_PUPD13_Msk); //sem pull

}

```

4. Em seguida, a configuração do pino de entrada PE7 para a função alternativa de *External Trigger input* (ETR) do temporizador TIM1 ([AF1](#))

```

void PE7_PInit (void) {

// Ativa GPIOE (PE7)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOEEN_Msk;

// Configurar PE7 como função alternativa

GPIOE->MODER &= ~GPIO_MODER_MODE7_Msk;

GPIOE->MODER |= GPIO_MODER_MODE7_1;

// Selecionar AF1 para PE7 (TIM1_ETER)

GPIOE->AFR[0] &= ~(0xF << GPIO_AFRL_AFSEL7_Pos);

GPIOE->AFR[0] |= (1 << GPIO_AFRL_AFSEL7_Pos);

}

```

5. Precisamos agora criar um caminho físico para que o sinal gerado pelo botão azul no PC13 chegue ao pino PE7. Para isso, configuramos o pino PE8 com a função GPIO de saída, refletimos por *software* o sinal no pino PC13 no pino PE8 e conectamos o pino PE7 com o pino PE8 através do conector Zio CN10. Insira a seguinte função de configuração do pino PE8 depois da definição da função **PE7\_PInit (void)**

```

void PE8_PInit (void) {

// Ativa GPIOE (PE9)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOEEN_Msk;

// PE8 como saida digital

GPIOE->MODER &= ~(GPIO_MODER_MODE8_Msk);

GPIOE->MODER |= GPIO_MODER_MODE8_0;

GPIOE->OTYPER &= ~GPIO_OTYPER_OT8_Msk; // PE8 como push-pull

}

```

6. Vamos agora configurar o temporizador TIM1 para operar no [modo de relógio externo 2](#) (em inglês, *External Clock Mode 2*), ou seja, no modo em que a fonte externa do sinal de

relógio do contador vem de um pino dedicado ETR, seguindo o [procedimento recomendado](#) no Manual.

```

void TIM1_PInit(void) {

// Habilitar o clock para o Timer TIM1

RCC->APB2ENR |= RCC_APB2ENR_TIM1EN_Msk;

TIM1->EGR |= TIM_EGR_UG_Msk;    //Atualizacao inicial dos registradores

while (TIM1->EGR & TIM_EGR_UG);

// Configurar PSC e ARR

TIM1->CR1 &= ~TIM_CR1_ARPE_Msk; //Desabilita precarga de autoreload

TIM1->PSC = 0; // Prescaler

TIM1->ARR = 20-1; // Período

// Configurar a fonte de sinal externo (pag. 1443)

TIM1->SMCR |= TIM_SMCR_ECE; // Habilita o modo ETR externo (modo de relógio

externo 2)

TIM1->SMCR &= ~(TIM_SMCR_SMS_Msk); // Desabilita o modo escravo

TIM1->AF1 &= ~(TIM1_AF1_ETRSEL_Msk); // pinos I/O sao fonte de sinais externos

(PE7)

// Configurar o modo de contagem usando ETR2 (Fig. 338 e pag. 1443)

TIM1->SMCR &= ~(TIM_SMCR_ETF_Msk); // Sem filtro ETR2

TIM1->SMCR &= ~TIM_SMCR_ETPS_Msk; // Prescaler ETR2 (nenhum prescaler)

TIM1->SMCR |= TIM_SMCR_ETP; // Sensivel a borda de descida

// Habilitar interrupção TIM1 no NVIC

NVIC_SetPriority(TIM1_UP IRQn, 1); // Define a prioridade da interrupção

NVIC_EnableIRQ(TIM1_UP IRQn); // Habilita a interrupção TIM1_UP IRQn

TIM1->DIER |= TIM_DIER_UIE; // Habilitar geracao de interrupcao por evento de

atualizacao.

// Reiniciar o contador

TIM1->CNT = 0;

// Habilitar o Timer

TIM1->CR1 |= TIM_CR1_CEN; // Iniciar a contagem

}

```

Esta função configura o temporizador TIM1 como um contador de eventos externos. Para isso, habilita o *clock* do TIM1, desabilita a pré-carga do *autoreload* e define o *prescaler* como 0, resultando em um incremento do contador a cada evento externo. A contagem máxima (*autoreload*) é configurada para 20. O modo de relógio externo 2 é ativado sem filtro, e o contador é configurado para detectar bordas de descida no sinal de entrada. A interrupção de atualização, que ocorre quando o contador atinge o valor máximo, é habilitada com prioridade 1 no NVIC. Finalmente, o contador é reinicializado e a contagem é iniciada.

Consegue imaginar o que seria um modo de relógio externo 2? E um modo 1? Provavelmente não. Mas não se preocupe, exploraremos isso em detalhes mais adiante.

7. Inserimos as chamadas dessas funções na área `/* USER CODE BEGIN 2 */` da função main para inicialização dos periféricos

```

GPIO_Perif_PInit ();

PE8_PInit ();

```

```

PE7_PInit ();

TIM1_PInit();

```

6. No laço infinito de `main`, realizamos o *polling* do botão azul (PC13). Se o botão estiver pressionado, é gerado um pulso no pino PB0 onde o LED verde está conectado e no pino PE8 que será ligado ao pino PE7. Além disso é verificado o valor do contador para controlar o estado do LED amarelo. Abaixo da linha `/* USER CODE BEGIN 3 */`, insira o seguinte bloco de código:

```

uint16_t i;

if(GPIOC->IDR & GPIO_IDR_ID13_Msk) { // Botao pressionado

if (TIM1->CNT < 19 && (GPIOB->IDR & GPIO_IDR_ID14)) {

GPIOB->BSRR = GPIO_BSRR_BR14; // Apaga LD3 (vermelho)

}

GPIOE->BSRR = GPIO_BSRR_BS8; // PULSO em nivel alto

GPIOB->BSRR = GPIO_BSRR_BS0; // LD1 aceso

for (i=0; i<5000;i++); // mantem LD1 aceso por um intervalo de tempo

GPIOE->BSRR = GPIO_BSRR_BR8; // PULSO em nivel baixo

GPIOB->BSRR = GPIO_BSRR_BR0; // LD1 apagado

while(GPIOC->IDR & GPIO_IDR_ID13); // Espera soltar botao

}

if (TIM1->CNT > 9 && !(GPIOE->IDR & GPIO_IDR_ID1)) { // Chegou a 10

GPIOE->BSRR = GPIO_BSRR_BS1; // Acende LD2 (amarelo)

} else if (TIM1->CNT <= 9 && (GPIOE->IDR & GPIO_IDR_ID1)){

GPIOE->BSRR = GPIO_BSRR_BR1; // Apaga LD2

}

```

Dentro do bloco de código, observe instruções adicionais que controlam o estado do LED vermelho. Essas instruções garantem que o LED vermelho permaneça aceso após o ciclo de contagem de 20 eventos ser concluído. O LED só será apagado e um novo ciclo de contagem iniciado quando o botão azul for pressionado.

7. Agora vamos implementar a ISR do evento de interrupção *Update*. Abra o arquivo “stm32h7xx\_it.c” e localize área `/* USER CODE BEGIN 1 */`. Insira a rotina de serviço:

```

void TIM1_UP_IRQHandler (void) {

if(TIM1->SR & TIM_SR UIF) { // Update Interrupt

TIM1->SR &= ~TIM_SR UIF; // Limpa flag

GPIOB->BSRR = GPIO_BSRR_BS14; // Acende LED vermelho

}

}

```

Além de limpar a *flag*, é aceso o LED vermelho.

8. Interligue com um fio os pinos PE7 e PE8, correspondentes aos pinos 18 e 20 do conector CN10, para que os pulsos gerados pelo botão azul sejam usados como *triggers* externos do temporizador TIM1. Veja a figura no projeto de *Input Capture*.

9. Realize o *Build* e transfira o código para o microcontrolador. Execute o código. Aperte o botão algumas vezes e veja o LED verde acender a cada aperto. Quando o número de apertos chegar a 10, o LED amarelo acenderá. Continue a apertar o botão, em um total de 19 vezes. Quando chegar a 20, o LED vermelho acenderá. O que acontece se pressionarmos mais uma vez o botão azul?

10. Termine e reinicie a execução do programa. Faça uma pausa (“Pause”) após três pressionamentos do botão e verifique o valor do registrador TIM1\_CNT. Retome a execução (“Resume”) e pressione o botão mais uma vez. Faça uma nova pausa (“Pause”) e verifique novamente o valor no registrador TIM1\_CNT. Continue a execução (“Resume”) e continue pressionando o botão até que o LED amarelo acenda. Faça uma nova pausa (“Pause”) e verifique novamente o valor no registrador TIM1\_CNT. Continue a execução (“Resume”) e continue pressionando o botão até que o LED vermelho acenda. vermelho seja acionado. Após acionar o LED vermelho, faça uma pausa (“Pause”) e leia o valor do TIM1\_CNT.

|                                                    | Quantidade de apertos | Valor no TIM1_CNT |

|----------------------------------------------------|-----------------------|-------------------|

| Primeira pausa                                     |                       |                   |

| Segunda pausa                                      |                       |                   |

| LED amarelo muda de estado<br>(apagado para aceso) |                       |                   |

| Depois do LED vermelho acender                     |                       |                   |

Após o LED vermelho acender, observe atentamente o valor do registrador TIM1\_CNT. O que você nota? Tente desvendar a relação entre cada pressionamento do botão e os valores armazenados no registrador. Se o funcionamento desse mecanismo ainda não for claro para você, não se preocupe! Vamos dissecar o circuito responsável pelo comportamento observado mais adiante.

## FUNDAMENTOS TEÓRICOS

No Roteiro 5, exploramos temporizadores especializados, como RTC e *Watchdog*, e temporizadores de uso geral para tarefas básicas de temporização. Neste roteiro, introduziremos os **temporizadores avançados**, projetados para aplicações que demandam maior precisão e flexibilidade. Para aumentar a **precisão**, os temporizadores avançados podem integrar desmembrar registradores de módulo (auto-recarga) em registradores sombra

e pré-carga. Além da precisão, os temporizadores avançados oferecem maior **flexibilidade** em diversas áreas:

- modos de operação avançados: Permitem gerar sinais complexos e realizar tarefas de controle precisas.

- controle de saída flexível: Permitem configurar as saídas para gerar sinais com diferentes formas de onda, frequências e larguras de pulso, sincronizando-as com eventos externos.

- sincronização e interconexão: Podem ser sincronizados com outros temporizadores ou eventos externos, e interconectados com periféricos como ADCs e DMAs, para realizar tarefas de controle e aquisição de dados de forma eficiente.

Atualmente, temporizadores avançados são componentes cruciais em sistemas eletrônicos que demandam alta segurança e confiabilidade operacional. Para tanto, alguns incorporam circuitos de *break*, que monitoram continuamente o sistema em busca de falhas, e circuitos geradores de *dead-time*, que previnem a sobreposição de atividade em componentes de operação mutuamente exclusiva. Isso os torna cada vez mais apropriados para serem aplicados no **controle de sistemas de alta potência**, pois permitem o controle preciso de comutação, reduzem a necessidade de componentes externos e aumentam a vida útil dos componentes de potência.

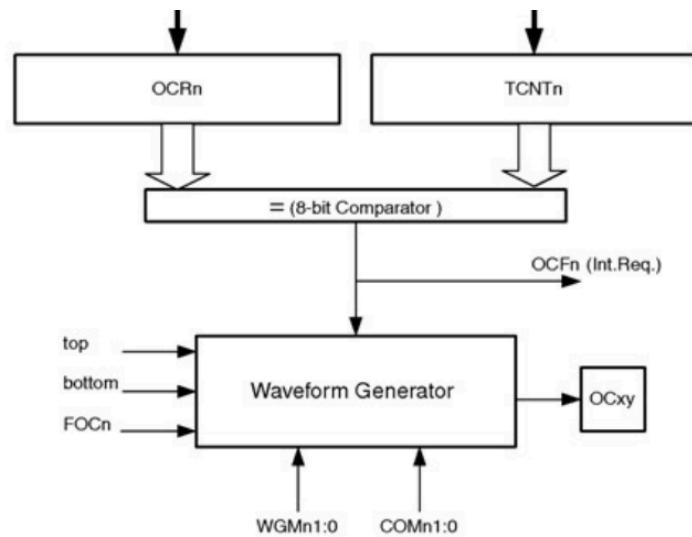

Temporizadores avançados se destacam pela capacidade de interagir com o mundo físico através de múltiplos canais de entrada e saída, característica essencial para sistemas de controle complexos e precisos, como os utilizados em controle de motores e aplicações industriais. Os canais de entrada permitem capturar eventos externos, como pulsos de sensores, através da funcionalidade de **captura de entrada** (em inglês, *input capture* – IC), que registra o valor do contador no momento exato do evento. Já os canais de saída permitem gerar sinais de controle para dispositivos externos, como motores, LEDs e relés. A **comparação de saída** (em inglês, *output compare* – OC) compara o valor do contador com um valor predefinido, executando ações específicas quando há coincidência, enquanto a **modulação por largura de pulso** (em inglês, *pulse width modulation* – PWM) ajusta a potência fornecida aos dispositivos através da variação da largura do pulso.

É importante notar que, apesar de funcionarem de forma independente, todos os canais compartilham o **mesmo contador**, portanto sujeitos à **mesma frequência de clock** e **ao mesmo módulo de contagem**. Isso garante sincronia e precisão nas operações temporais. Como interagem com o ambiente externo, a configuração dos pinos é essencial para que os canais capturem eventos ou enviem sinais.

## PRELIMINARES

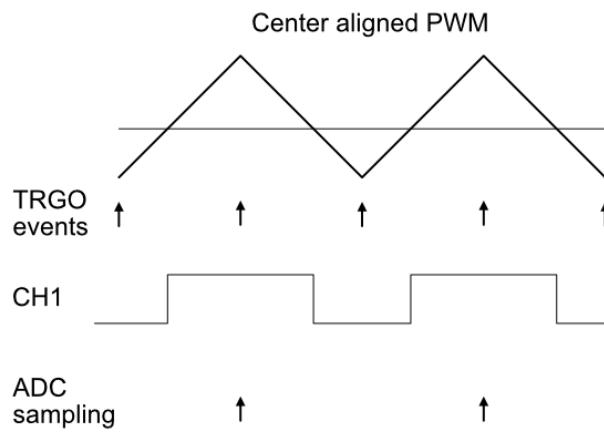

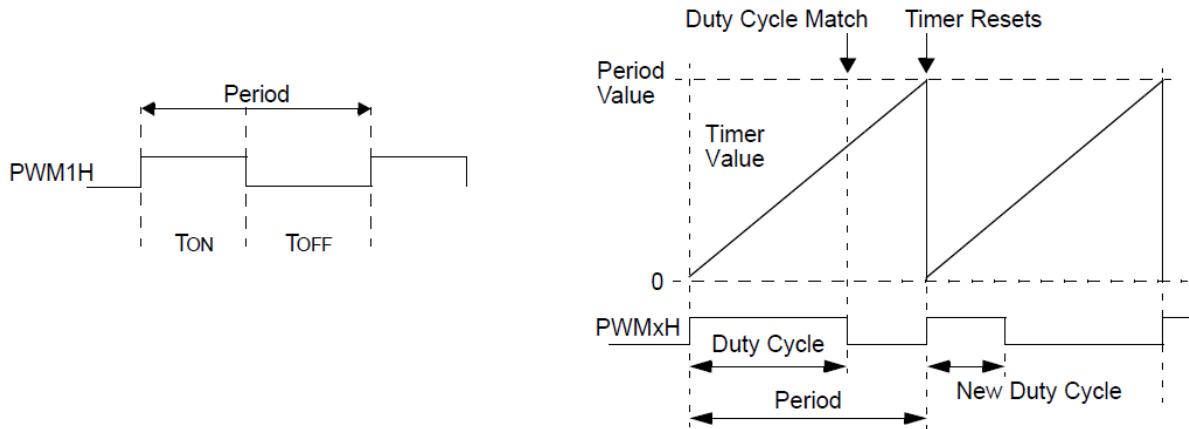

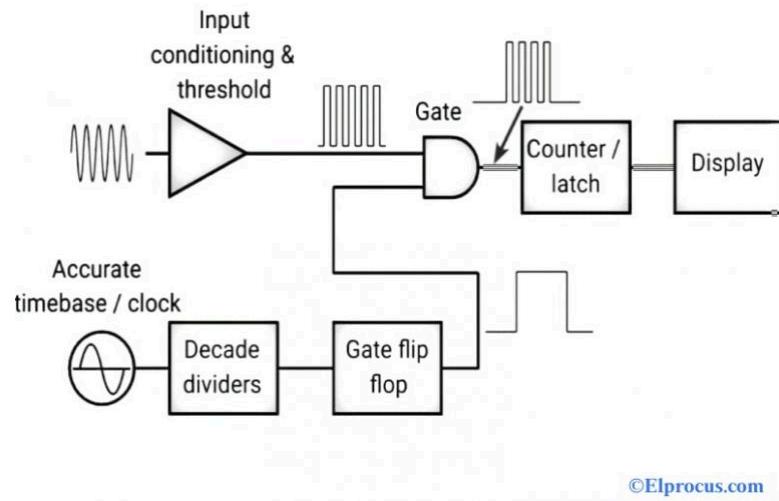

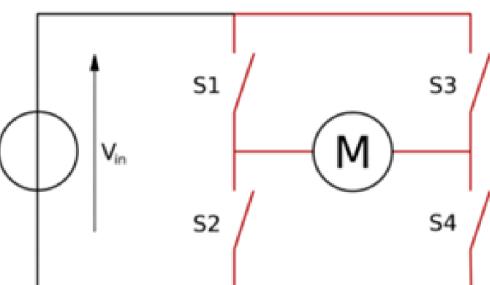

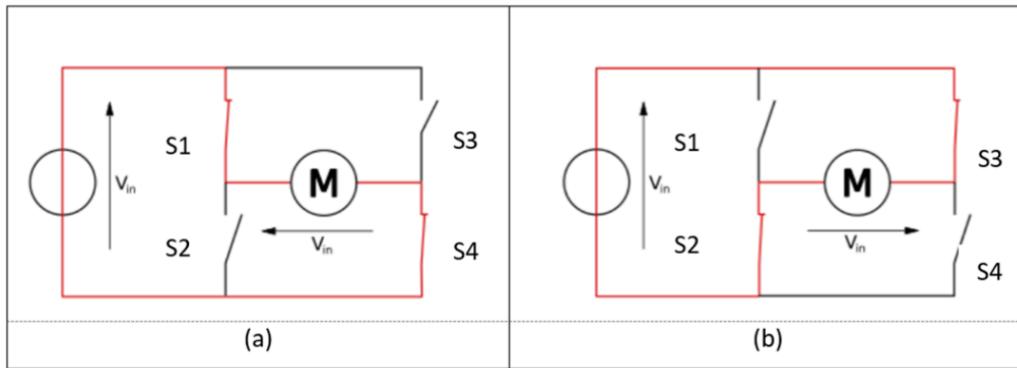

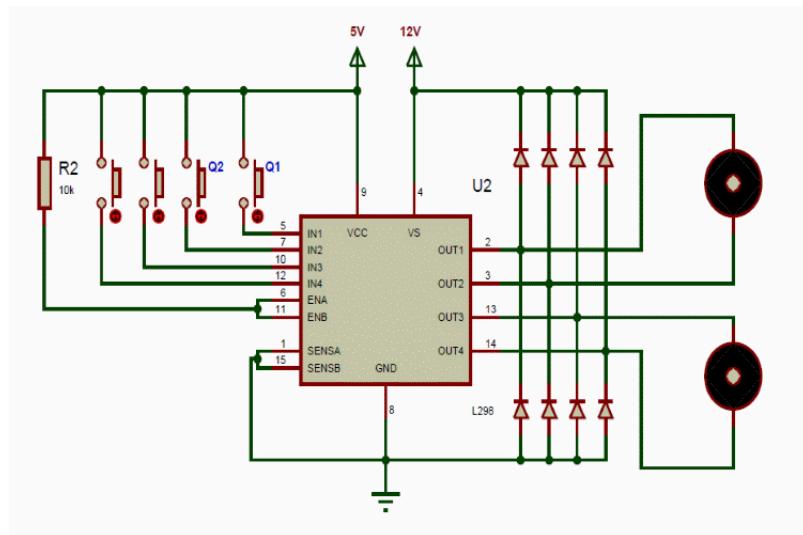

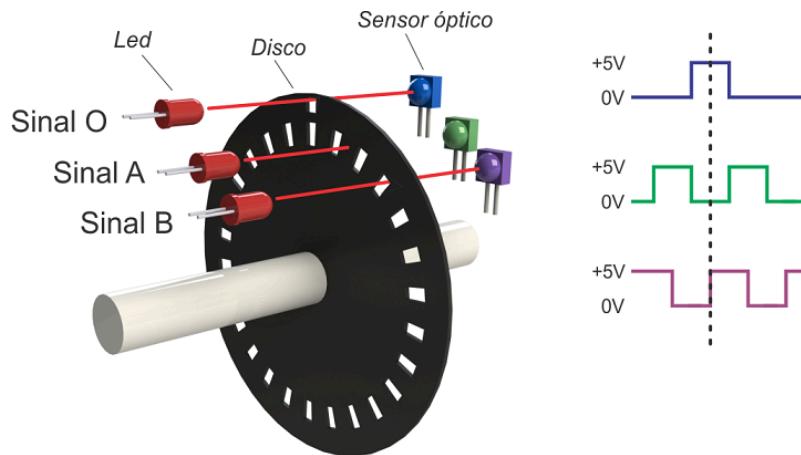

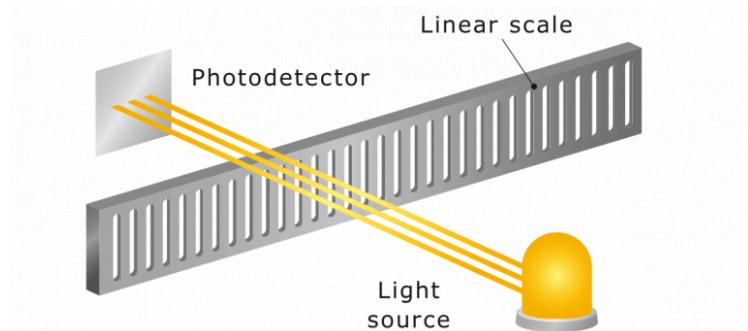

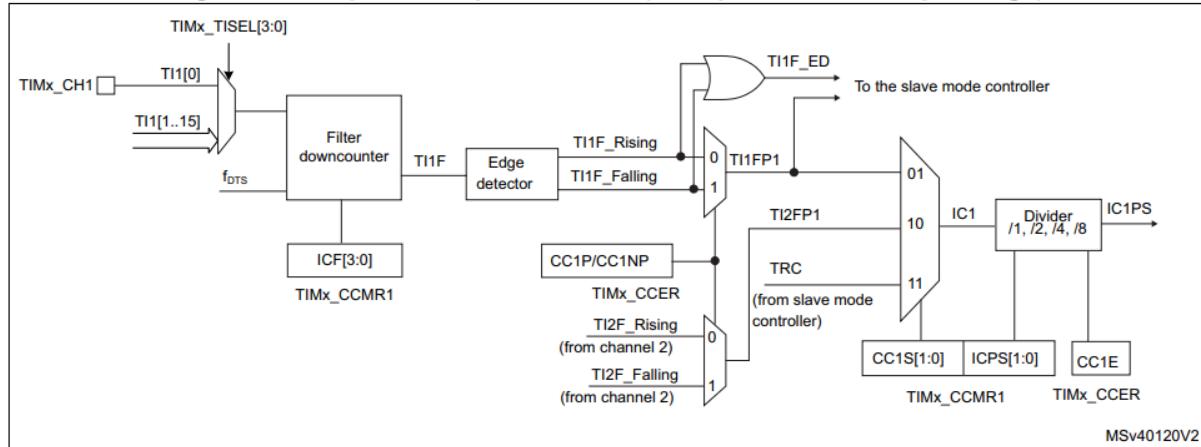

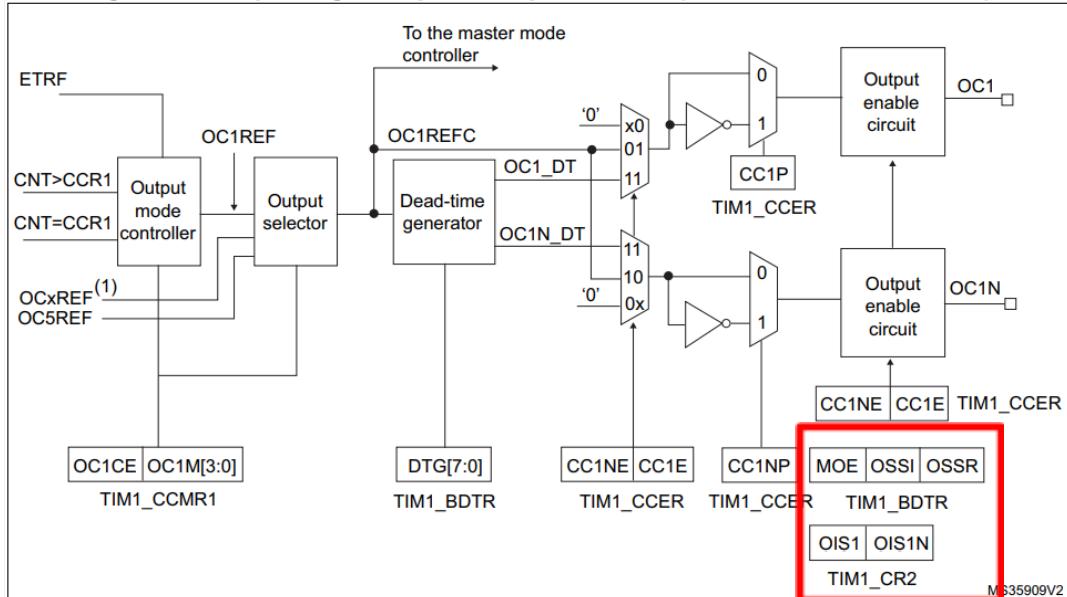

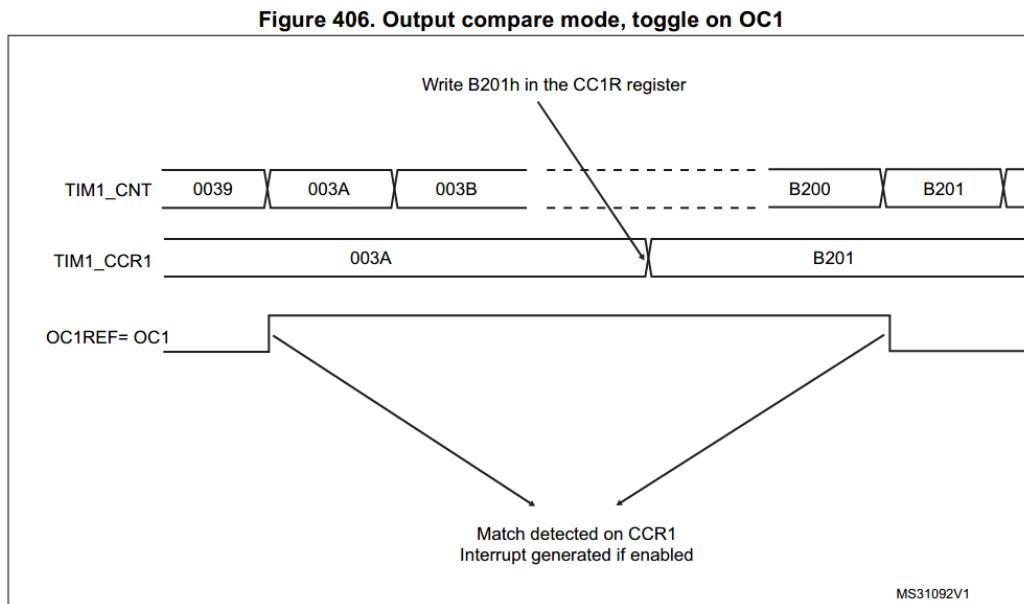

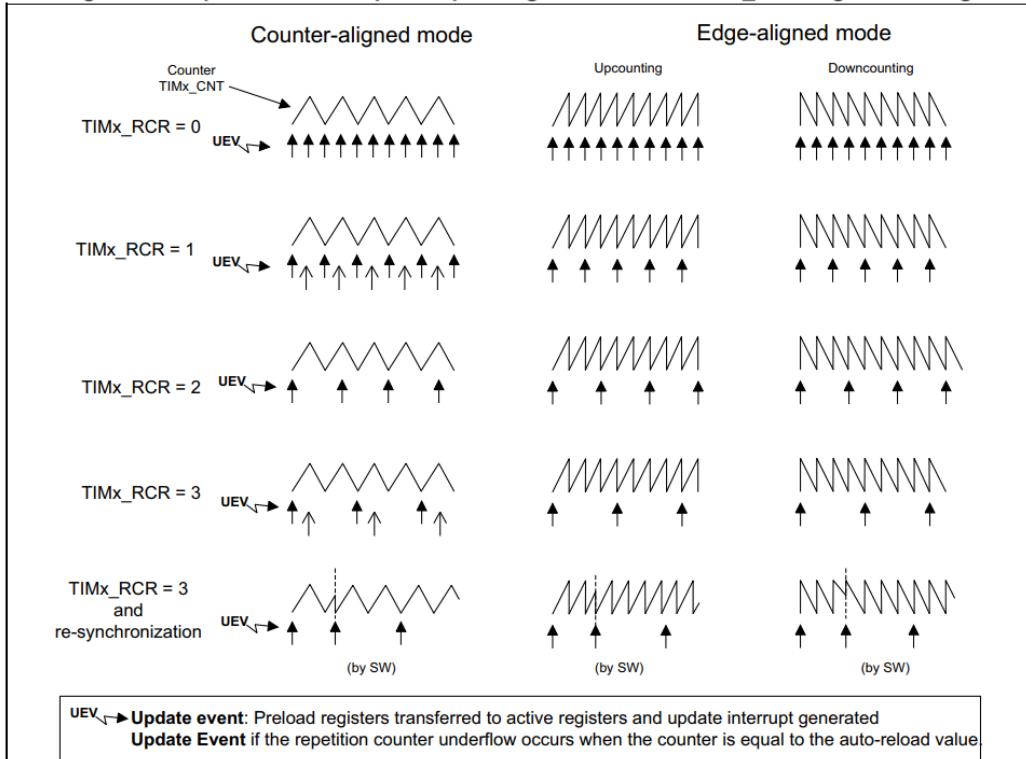

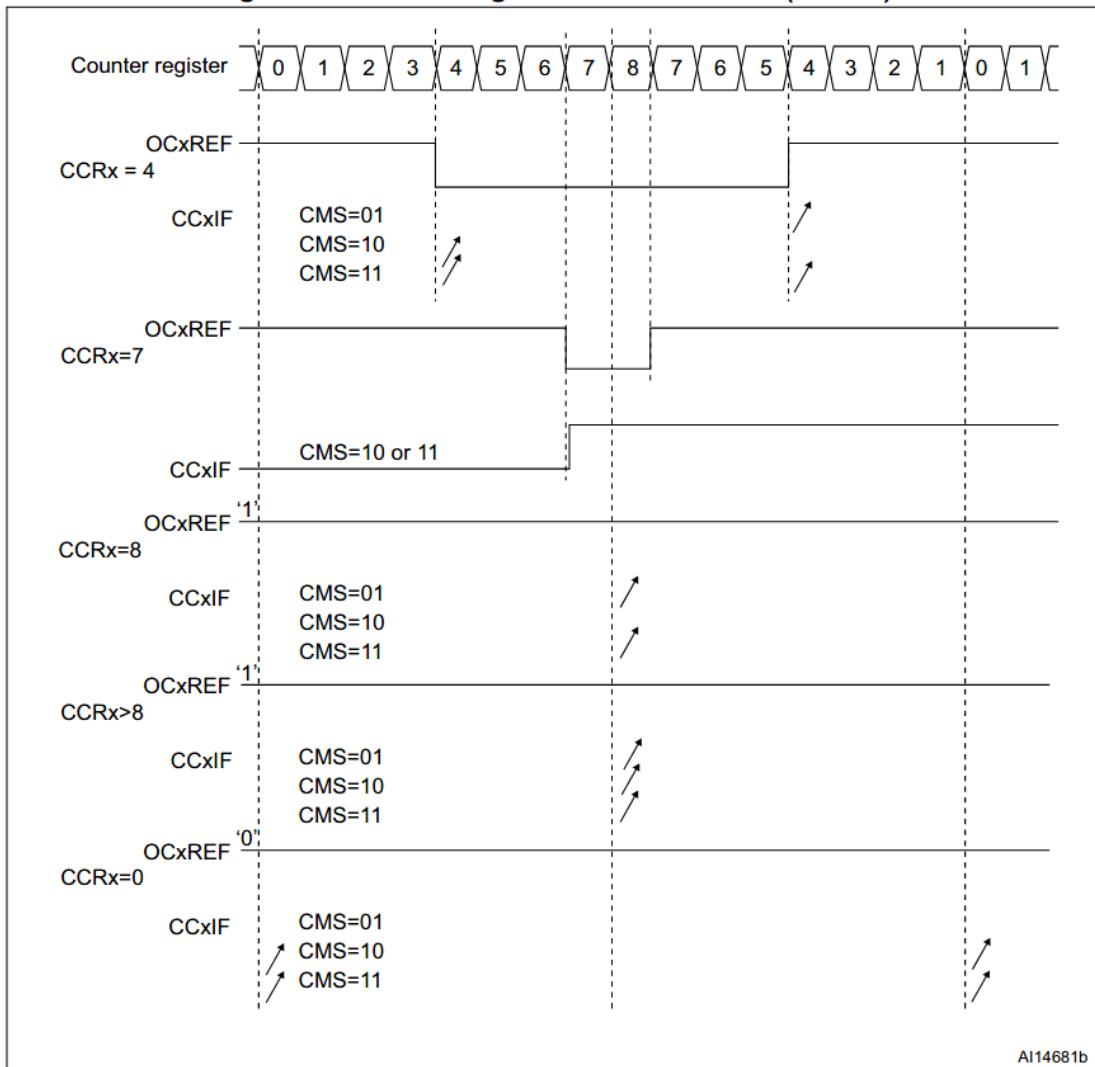

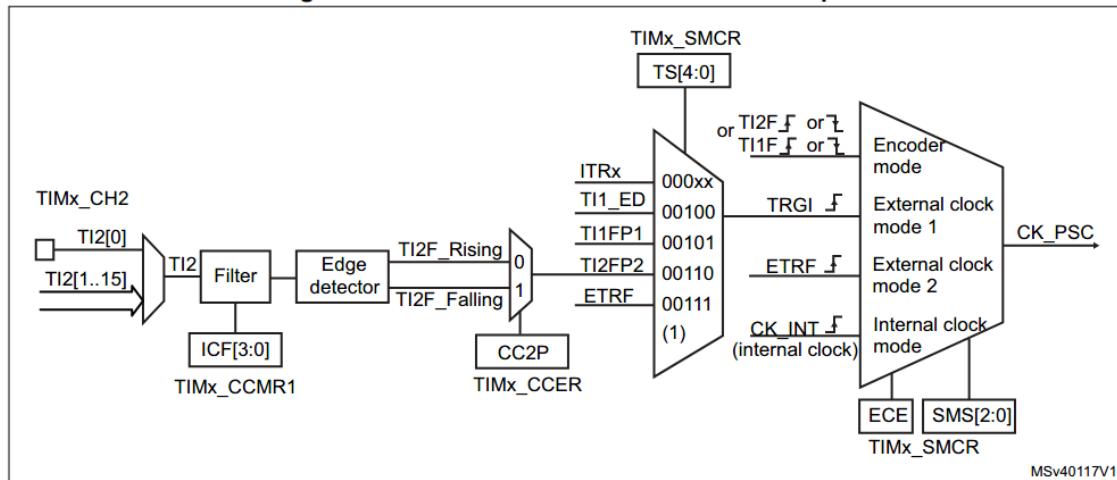

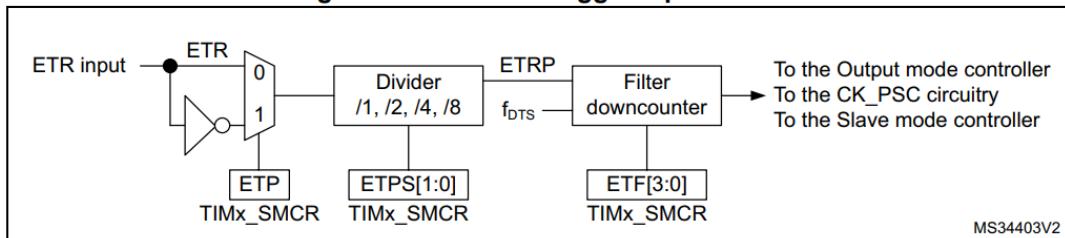

Os temporizadores avançados são componentes essenciais em sistemas eletrônicos que exigem controle preciso do tempo. Além das funções básicas de contagem e geração de sinais, eles podem incorporar recursos adicionais que aumentam a segurança e a flexibilidade do sistema. Os temporizadores avançados envolvem conceitos que aumentam a flexibilidade e a precisão do controle sobre o tempo, permitindo a sincronização de eventos e a geração de sinais com alta precisão.