# **DISCIPLINA EA701**

## **Introdução aos Sistemas Embarcados**

### **ROTEIRO 9: Entradas/Saídas Analógicas**

**Domínios Analógicos e Digitais, Conversores DAC e ADC, Interface Analógica em Microcontroladores, DMA (DMAC, DMAMUX e *Buffer Circular*), Sensores Analógicos (Sensor de Temperatura LM61, Potenciômetro, *Joystick*), Atuador Analógico (Disco Piezoelétrico)**

**Profs. Antonio A. F. Quevedo e Wu Shin-Ting**

**FEEC / UNICAMP**

**Revisado e modificado em abril de 2025 por Ting com auxílio do Chatgpt**

**Revisado em outubro de 2024**

This work is licensed under Creative Commons Attribution-NonCommercial-ShareAlike 4.0 International. To view a copy of this license, visit <https://creativecommons.org/licenses/by-nc-sa/4.0/>

|                                                                                           |            |

|-------------------------------------------------------------------------------------------|------------|

| <b>INTRODUÇÃO</b>                                                                         | <b>3</b>   |

| <b>PROJETOS-EXEMPLO</b>                                                                   | <b>4</b>   |

| Projeto de conversão D/A básica                                                           | 4          |

| Projeto de conversão A/D básica                                                           | 10         |

| Projeto de conversor A/D disparado por hardware e geração de evento de “fim de conversão” | 14         |

| Projeto de conversão DAC com DMA                                                          | 22         |

| Projeto de conversor A/D disparado por hardware, com DMA                                  | 26         |

| <b>FUNDAMENTOS TEÓRICOS</b>                                                               | <b>33</b>  |

| QUANTIDADE ANALÓGICA E QUANTIDADE DIGITAL                                                 | 34         |

| COEXISTÊNCIA DE DOMÍNIOS ANALÓGICOS E DIGITAIS                                            | 37         |

| INTEGRAÇÃO DE DOMÍNIOS ANALÓGICOS E DIGITAIS                                              | 40         |

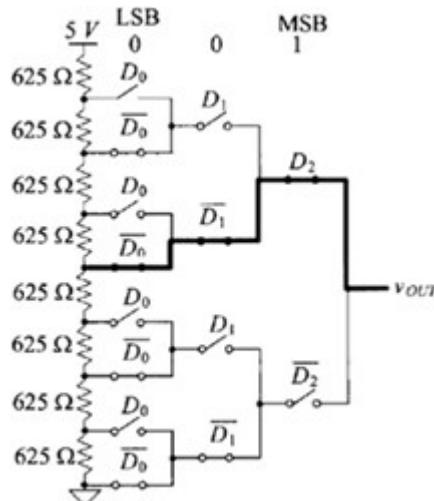

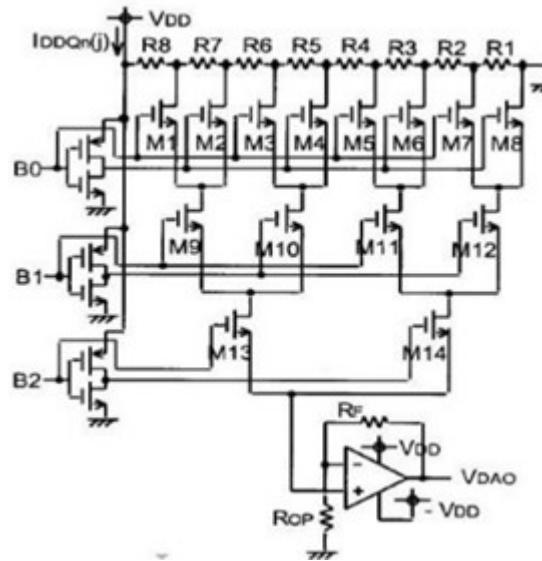

| ARQUITETURAS DE CONVERSORES DIGITAL-ANALÓGICOS                                            | 42         |

| Resistor String DAC                                                                       | 43         |

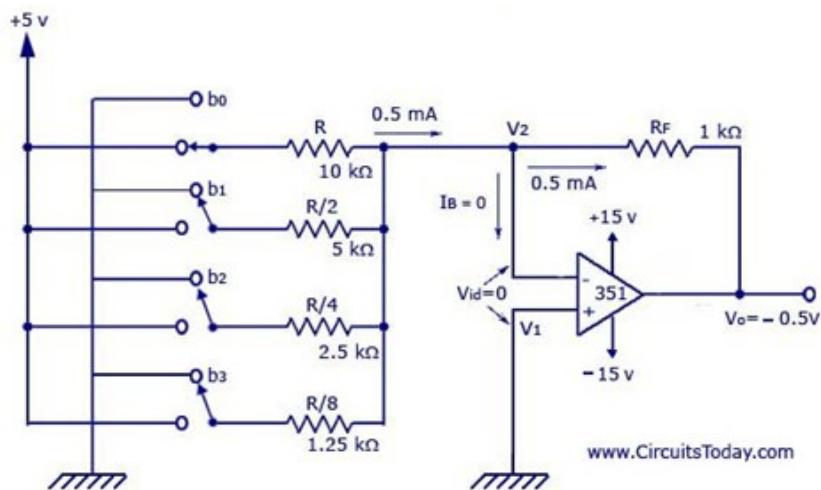

| Círculo DAC com resistores ponderados                                                     | 45         |

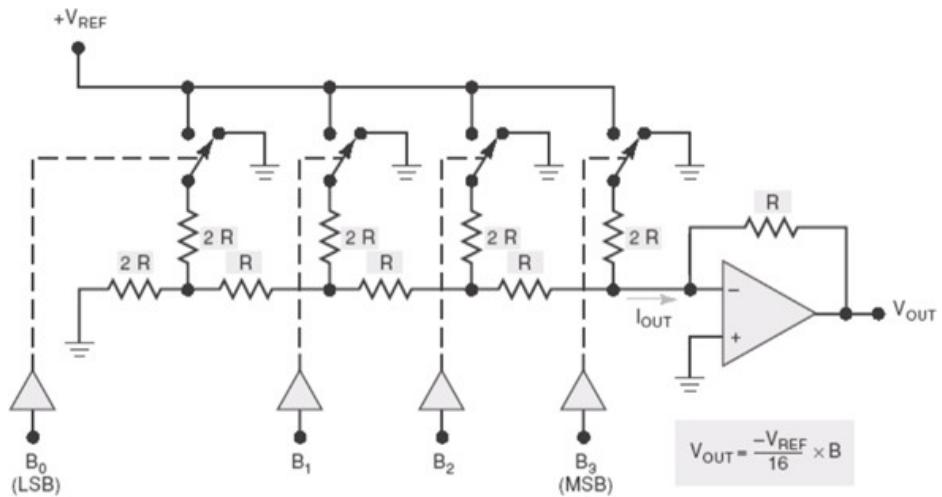

| Círculo DAC com rede resistiva R/2R                                                       | 47         |

| ARQUITETURAS DE CONVERSORES ANALÓGICO-DIGITAIS                                            | 49         |

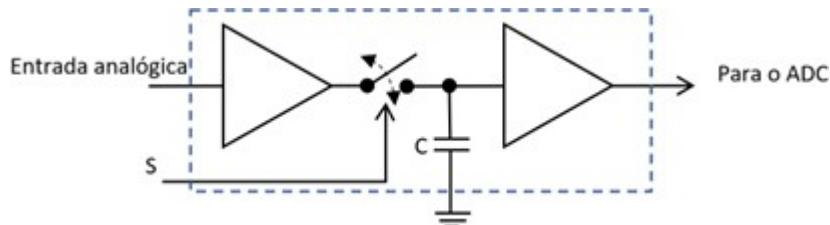

| Círculo de amostragem-e-retenção (sample-and-hold)                                        | 50         |

| Conversão de códigos binários para valores em unidades físicas                            | 50         |

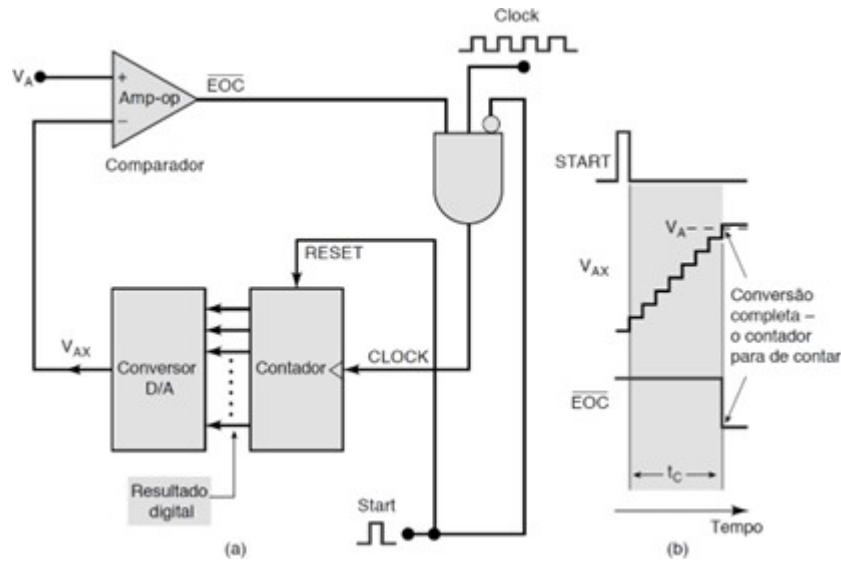

| ADC de rampa digital (contador-rampa)                                                     | 51         |

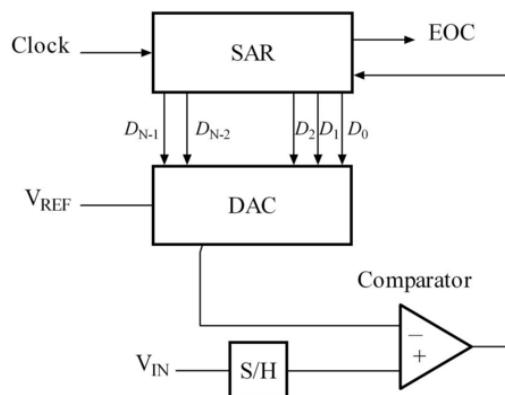

| ADC com registrador de aproximações sucessivas                                            | 53         |

| Aprimoramento das tecnologias de ADC                                                      | 54         |

| Outros tipos de ADC                                                                       | 55         |

| ESPECIFICAÇÕES E MÉTRICAS DE DESEMPENHO                                                   | 56         |

| ARQUITETURA DE INTERFACE ANALÓGICA EM MICROCONTROLADORES                                  | 59         |

| <b>ACESSO DIRETO À MEMÓRIA</b>                                                            | <b>61</b>  |

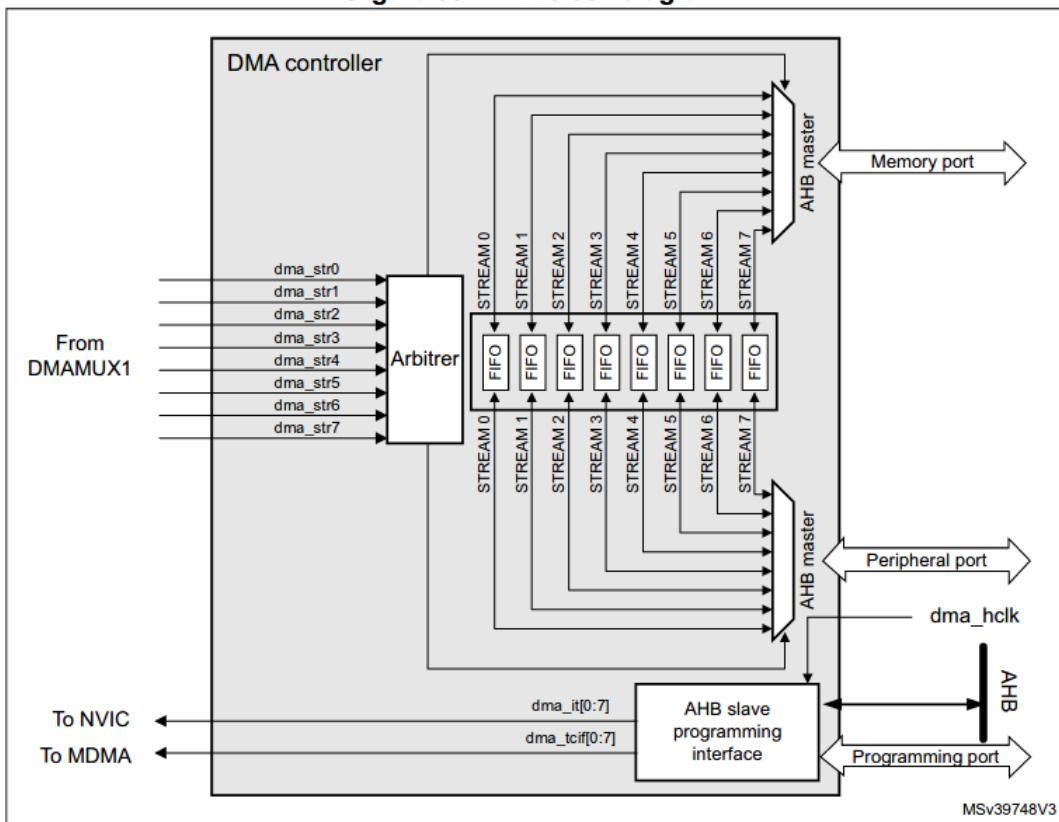

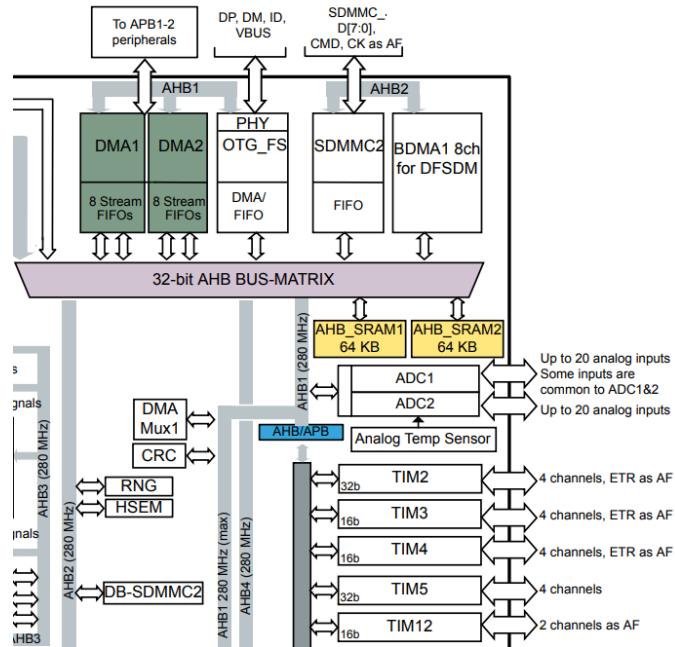

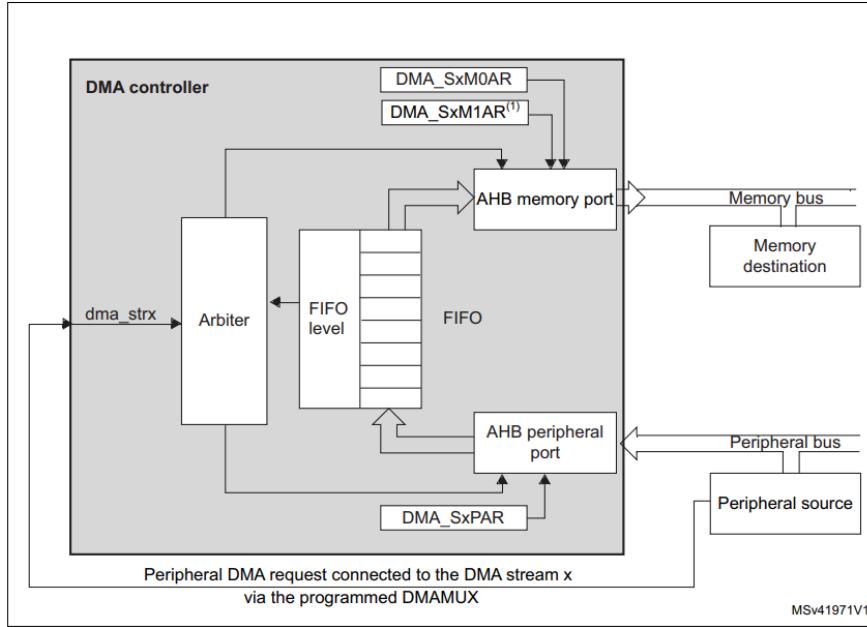

| Controlador de Acesso Direto à Memória                                                    | 63         |

| Modos de operação do DMAC                                                                 | 65         |

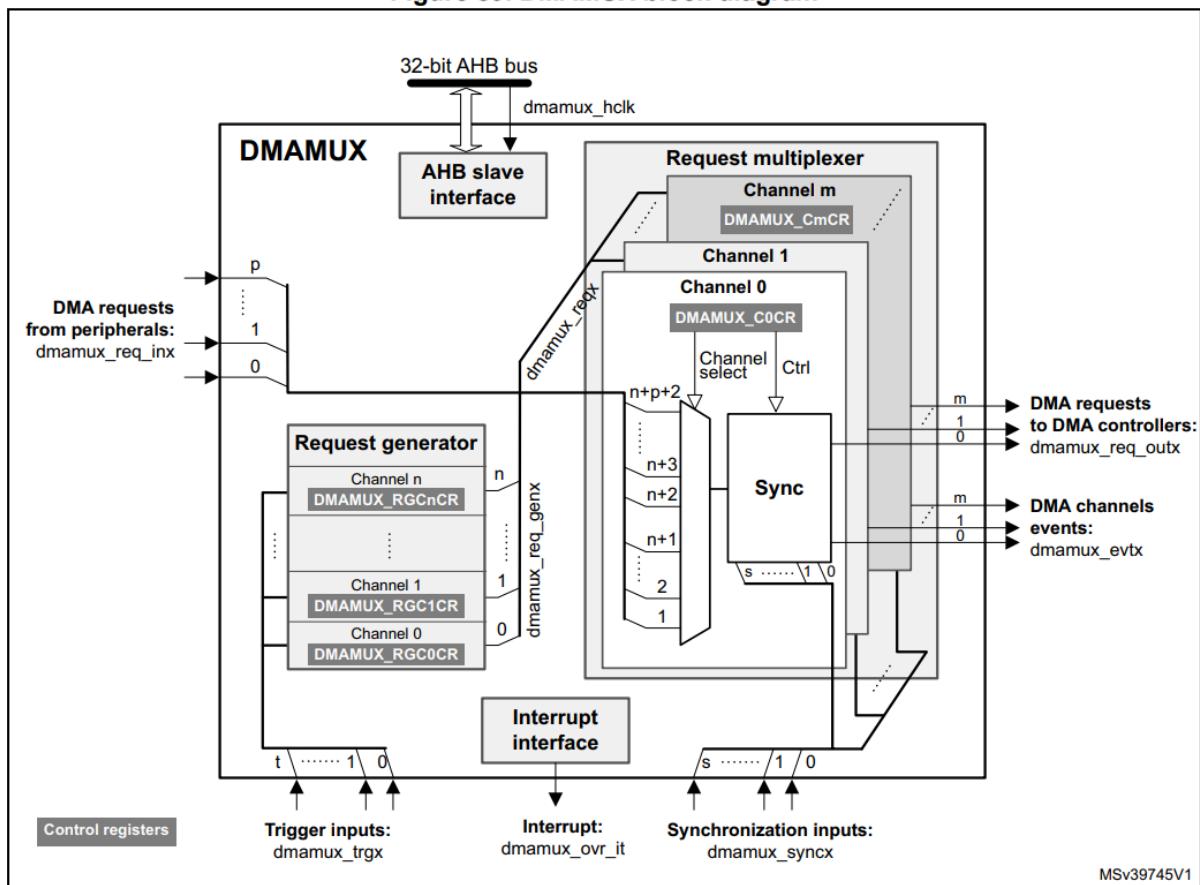

| Roteador de requisições de DMA                                                            | 67         |

| Estrutura de dados: buffer circular                                                       | 68         |

| Coerência de cache                                                                        | 70         |

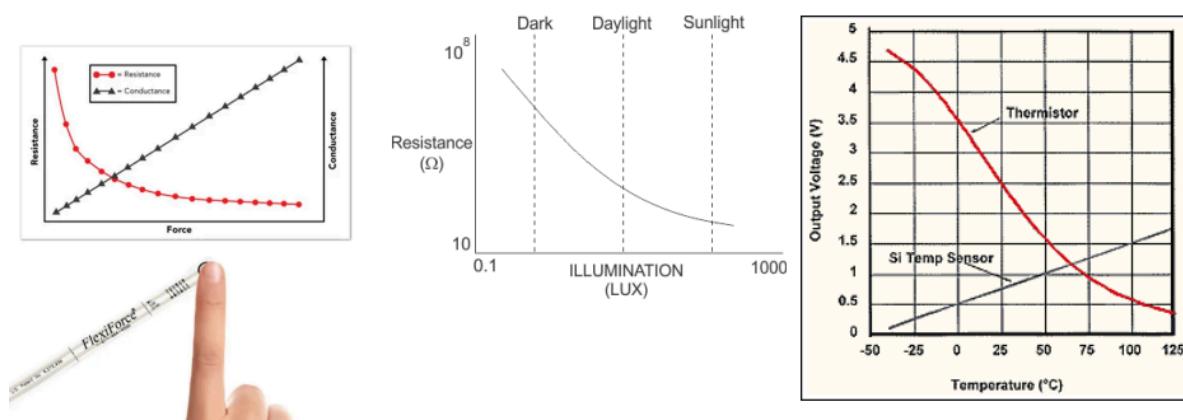

| <b>SENSORES ANALÓGICOS</b>                                                                | <b>71</b>  |

| Joystick Analógico                                                                        | 72         |

| Potenciômetro                                                                             | 73         |

| Sensor de Temperatura Integrado LM61                                                      | 74         |

| <b>ATUADORES ANALÓGICOS</b>                                                               | <b>75</b>  |

| Disco Piezoelétrico                                                                       | 76         |

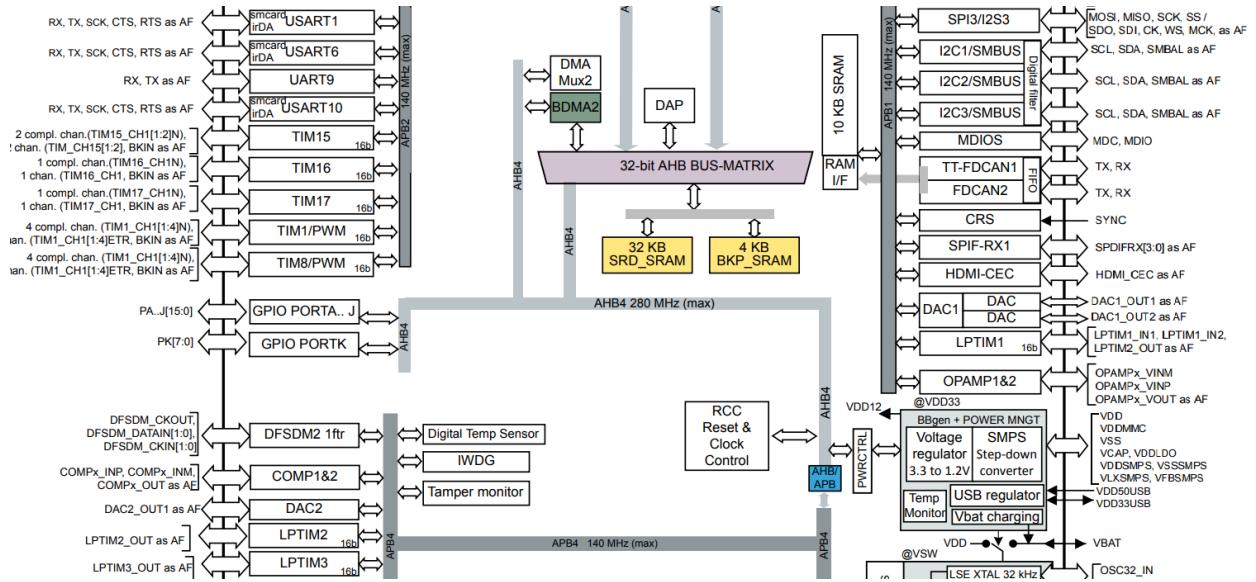

| <b>STM32H7A3</b>                                                                          | <b>77</b>  |

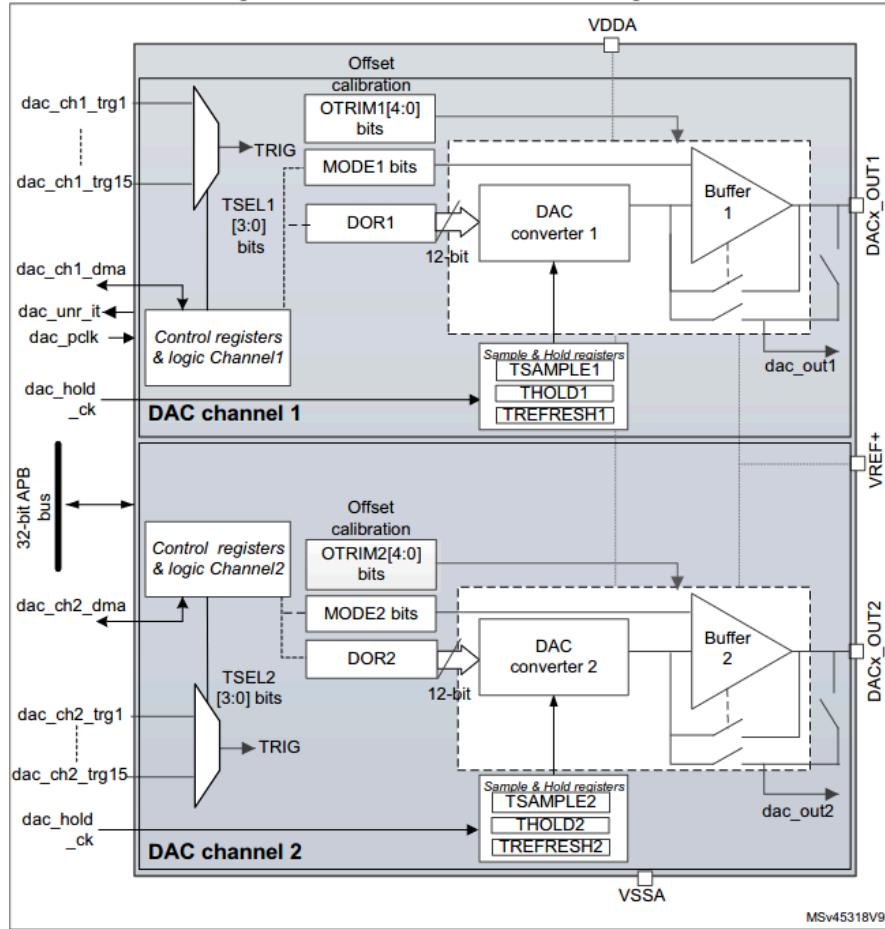

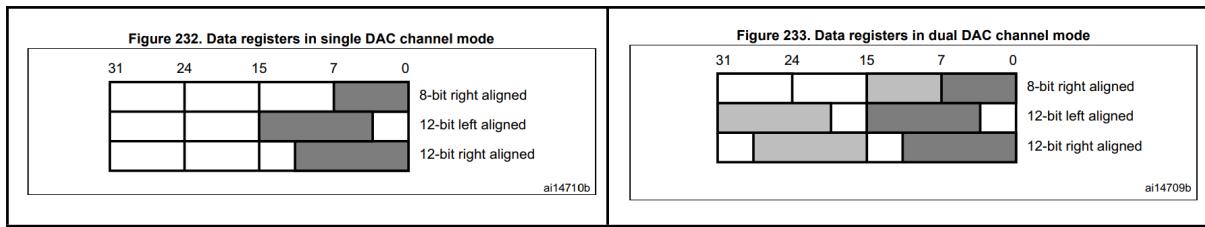

| DAC                                                                                       | 77         |

| ADC                                                                                       | 84         |

| DMA                                                                                       | 92         |

| DMAMUX                                                                                    | 97         |

| <b>PROGRAMAÇÃO EM C: VALOR DECIMAL EM VETOR DE CARACTERES ASCII</b>                       | <b>102</b> |

# INTRODUÇÃO

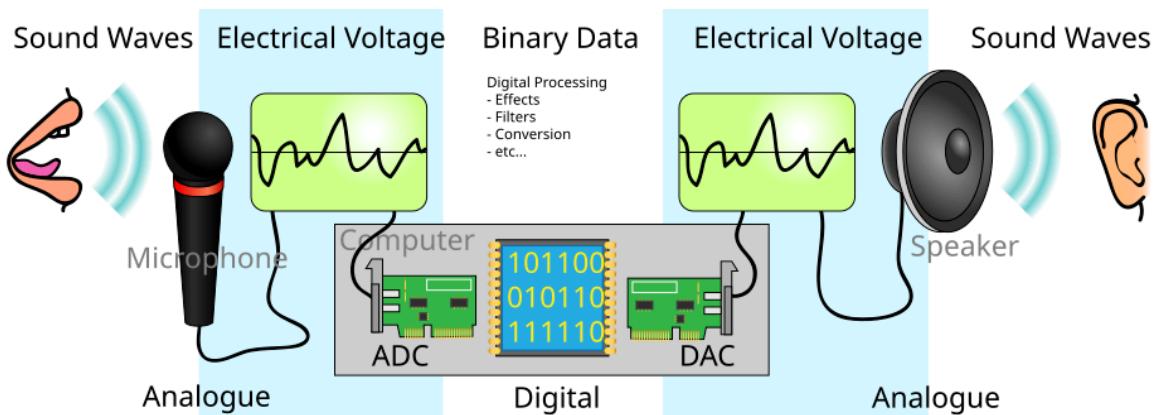

O mundo elétrico pode ser entendido de duas formas principais: analógica e digital. O mundo digital representa grandezas físicas com valores discretos (códigos binários), interpretados por computadores. Já o mundo analógico lida com grandezas contínuas (tensão, corrente, temperatura, som), que variam suavemente. A manipulação de sinais é mais eficiente no digital, mas a interação de sistemas digitais com o mundo físico, predominantemente analógico, exige superar desafios de compatibilidade entre esses dois domínios.

Para aproveitar a capacidade de processamento dos sistemas digitais no controle de dispositivos com base nos sinais analógicos amostrados pelos sensores, é essencial desenvolver circuitos conversores que realizem a transição entre os sinais analógicos e digitais. O circuito responsável por converter sinais digitais em analógicos é chamado de **Conversor Digital-Analógico** (em inglês, *Digital to Analog Converter* – DAC). Por sua vez, a conversão de sinais analógicos para digitais é feita pelos **Conversores Analógico-Digitais** (em inglês, *Analog to Digital Converter* – ADC). Esses circuitos são fundamentais para integrar informações do mundo físico aos sistemas computacionais, permitindo o controle e processamento digital desses dados. Geralmente, esses conversores estão integrados em uma interface analógica.

Antigamente, os conversores analógico-digitais (ADC) e digitais-analógicos (DAC) eram frequentemente implementados como circuitos integrados individuais encapsulados, contendo todos os componentes necessários para a conversão entre sinais analógicos e digitais. Os DACs geravam sinais analógicos a partir de dados digitais, enquanto os ADCs convertiam sinais analógicos em formato digital para processamento em microcontroladores. Hoje em dia, esses conversores estão cada vez mais integrados diretamente em microcontroladores, sensores e atuadores, otimizando o *design* e a eficiência dos sistemas. Essa evolução permite maior compactação e eficiência nos dispositivos eletrônicos contemporâneos.

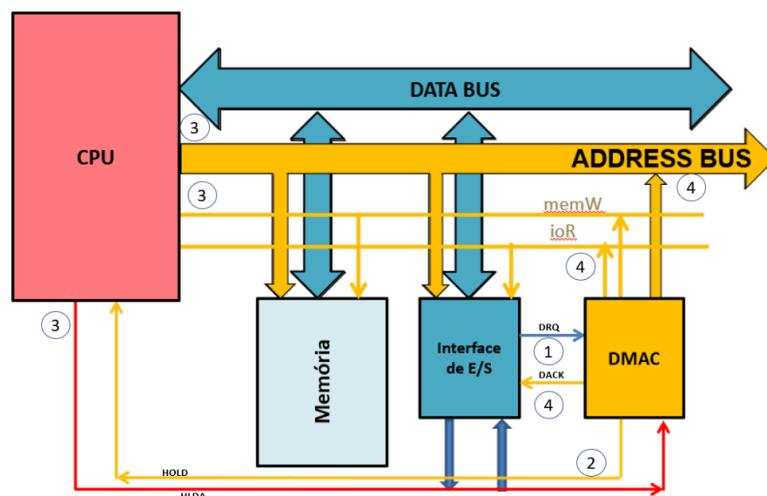

Além disso, a implementação de DMA (do inglês *Direct Memory Access*) nos sistemas digitais desempenha um papel crucial na eficiência geral. O DMA permite a transferência de dados entre os conversores e a memória sem a intervenção contínua da CPU, liberando recursos do processador para outras tarefas. Isso resulta em um processamento mais rápido e eficiente, reduzindo a latência e melhorando o desempenho em aplicações que requerem a

coleta e o controle de grandes volumes de dados. Ao combinar conversores analógico-digitais e digitais-analógicos com tecnologias de DMA, os sistemas se tornam mais responsivos e capazes de lidar com a complexidade dos sinais do mundo físico de forma eficaz.

## PROJETOS-EXEMPLO

Desenvolveremos cinco projetos neste Roteiro. Inicialmente, no primeiro projeto, sintetizaremos formas de onda triangular e senoidal utilizando os DACs do microcontrolador. Em seguida, nos dois projetos subsequentes, concentraremos na leitura de sinais analógicos através do ADC, explorando duas abordagens distintas: conversão simples iniciada por *software* e conversão iniciada por *hardware* via *timer*. Finalmente, nos dois últimos projetos, utilizaremos os módulos DMA e DMAMUX para a transferência direta de dados entre os conversores e a memória, empregando o controlador de DMA e o roteador DMAMUX.

### Projeto de conversão D/A básica

Muitas vezes é necessário sintetizar sinais analógicos variantes no tempo. Um exemplo são os geradores de função usados em bancadas de eletrônica. Para que possamos gerar estes sinais analógicos a partir das amostras digitais, uma das maneiras de se fazer isto é usando o Conversor Digital-Analógico (DAC). Vamos explorar neste projeto uma forma direta de transferência de amostras digitais para o DAC, com a taxa de transferência controlada por interrupção de *timer*. Utilizaremos os dois DACs do microcontrolador para gerar, de forma simultânea, duas formas de onda distintas: uma triangular e outra senoidal. As amostras inteiras, com valores entre 0 e 4096, serão calculadas e convertidas para tensões analógicas no intervalo de 0 a 3.3V a cada interrupção do núcleo.

1. Crie um novo projeto usando o *Cube*, com o nome “DAC\_Basico”, **sem inicializar os periféricos**. Ative o *Debug* e gere o código, mantendo o *clock* padrão de 64MHz.

2. Para que se possa gerar a senóide, precisamos usar funções matemáticas que não estão nativas no C, mas estão disponíveis em uma biblioteca padrão. No escopo de `/* USER CODE BEGIN Includes */`, inclua a biblioteca:

```

#include <math.h>

```

3. Defina as constantes que vamos usar. No escopo de `/* USER CODE BEGIN PD */`, crie as macros:

```

#define PI 3.14159265358979

#define SAMPLES 100 // Numero de amostras do vetor

#define DAC_MAX_VALUE 4095 // Valor maximo do vetor (DAC de 12 bits)

#define OFFSET 2048 // "Offset" para somar em todas as amostras (todos os valores positivos)

```

4. Ainda nesta etapa de preparação, vamos criar os protótipos das funções de configuração dos periféricos que vamos utilizar (DAC para conversão e TIM7 para interrupções periódicas). No escopo de `/* USER CODE BEGIN PFP */`, declare os protótipos das funções de configuração desses periféricos:

```

void Config_DAC(void);

void Config_Timer(void);

e funções definidas no arquivo stm32h7xx_it.c:

uint8_t leFlag();

void resetFlag();

```

5. Agora dentro da função “main”, vamos declarar uma variável auxiliar para “varrer” o vetor e definir as amostras da senóide. No escopo de `/* USER CODE BEGIN 1 */`, declare as variáveis locais:

```

int8_t step = 0;           // índice de amostra da onda triangular

int8_t direction = 1;     // 1 para subir, -1 para descer

uint8_t i = 0;             // índice de amostra da onda senoidal

uint32_t dac_value, sine_wave;

```

6. Antes de configurar os periféricos, vamos chamar as funções de configuração dos periféricos.

```

Config_DAC();

Config_DMA();

```

7. Dentro do laço infinito, a cada interrupção do *timer*, o canal DAC1\_OUT2 (PA5) e o canal DAC2\_OUT1 (PA6) são carregados com novas amostras digitais da onda triangular e senoidal, respectivamente. Insira no escopo `/* USER CODE BEGIN 3 */` os cálculos das amostras digitais `dac_value` e `sine_wave` correspondentes aos índices `step` e `i` das ondas triangular e senoidal, respectivamente.

```

if (leFlag()) {

//Reseta flag

resetFlag();

// Calcular o proximo valor da onda triangular

step += direction;

// Verificar limites da onda triangular (0 a 4095)

if (step >= 50) {

direction = -1; // Começar a descer

step = 50;

} else if (step <= 0) {

direction = 1; // Começar a subir

step = 0;

}

// Ajustar o valor para escala de 12 bits (4096 níveis)

dac_value = (step * 4095) / 50;

//Calcula o proximo valor da onda senoidal

```

```

sine_wave = (uint32_t)(OFFSET + (OFFSET * sin(2 * PI * i / SAMPLES)));

if(sine_wave > DAC_MAX_VALUE) {

sine_wave = DAC_MAX_VALUE;

}

i++;

if (i == SAMPLES) i = 0;

// Atualizar os valores do DAC1_OUT2 e DAC2_OUT1

DAC1->DHR12R2 = dac_value; //PA5

DAC2->DHR12R1 = sine_wave; //PA6

}

```

O procedimento implementa uma rampa com comportamento ascendente nos primeiros 50 passos e descendente nos 50 subsequentes, além de gerar uma senóide completa ao longo de 100 passos.

8. Agora, precisamos definir as funções de configuração dos periféricos, iniciando pelo DAC. No escopo de `/* USER CODE BEGIN 4 */`, escreva o código:

```

void Config_DAC(void) {

// Habilitar o clock do DAC1 e DAC2

RCC->APB1LENR |= RCC_APB1LENR_DAC12EN; // DAC1 (2 canais)

RCC->APB4ENR |= RCC_APB4ENR_DAC2EN; // DAC2

// Configurando DAC2, canal 1 (sem trigger)

DAC2->CR = 0; // Inicia com os bits zerados

DAC2->CR |= DAC_CR_EN1; // Habilitar o canal 1 do DAC2

// Configurar o DAC1, canal 2 (sem trigger)

DAC1->CR = 0; // Inicia com os bits zerados-

DAC1->CR |= DAC_CR_EN2; // Habilitar o canal 2 do DAC1

// Configurar PA5 e PA6 para DAC_Out (modo analógico)

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOAEN; // Permite configurar o GPIOA

GPIOA->MODER |= (GPIO_MODE5_Msk | GPIO_MODE6_Msk); // MODER

= 11 em PA5 e PA6

}

```

Nessa função apenas habilitamos os canais dos DACs e garantimos que os pinos PA5 e PA6 estejam no modo analógico. Note que quando um pino do microcontrolador STM32H7A3 é configurado como analógico, ele automaticamente é atribuído à função analógica definida para aquele pino (DAC ou ADC), sem necessidade de configuração de função alternativa.

O valor padrão de [calibração](#) é o valor de ajuste de fábrica, e ele é carregado uma vez que a interface digital do DAC é resetada. Quando as condições de operação diferem das condições de ajuste de fábrica nominais, pode ser feita re-calibração a qualquer momento durante a aplicação por meio de *software*.

9. Ainda no mesmo escopo, vamos definir a função de configuração do *timer*. Vamos usar o *timer* 7 para a cadência das duas ondas. Abaixo da função anteriormente criada, escreva essa nova função:

```

void Config_Timer(void) {

// Enable clock for TIM6 e TIM7

RCC->APB1LENR |= RCC_APB1LENR_TIM7EN;

// TIM7: Faz interrupção periódica

// Resetar os registradores de TIM7

TIM7->EGR |= TIM_EGR_UG_Msk;

while (TIM7->EGR & TIM_EGR_UG);

TIM7->CR1 = 0;

TIM7->PSC = 64 - 1; // Dividir clock por 64 -> 1MHz

TIM7->ARR = 20 - 1; // Contar até 20 -> 50kHz

TIM7->CR1 = 0; // Registradores de controle inicialmente zerados

TIM7->CR2 = 0;

TIM7->DIER |= TIM_DIER_UIE; // Habilitar interrupção de update (UIE)

TIM7->CR1 |= TIM_CR1_CEN; // Start timer

// Configurar prioridade da interrupção de TIM7 e habilitar no NVIC

NVIC_SetPriority(TIM7_IRQn, 1);

NVIC_EnableIRQ(TIM7_IRQn);

}

```

No *timer 7*, foi realizado o procedimento padrão para interrupção periódica, com um período de 50kHz. Como vamos gerar as ondas com 100 amostras por ciclo, teremos 500 ciclos por segundo, ou seja, uma frequência de 500Hz.

10. Por fim, é necessário definir a ISR para sinalizar as ocorrências de interrupções periódicas para atualização das amostras. Abra o arquivo “stm32h7xx\_it.c”. Vamos inicialmente criar 1 variável global no escopo */\* USER CODE BEGIN PV \*/*

```

uint8_t flag;

declarar protótipos de duas funções no escopo /* USER CODE BEGIN PFP */

uint8_t leFlag();

void resetFlag();

```

e implementar essas funções no escopo */\* USER CODE BEGIN EV \*/*

```

uint8_t leFlag() {

return flag;

}

void resetFlag() {

flag = 0;

}

```

11. No escopo de */\* USER CODE BEGIN 1 \*/*, implemente a ISR:

```

void TIM7_IRQHandler(void) {

// Verificar se a interrupção é de update

if (TIM7->SR & TIM_SR UIF) {

TIM7->SR &= ~TIM_SR UIF; // Limpar o flag de interrupção

flag = 1;

}

}

```

```

}

}

```

Essencialmente, esta rotina de serviço indica uma interrupção periódica, a qual dispara o envio de um novo par de amostras para gerar as formas de onda.

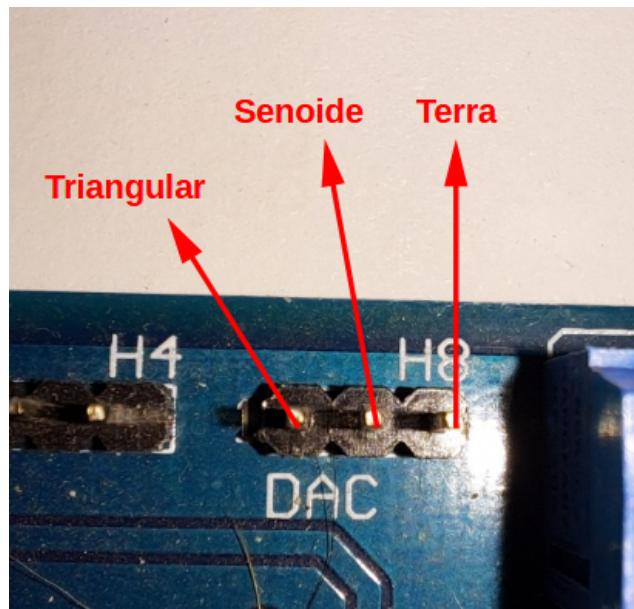

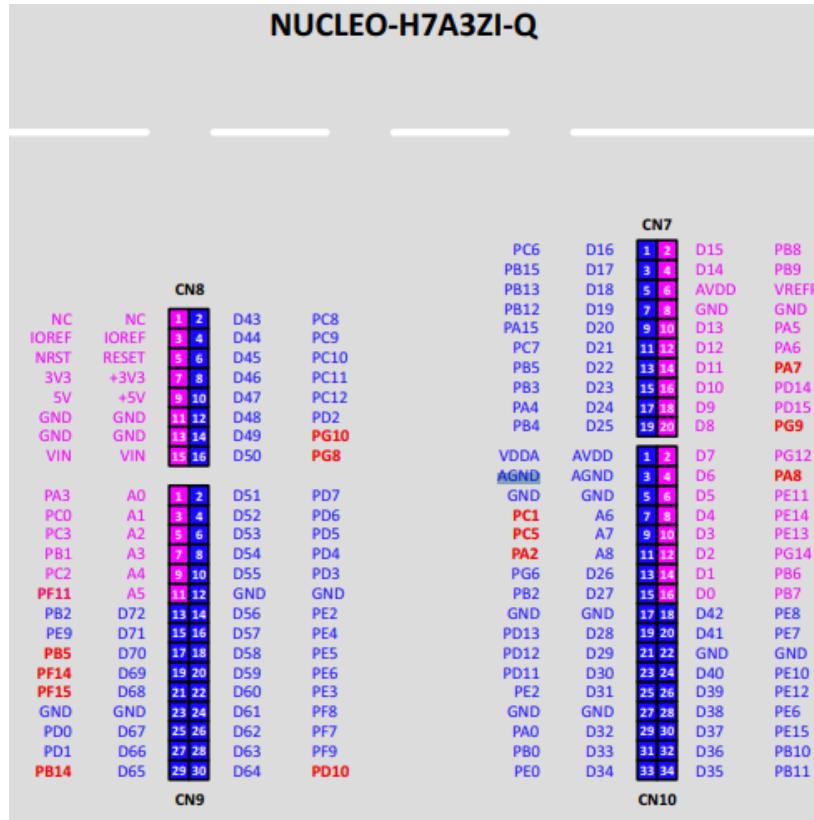

12. Faça um *Build*. Conecte as pontas de prova do osciloscópio nos pinos 1 e 2 do [conector H8](#) (DAC). Ligue o terra do **osciloscópio** no pino 3 do mesmo conector, ou em outro ponto de terra, como o pino 7 do conector H9 (ADC). Veja a figura a seguir.

13. Transfira o código para o microcontrolador e execute o programa. Ajuste o **osciloscópio** para visualizar as formas de onda. Meça as frequências das mesmas, comparando com o previsto em função do número de amostras e da frequência configurada para o *timer*.

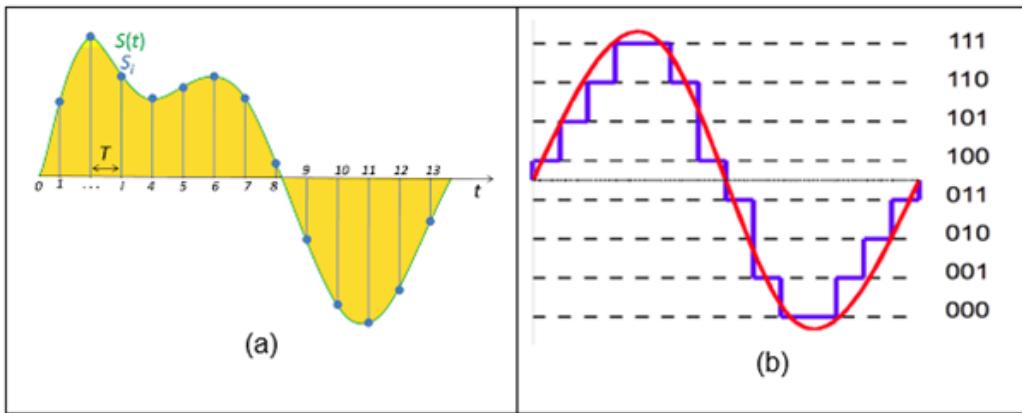

14. Dê um *zoom* nos sinais para ver a discretização dos mesmos, caracterizada por pequenos “degraus”. Para reduzir a percepção desses degraus, podemos simplesmente aumentar o número de amostras? No caso da senóide, a geração de amostras e o controle da transferência de dados são parametrizados pela macro SAMPLES. Portanto, alterar o valor de SAMPLES em sua definição global aplicará a modificação a todo o programa. Experimente modificar o valor de SAMPLES de 100 para 200, recompilar e re-executar o programa. Essa alteração afetou o intervalo entre duas amostras? E o período do sinal gerado, foi alterado? Qual o efeito visual do aumento do número de amostras na forma de onda exibida?

Considerando agora a redução do valor do registrador de auto-recarga pela metade (para 10-1), qual seria o novo intervalo entre as amostras e o período do sinal gerado?

Você consegue descrever como os sinais podem ser suavizados? Caso nenhuma solução para a suavização surja neste momento, podemos prosseguir e revisitar essa questão posteriormente.

15. Para fazer o mesmo com a onda triangular, todos os valores “50” dentro da ISR devem ser mudados para “100, mantendo o valor de auto-recarga em (10-1). Estes valores ocorrem em 3

das linhas de código da `main`, sendo de fácil localização. Certifique se mudou as 3 ocorrências do valor 50 para 100 antes de recompilar. Re-execute o programa. Veja agora os “degraus” no sinal. O que mudou? Você consegue explicar essa mudança? Já consegue dizer quais são os parâmetros que controlam a suavidade de um sinal digital? Caso não tenha uma solução ainda, prossigamos e veremos se essa ideia surge mais adiante.

16. Vamos analisar a relação entre as amostras digitais (entre 0 e 4096) e os correspondentes valores analógicos (na faixa de 0V a 3.3V). Para isso, insira um breakpoint na linha de instrução “`i++;`”. Quando a execução do programa pausar nesse ponto, utilize um **multímetro** para medir a tensão nos pinos PA5 e PA6 para os valores da variável `step` indicados na primeira coluna da tabela a seguir. Registre tanto os valores de tensão medidos quanto os valores das amostras correspondentes.

| step | i | sine_wave | PA6 (em Volts) | dac_value | PA5 (em Volts) |

|------|---|-----------|----------------|-----------|----------------|

| 10   |   |           |                |           |                |

| 25   |   |           |                |           |                |

| 50   |   |           |                |           |                |

| 75   |   |           |                |           |                |

| 99   |   |           |                |           |                |

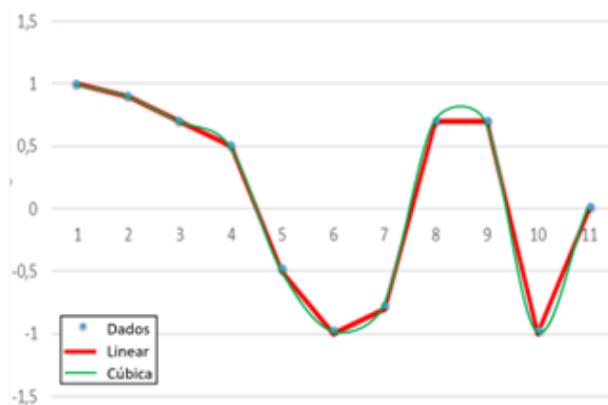

Posteriormente, investigue a correlação entre os valores das amostras e os resultados das conversões nos canais analógicos. Essa relação é linear? Se você quiser quantificar essa relação, use uma técnica de regressão.

17. Se conectarmos um *buzzer* entre o pino 1 e o terra ou entre o pino 2 e o terra, e aproximá-lo do seu ouvido, qual será sua percepção sonora? Você consegue explicar o fenômeno observado? Nessa configuração específica, o *buzzer* funciona como um sensor ou um atuador? Trata-se de um periférico digital ou analógico? Caso esses conceitos ainda não estejam totalmente claros, não se preocupe. Eles serão detalhados em seções futuras, e então você terá as ferramentas para explicar suas observações.

18. Declaramos `dac_value` e `sine_wave` como inteiros de 32 *bits*. Precisamos de tantos *bits*? Investigue o tamanho dos dados para os quais essas variáveis irão passar para descobrir.

19. Você já se questionou sobre o momento em que a conversão de cada valor digital tem início? É possível para um desenvolvedor configurar com precisão o início de cada conversão no STM32H7? A resposta a estas questões será abordada posteriormente.

20. Qual técnica de conversão digital-analógica é utilizada nos conversores DAC do microcontrolador STM32H7A? Caso a resposta não seja imediata, não se preocupe, ela será apresentada em breve.

## Projeto de conversão A/D básica

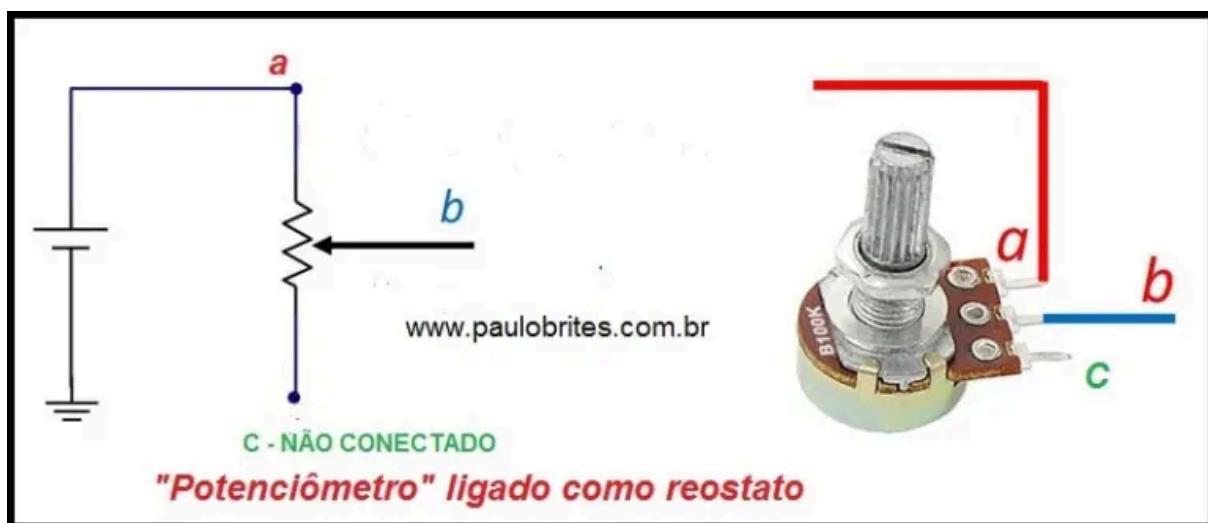

Sabe como um voltímetro funciona? Imagine a possibilidade de criar o seu próprio voltímetro digital usando um conversor ADC! Neste projeto, vamos explorar juntos como transformar uma simples leitura de tensão em um *display* digital. Vamos aprender não apenas sobre o funcionamento do ADC, mas também sobre a conversão de sinais analógicos em dados que podemos visualizar e interpretar, através das amostras coletadas de um potenciômetro. Pense nas potenciais aplicações: medir a tensão da bateria do seu celular, monitorar circuitos eletrônicos ou até mesmo experimentar com diferentes componentes! A implementação do seu próprio voltímetro digital será uma excelente oportunidade para aplicar conceitos teóricos na prática, desenvolvendo suas habilidades e ampliando seu conhecimento.

1. Crie um novo projeto usando o *Cube*, com o nome “ADC\_Basico”, **sem inicializar os periféricos**. Ative o *Debug* e gere o código, mantendo o *clock* padrão de 64MHz.

2. Vamos criar duas funções, uma para configurar o ADC e outra para realizar uma leitura no ADC em `main.c`. No escopo de `/* USER CODE BEGIN PFP */`, crie os protótipos das funções:

```

void Config_ADC(void);

uint16_t Le_ADC(void);

```

3. No escopo de `/* USER CODE BEGIN 4 */`, vamos implementar as funções, começando com a de configuração:

```

void Config_ADC(void) {

//Configurar PC4 como analog

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOCEN;

GPIOC->MODER |= GPIO_MODE4;

// Habilitar o clock do ADC1

RCC->AHB1ENR |= RCC_AHB1ENR_ADC12EN;

// Resetar o ADC1 (garantir que o ADC esteja desabilitado antes de

configurar)

if (ADC1->CR & ADC_CR_ADEN) {

ADC1->CR |= ADC_CR_ADDIS; // Desabilitar o ADC se já estiver

habilitado

while (ADC1->CR & ADC_CR_ADEN); // Aguardar até o ADC ser

desabilitado

}

ADC1->CR = 0;

// Desabilitar o deep power down

ADC1->CR &= ~ADC_CR_DEEPPWD;

// Habilitar o regulador de tensão do ADC (modo intermediário)

ADC1->CR |= ADC_CR_ADVREGEN;

// Aguardar estabilização do regulador de tensão do ADC

while (!(ADC1->ISR & ADC_ISR_LDORDY));

// Definir a fonte de ADC clock: clock do sistema/2 (64MHz/2)

// O registrador eh comum para os 2 modulos

ADC12_COMMON->CCR &= ~(ADC_CCR_CKMODE);

ADC12_COMMON->CCR |= ADC_CCR_CKMODE_1;

```

```

// Calibrar o ADC1 (modo de entrada única)

ADC1->CR &= ~ADC_CR_ADCALDIF; // Garantir que a calibração seja no

modo single-ended

ADC1->CR |= ADC_CR_ADCAL; // Iniciar calibração

while (ADC1->CR & ADC_CR_ADCAL); // Aguardar fim da calibração

// Após a calibração, aguardar a estabilização do ADC

for(int i = 0; i < 10000; i++);

// Configurar o ADC1 para conversão no canal 4

ADC1->SQR1 = 0;

ADC1->SQR1 &= ~ADC_SQR1_L; // Configuração para conversão de 1

canal

ADC1->SQR1 |= ADC_SQR1_SQ1_2; // Selecionar canal 4 na sequência

regular

// Configurar o tempo de amostragem do canal 4 (adequado para precisão)

ADC1->SMPR1 &= ~ADC_SMPR1_SMP4; // Limpar configurações anteriores

ADC1->SMPR1 |= ADC_SMPR1_SMP4_2; // Amostragem de 32.5 ciclos de ADC

ADC1->PCSEL |= ADC_PCSEL_PCSEL_4; // Pre-seleciona canal 4

// Configurar a resolução (16 bits)

ADC1->CFGGR &= ~ADC_CFGGR_RES;

// Habilitar o ADC

ADC1->ISR |= ADC_ISR_ADRDY; // Limpar flag de prontidão

ADC1->CR |= ADC_CR_ADEN; // Habilitar ADC1

while (!(ADC1->ISR & ADC_ISR_ADRDY)); // Aguardar até o ADC estar

pronto

}

```

Inicialmente, a função configura o pino PC4 como pino analógico, [mapeado no canal 4 do ADC1](#). Depois, aciona o *clock gating* do ADC1. Na sequência, configura o *clock* do sistema (64MHz)/2 como fonte de *clock* para circuito do ADC. Em seguida, ativa o regulador de tensão do ADC e realiza a autocalibração. Por fim, seleciona o canal 4 para aquisição e habilita o ADC1 para conversões.

4. Agora vamos implementar a função que realiza a conversão A/D iniciada com um disparo por *software*, aguarda por *polling* a conclusão da conversão e retorna o valor obtido. Após a função anterior, implemente a de leitura:

```

uint16_t Le_ADC(void) {

// Verificar se o ADC está pronto

while (!(ADC1->ISR & ADC_ISR_ADRDY)) {}

// Iniciar conversão de canal único por software

ADC1->CR |= ADC_CR_ADSTART;

// Aguardar até a conversão estar completa

while (!(ADC1->ISR & ADC_ISR_EOC)) {}

// Verificar se ocorreu um overrun

// (sobrescrita do valor anterior ainda não acessado)

if (ADC1->ISR & ADC_ISR_OVR) {

ADC1->ISR |= ADC_ISR_OVR; // Limpar a flag de overrun, por

precaucao

}

// Ler o valor da conversão

}

```

```

return (uint16_t)ADC1->DR;

}

```

Ao ser chamada, a função inicialmente verifica se o ADC está disponível para realizar uma conversão (*flag* ADRDY). Depois, **dispara uma conversão A/D por software** (setando o *bit* ADSTART) e entra em um *loop* testando o *flag* EOC (*End of Conversion*). Por fim, limpa o *flag* de *overrun* (evento de estouro do *buffer*, quando os dados de conversão não são lidos pelo processador) e lê o registrador DR, que armazena o valor da conversão em 16 *bits*, retornando o valor lido. Note que o registrador DR é de 32 *bits*, sendo os 16 menos significativos o resultado da conversão, e por isso é feito uma conversão (um *cast*) para 16 *bits* sem sinal no valor a ser retornado.

5. Agora vamos à função “main()”. Inicialmente, vamos declarar variáveis locais. No escopo de `/* USER CODE BEGIN 1 */`, declare as variáveis:

```

uint16_t adc;

float tensao;

```

6. Antes do *loop* infinito vamos configurar o ADC. No escopo de `/* USER CODE BEGIN 2 */`, chame a função de configuração:

```

Config_ADC();

```

e abaixo da linha `/* USER CODE BEGIN 3 */`, escreva o código:

```

adc = Le_ADC();

tensao = (adc * 3.3) / 65535.0;

HAL_Delay(100);

```

A primeira linha realiza a conversão A/D, guardando o resultado na variável “adc”. A segunda linha calcula o valor de tensão correspondente ao valor lido no ADC, sendo o valor resultante expresso em Volts, em uma variável de ponto flutuante. A terceira linha realiza uma espera de 100ms antes de uma nova aquisição de valor analógico.

A equação para cálculo da tensão leva em conta que o valor de “Vrefl” é 0 e o valor de “Vrefh” é a tensão de alimentação, ou seja, 3.3V. Além disso, a resolução da conversão é em 16 *bits*, ou seja, o valor máximo de tensão corresponde ao valor máximo da variável de 16 *bits* (escala cheia).

A implementação da função `HAL_Delay(X)`, que introduz um atraso de X milissegundos no fluxo de controle, é semelhante à da função `void Delay(uint32_t ms)` presente no projeto `Delay_1ms` do Roteiro 5. Por padrão, o módulo SysTick, configurado com um período de 1ms, é inicializado no código gerado pelo STM32CubeMX. Quando `HAL_Delay` é chamada, a interrupção do SysTick é habilitada, e o incremento do seu contador é monitorado dentro da rotina de serviço de interrupção `SysTick_Handler`, localizada no arquivo `stm32h7xx_it.c`.

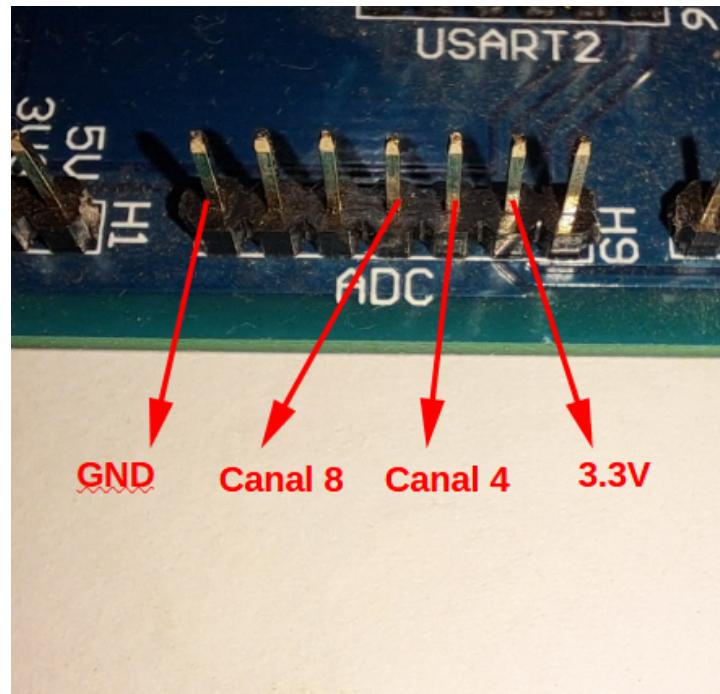

7. Adicione um *breakpoint* na linha “HAL\_Delay(100);”. Faça o *Build* do programa. Depois, conecte o terminal central do potenciômetro no canal 4 (pino 3) no conector H9 (ADC). Ligue um dos terminais laterais do potenciômetro no pino 2 do conector (3.3V) e o outro terminal lateral no pino 7 do conector (GND). Como referência, use a figura abaixo.

**OBS: Cuidado para não usar o primeiro pino do conector**, pois ele está ligado à fonte de 5V da placa. Se o potenciômetro for ligado neste pino, ele fornecerá tensões entre 0 e 5V, e não de 0 a 3.3V. O conversor A/D do STM32H7A3 aceita um valor máximo de 3.3V em suas entradas analógicas, e valores maiores podem causar danos ao componente.

8. Realize o *Debug*. Abra a aba *Variable* para monitorar o valor das variáveis “tensao” e “adc”, e execute o programa. Quando ele for interrompido (o que vai levar vários segundos), meça a tensão entre o terminal central e o GND do potenciômetro usando o **multímetro**. Analise o valor das variáveis “adc” e “tensao”, comparando esta última com o valor medido. Mova o *cursor* (braço móvel) do potenciômetro para outra posição e dê um *Resume*, experimentando vários valores, sempre comparando a tensão medida no potenciômetro com o valor calculado no programa. Para comparação, preencha a seguinte tabela com os valores de 5 amostras.

| Amostra | “adc” | “tensao” (V) | Tensão Medida (V) |

|---------|-------|--------------|-------------------|

| 1       |       |              |                   |

| 2       |       |              |                   |

| 3       |       |              |                   |

|   |  |  |  |

|---|--|--|--|

| 4 |  |  |  |

| 5 |  |  |  |

Como você explica a fórmula usada para converter o valor “bruto” do ADC (“adc”) em um valor de tensão correspondente (“tensao”)? Qual é a diferença média entre os valores obtidos pelo conversor ADC e pelo multímetro?

Qual é a relação entre as amostras analógicas (Tensão Medida) e os valores digitais (adc) observados? Essa relação é linear? A equação obtida por meio de uma técnica de regressão se assemelha à fórmula utilizada para converter o valor adc em tensao?

9. Nesse projeto, o potenciômetro atua como um sensor ou um atuador analógico? Caso esses conceitos ainda não estejam claros, não se preocupe, eles serão detalhados posteriormente e você conseguirá responder.

10. Para iniciar uma conversão do ADC via *software*, qual registrador é acionado? Após essa ativação, o ADC efetua uma única leitura ou prossegue com conversões em sequência? Qual é o impacto da ausência dessa inicialização no processo de conversão? As respostas para essas perguntas serão exploradas no próximo projeto-exemplo.

11. Quais modificações você faria no projeto se mudarmos a resolução de conversão de 16 *bits* para 10 *bits*? Nós veremos mais adiante a resposta para esta pergunta.

12. Qual é a taxa de superamostragem configurada para o controlador ADC neste projeto? Onde está essa configuração? Se não tiver nenhuma ideia, vamos descobrir onde está essa configuração juntos.

13. Considerando que o registrador ADC1->SQR1 define a sequência de conversão e, por conseguinte, a ordem dos canais a serem convertidos, qual a justificativa para a necessidade de pré-selecionar um canal separadamente, através do registrador ADC1->PCSEL, se este já está explicitamente incluído na referida sequência? Parece redundante, não é? Adiante, exploraremos como essa aparente duplicação reflete as nuances das soluções de *hardware*, que podem variar significativamente entre projetos, resultando em diferentes arquiteturas de registradores de configuração.

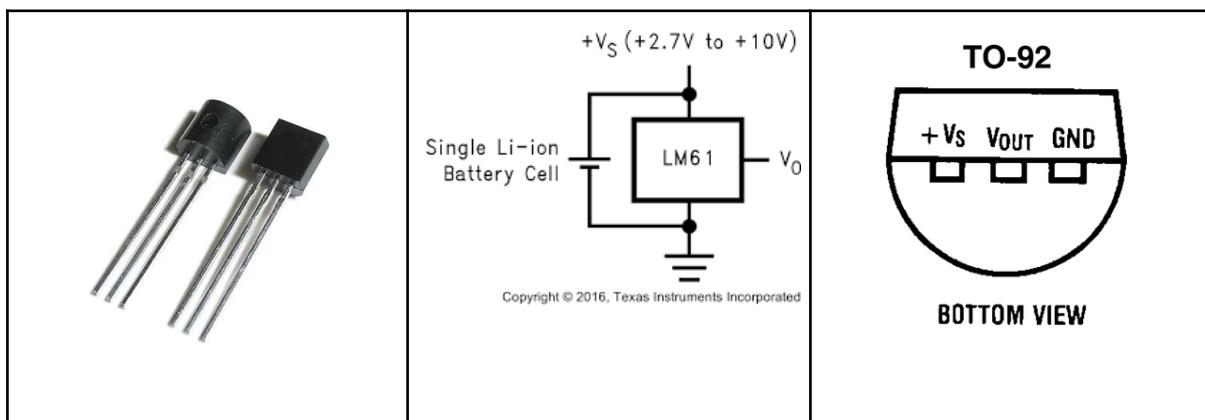

### **Projeto de conversor A/D disparado por *hardware* e geração de evento de “fim de conversão”**

Você já pensou na importância de monitorar dados meteorológicos, como a temperatura, de forma precisa e eficiente? Imagine um projeto onde você pode coletar essas informações automaticamente, transformando um simples sinal analógico em informações. Vamos explorar como obter amostras periódicas de um sensor de temperatura. Você poderia fazer uma conversão A/D única, controlando o momento de aquisição pelo *software* e aguardando o fim de uma conversão por *polling*, como vimos no projeto anterior. Mas e se quisermos uma

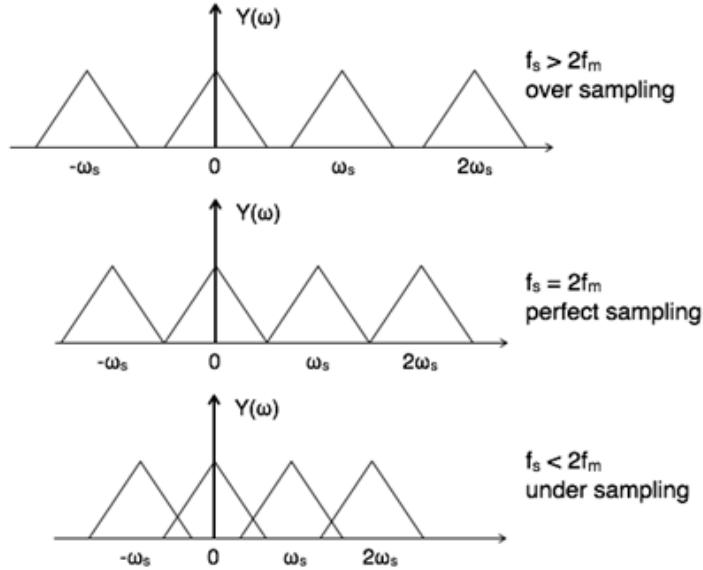

coleta contínua, com uma taxa de amostragem consistente? É possível aprimorarmos o nosso projeto com mínima sobrecarga de *software*?

Uma alternativa para eliminar o *polling* seria habilitar o evento de interrupção de “fim de conversão”. Dessa forma, o fluxo de controle seria desviado por *hardware* para a rotina de serviço `ADC_IRQHandler` assim que uma conversão fosse concluída. Para implementar uma coleta periódica, podemos utilizar um temporizador configurado para gerar interrupções periódicas. Dentro da rotina de tratamento dessas interrupções, iniciariíamos uma nova conversão, garantindo a periodicidade das aquisições. Com essas interrupções periódicas e a habilitação das interrupções de “fim de conversão”, apenas duas intervenções por *software* seriam necessárias: uma para iniciar a conversão por *software* e outra para ler o resultado.

E se substituirmos as conversões iniciadas por *software* por conversões disparadas por *hardware*? Imagine o sinal de fim de contagem de um período de um temporizador conectado diretamente ao pino de inicialização da conversão ADC. Nesse cenário, a conversão seria iniciada automaticamente a cada evento de interrupção periódica gerado pelo temporizador. Dessa forma, o programa se tornaria mais eficiente, dedicando-se exclusivamente ao processamento dos resultados da conversão, acessíveis na rotina de serviço `ADC_IRQHandler`.

Considere agora que esse sinal analógico provém de um sensor de temperatura, como o [sensor LM61](#), que produz uma tensão proporcional à temperatura medida. Com essa abordagem, você não apenas monitoraria a temperatura de forma periódica, mas também teria a oportunidade de explorar a interação entre *hardware* e *software*, aprofundando suas habilidades em eletrônica e programação.

1. Crie um novo projeto usando o *Cube*, com o nome “ADC\_TrigTimer”, **sem inicializar os periféricos**. Ative o *Debug* e gere o código, mantendo o *clock* padrão de 64MHz.

2. Como no projeto anterior, vamos criar algumas funções, sendo uma para configurar o ADC, uma para configurar o *timer*, uma para iniciar as conversões periódicas e outra para parar as conversões. Além disso, dentro do arquivo “stm32h7xx\_it.c” vamos criar uma função para indicar se há resultado novo no ADC e outra para realizar a leitura do resultado. Para estas duas funções no outro arquivo, precisamos prototipá-las no arquivo “main.c”. No escopo de `/* USER CODE BEGIN PFP */`, crie os protótipos das funções:

```

void Config_Timer(void);

void Config_ADC(void);

void Start_Conv(void);

void Stop_Conv(void);

uint8_t ADC_Complete(void);

uint16_t Read_Data(void);

```

3. No escopo de `/* USER CODE BEGIN 4 */`, vamos implementar as quatro primeiras funções, começando com a de configuração de *timer*:

```

void Config_Timer(void) {

RCC->APB1LENR |= RCC_APB1LENR_TIM6EN; // Habilita clock de TIM6

TIM6->EGR |= TIM_EGR_UG_Msk; // atualizacao inicial dos registradores

while (TIM6->EGR & TIM_EGR_UG);

TIM6->CR1 &= ~TIM_CR1_CEN; // Desabilita o contador

TIM6->PSC = 63999; // Prescaler, assumindo clock de 64 MHz, timer a 1

kHz

TIM6->ARR = 99; // Periodo do timer: 1kHz / 100 = 10Hz

TIM6->CR2 &= ~TIM_CR2_MMS;

TIM6->CR2 |= TIM_CR2_MMS_1; // MMS[2:0] = 010: Update Event

}

```

Nesta função, configuramos o temporizador para gerar um evento de atualização a cada 100 ms, o que corresponde a uma frequência de 10 vezes por segundo. Embora a interrupção do temporizador não esteja sendo habilitada, o TIM6 está sendo configurado para emitir um sinal de evento ao ocorrer cada atualização através de [TIM6\\_CR2](#). Esse sinal de evento pode ser roteado para diversos periféricos e, caso estes estejam configurados para tal, pode deflagrar o início de suas operações. Em nosso projeto, o evento de atualização do TIM6 será utilizado para disparar automaticamente o início da conversão do ADC1, que será configurado para essa finalidade. Observe que, nesta etapa da configuração, a contagem do temporizador ainda não foi habilitada. Essa ação será realizada posteriormente.

4. Na sequência, vamos implementar a função de configuração do ADC:

```

void Config_ADC(void) {

//Configurar PC4 como analog

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOCEN;

GPIOC->MODER |= GPIO_MODER_MODE4;

{

// Este trecho habilita o pino PC5 configurado para servir de GND

// digital, evitando jumpers adicionais na conexao do sensor com AGND

// Se usar AGND, remova este bloco de instrucoes

GPIOC->MODER |= GPIO_MODER_MODE4;

GPIOC->MODER &= ~GPIO_MODER_MODE5;

GPIOC->MODER |= GPIO_MODER_MODE5_0; // PC5 em GPIO output

GPIOC->OTYPER |= GPIO_OTYPER_OT5; // PC5 open drain

GPIOC->BSRR = GPIO_BSRR_BR5; // Nivel low

}

// Habilitar o clock do ADC1

RCC->AHB1ENR |= RCC_AHB1ENR_ADC12EN;

// Resetar o ADC1 (garantir que o ADC esteja desabilitado antes de

configurar)

if (ADC1->CR & ADC_CR_ADEN) {

ADC1->CR |= ADC_CR_ADDIS; // Desabilitar o ADC se já estiver

habilitado

while (ADC1->CR & ADC_CR_ADEN); // Aguardar até o ADC ser

desabilitado

}

ADC1->CR = 0;

}

```

```

// Desabilitar o deep power down

ADC1->CR &= ~ADC_CR_DEEPPWD;

// Habilitar o regulador de tensão do ADC (modo intermediário)

ADC1->CR |= ADC_CR_ADVREGEN;

// Aguardar estabilização do regulador de tensão do ADC

while(!(ADC1->ISR & ADC_ISR_LDORDY));

// Definir a fonte de ADC clock: clock do sistema/2 (64MHz/2)

// O registrador eh comum para os 2 modulos

ADC12_COMMON->CCR &= ~(ADC_CCR_CKMODE);

ADC12_COMMON->CCR |= ADC_CCR_CKMODE_1;

// Calibrar o ADC1 (modo de entrada única)

ADC1->CR &= ~ADC_CR_ADCALDIF; // Garantir que a calibração seja no

modo single-ended

ADC1->CR |= ADC_CR_ADCAL; // Iniciar calibração

while (ADC1->CR & ADC_CR_ADCAL); // Aguardar fim da calibração

// Após a calibração, aguardar a estabilização do ADC

for(int i = 0; i < 10000; i++);

// Configurar o ADC1 para conversão no canal 4

ADC1->SQR1 = 0;

ADC1->SQR1 &= ~ADC_SQR1_L; // Configuração para conversão de 1

canal

ADC1->SQR1 |= ADC_SQR1_SQ1_2; // Selecionar canal 4 na sequência

regular

// Configurar o tempo de amostragem do canal 4

ADC1->SMPR1 &= ~ADC_SMPR1_SMP4; // Limpar configurações anteriores

ADC1->SMPR1 |= ADC_SMPR1_SMP4_2; // Amostragem de 32.5 ciclos de ADC

ADC1->PCSEL |= ADC_PCSEL_PCSEL_4; // Pre-seleciona canal 4

// Configurar a resolução (16 bits)

ADC1->CFGR &= ~ADC_CFGR_RES;

// Configurar o ADC para disparo externo pelo TIM6 Update Event

// Reference Manual, Tabelas 194 e 196.

ADC1->CFGR &= ~(ADC_CFGR_EXTSEL | ADC_CFGR_EXTEN); // Limpar

configuração anterior de trigger

ADC1->CFGR |= (ADC_CFGR_EXTSEL_3 |

ADC_CFGR_EXTSEL_2 |

ADC_CFGR_EXTSEL_0); // EXTSEL = 01101 para TIM6 Update Event

ADC1->CFGR |= ADC_CFGR_EXTEN_0; // Habilitar trigger em borda de subida

(EXTEN = 01)

//Configurar interrupção de EOC prioridade 1

ADC1->IER |= ADC_IER_EOCIE; // Habilita interrupção EOC

NVIC_SetPriority(ADC IRQn, 1); // Configura NVIC para interrupções do

ADC

NVIC_EnableIRQ(ADC IRQn);

// Habilitar o ADC1

ADC1->ISR |= ADC_ISR_ADRDY; // Limpar flag de prontidão

ADC1->CR |= ADC_CR_ADEN; // Habilitar ADC1

```

```

while (! (ADC1->ISR & ADC_ISR_ADRDY)) ; // Aguardar até o ADC estar

pronto

// Iniciar conversões

ADC1->CR |= ADC_CR_ADSTART;

}

```

A configuração do ADC é similar a do projeto anterior. Usamos o mesmo canal com as mesmas configurações. Porém, há uma adição de código após a configuração de conversão no canal 4. Na [Tabela 194 do Manual de Referência](#), pode-se ver que os *bits* EXTEN do registrador ADC\_CFGR precisam ter os valores “01” para que o ADC seja disparado por um sinal de *trigger* em borda de subida (ver [Figura 491 do Manual](#), sinal UEV, a borda de subida ocorre exatamente no *update*). A [Tabela 196 do Manual](#) mostra que a fonte de *trigger* externo denominada “adc\_ext\_trg13” para o ADC1 está relacionada ao “tim6\_trgo” (*Trigger Out* de TIM6, ou seja, seu *update*). Assim, os *bits* EXTSEL do registrador ADC\_CFGR devem conter o valor “01101”, ou seja, 13. Com o TIM6 configurado para gerar o sinal de atualização para outros periféricos e o ADC1 habilitado para utilizar o sinal do TIM6 como gatilho para conversões por *hardware*, o circuito de disparo das conversões do ADC1 está completo. Assim, a cada evento de atualização do TIM6, uma nova conversão será iniciada no ADC1.

Além da configuração do *trigger*, a interrupção de *End of Conversion* do ADC foi habilitada, e programada no NVIC com prioridade 1. Por fim, o *bit* ADSTART do registrador CR deve ser setado. Com o *trigger* por *hardware* configurado, este *bit* agora não inicia a conversão, mas habilita o ADC1 a responder ao *trigger*.

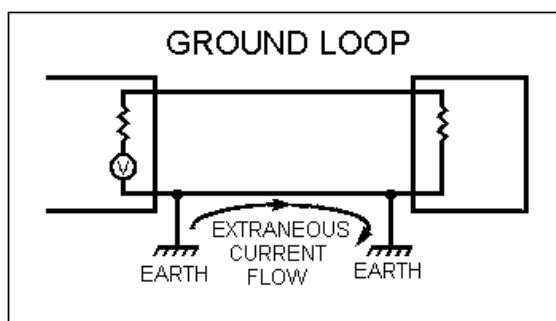

Por fim, note que o pino PC5 foi configurado como saída GPIO tipo “*open drain*” em nível baixo. Isto foi feito para que este pino, ao lado do pino PC4 no conector “ANALOG” da placa auxiliar, possa ser usado como GND para o sensor de temperatura. Assim, podemos ligar o conector do sensor diretamente no conector da placa. Como a corrente máxima do sensor é de 125  $\mu$ A, o pino será capaz de funcionar como um “terra” para o sensor. Em algumas situações, isto não é o ideal, pois estamos usando o terra digital no sensor analógico. Porém, para aplicações onde uma alta exatidão não é exigida e as conexões entre sensor e entrada A/D não são longas, pode ser uma boa opção. Nos nossos testes, o ruído máximo estimado no canal foi de 1.5mV. Preferivelmente, devemos usar o [pino 2 do conector CN10](#) (AGND) da placa NUCLEO.

5. Vamos agora implementar as funções para iniciar e parar a conversão periódica. Logo abaixo da função de configuração de ADC, implemente as duas funções:

```

void Start_Conv(void) {

TIM6->CR1 |= TIM_CR1_CEN; // Habilita o contador

}

void Stop_Conv(void) {

TIM6->CR1 &= ~TIM_CR1_CEN; // Desabilita o contador

}

```

Estas funções controlam a conversão periódica, ativando e desativando a contagem do *timer*. Se o *timer* estiver parado, o evento de atualização não ocorre e, consequentemente, o ADC configurado para iniciar as conversões por *hardware* não é disparado, mesmo estando habilitado e iniciado.

6. Vamos agora implementar as funções do arquivo “stm32h7xx\_it.c”. Inicialmente, vamos definir variáveis no escopo do arquivo para auxiliar nas funções. No escopo de `/* USER CODE BEGIN PV */`, declare as variáveis:

```

uint16_t data;

uint8_t complete = 0;

```

E incluir no escopo de `/* USER CODE BEGIN PFP */` os protótipos

```

uint16_t Read_Data(void);

uint8_t ADC_Complete(void);

```

7. Agora vamos implementar a ISR de fim de conversão e as funções para a interação com o código do arquivo “main.c”. No escopo de `/* USER CODE BEGIN 1 */`, implemente a função:

```

// ISR do ADC

void ADC_IRQHandler(void) {

if(ADC1->ISR & ADC_ISR_EOC) { // Flag de End Of Conversion

ADC1->ISR |= ADC_ISR_EOC; // Limpa flag

if (!complete) {

data = ADC1->DR; // Le o dado convertido

complete = 1; // Flag interno de dado disponível

}

}

}

```

E no escopo de `/* USER CODE BEGIN 0 */`, adicione as funções:

```

uint16_t Read_Data(void) {

complete = 0; // Apaga o flag interno na leitura do dado

return data;

}

uint8_t ADC_Complete(void) {

return complete;

}

```

As três funções são bastante simples, dispensando maiores comentários. Vale apenas destacar que, na ISR `ADC_IRQHandler`, **o conteúdo do registrador `ADC1->DR` deve ser armazenado em uma variável. Após cada conversão, o resultado é gravado nesse registrador, sobrescrevendo o valor da amostra anterior.** Portanto, cabe ao programador garantir que, **em cada conversão**, o conteúdo de `ADC1->DR` seja salvo para processamento posterior e controlar a sua sobrescrita. Neste projeto, implementou-se a estratégia de sobrescrever `data` somente após sua leitura; caso contrário, o valor convertido é descartado. Ademais, ao realizar um acesso de leitura deste registrador, o *bit* de estado de

ADC\_ISR\_EOC é resetado automaticamente pelo *hardware*, dispensando a necessidade de uma limpeza manual por *software*.

8. Por fim, vamos implementar o código dentro da função “main()”. Voltando ao arquivo “main.c”, no escopo de `/* USER CODE BEGIN 1 */`, declare um vetor para armazenar múltiplas amostras, uma variável auxiliar para definir o número da amostra, uma variável para acumular as amostras medidas (para cálculo da média de valores), uma para calcular a tensão correspondente à média, e uma para calcular a temperatura medida.

```

uint16_t adc[50];

uint8_t i;

uint32_t media;

float tensao, temp;

```

No escopo de `/* USER CODE BEGIN 2 */`, chame as funções de configuração do ADC e do *timer*:

```

Config_ADC();

Config_Timer();

```

9. Agora implemente o código que vai, a cada ciclo do *loop* principal, adquirir 50 amostras pelo ADC e guardá-las no vetor, calcular o valor médio do vetor, a tensão correspondente e a temperatura equivalente, e depois aguardar 1 segundo antes de reiniciar. Abaixo da linha `/* USER CODE BEGIN 3 */`, escreva o código:

```

media = 0;

Start_Conv();

for(i = 0; i < 50; i++) {

while(!ADC_Complete()) {}

adc[i] = Read_Data();

media += adc[i];

}

Stop_Conv();

media /= 50; // Faz a media das 50 amostras

tensao = (media * 3.3) / 65535.0;

// tensao = (10mV/C x temp) + 600mv

// invertendo: temp = (tensao - 600mv) / (10mV/C)

temp = (tensao - 0.6) / 0.01;

HAL_Delay(1000);

```

e coloque um *breakpoint* na linha do `HAL_Delay`. Faça o *Build*.

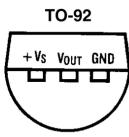

10. Conecte o sensor ao [conector H9](#), utilizando os pinos que foram referenciados com as mesmas denominações do projeto anterior. Ligue o terminal marcado com “+” (+Vs) no pino de 3.3V, o pino central (tensão de saída, Vout) no canal 4 e o último pino (GND) no canal 8 (configurado como um “terra” neste projeto). Opcionalmente, pode-se usar o pino 3 do CN10 (AGND) no lugar do canal 8.

## Pinagem do sensor LM61

Transfira o código executável para o microcontrolador e inicie a execução do código. Quando o programa parar no *breakpoint*, veja o conteúdo do vetor “adc”, o valor médio, e os valores de tensão média (“media”) e de temperatura média (“temp”). Aqueça o sensor na mão e retome a execução. Veja novamente o conteúdo das variáveis.

11. Como os valores de “adc” e “tensao” foram calculados neste projeto? Compare o procedimento adotado aqui com o método aplicado no segundo projeto. Observe que a fórmula utilizada para obter “temp” neste projeto foi derivada do [datasheet do sensor de temperatura LM61](#). Qual é a finalidade desta segunda fórmula?

12. Ao contrário do segundo projeto, as conversões neste projeto são disparadas por sinais provenientes do *timer* TIM6. Em comparação com o segundo projeto, onde as conversões são iniciadas por *software*, quais configurações adicionais são necessárias para associar o canal 4 (PC4) à entrada do ADC1, configurar o ADC1 a operar no modo de disparo por *hardware* e o TIM6 como fonte desses disparos de inicialização de conversões? Praticaremos neste Roteiro essas configurações.

13. Como realizar conversões periódicas, análogas a este projeto, em microcontroladores que possuem temporizadores periódicos e um *hardware* de conversão com suporte exclusivo para iniciação via *software* e eventos de interrupção de fim de conversão? Considerando essa limitação de *hardware*, quais seriam os desafios de implementação em *software* para garantir a periodicidade desejada? Que mecanismos e lógicas adicionais seriam necessários, e como eles impactariam a complexidade e o consumo de recursos do *software* em comparação com uma solução com disparo de conversão por *hardware*? No entanto, a vantagem de um *software* mais limpo, conciso e de fácil manutenção pode implicar uma maior complexidade na configuração de um *hardware* intrinsecamente mais potente, flexível, eficiente e preciso. Vamos explorar juntos essa complexidade e aprender domá-la?

## Projeto de conversão DAC com DMA

No primeiro projeto-exemplo, demonstramos uma técnica de conversão periódica de amostras digitais em valores analógicos, utilizando as interrupções periódicas de um temporizador para controlar a taxa de transferência das amostras para o conversor. A cada interrupção, uma nova amostra digital era calculada para conversão. Agora, exploraremos uma abordagem direta para transferir amostras digitais pré-calculadas para o DAC através do controlador DMA (do inglês *Direct Memory Access*), com a taxa de transferência ainda controlada pelo temporizador, mas sem a necessidade de tratamento dos seus eventos de interrupção pelo núcleo do processador. Especificamente, armazenaremos todas as amostras da forma de onda senoidal num espaço contíguo da memória e configuraremos o *hardware* para transferi-las sequencialmente para o conversor DAC, dispensando a intervenção da CPU.

1. Crie um novo projeto do tipo “STM32 Project from an Existint STM32CubeMX Configuration File (.ioc)” usando o *Cube*, a partir do “File” <caminho>/DAC\_basico.ioc com o “Project Name” “DAC\_DMA”. Gere o código que terá a mesma configuração básica do primeiro projeto-exemplo.

2. Vamos definir o vetor que irá guardar as amostras da senóide como variável global no escopo de `/* USER CODE BEGIN PV */`, pois ele deve ser acessível a partir da função “main” e também pela função de configuração do DMA:

```

uint32_t sine_wave[SAMPLES]; // Amostras da senoide

```

3. Vamos adicionar configuração do DMA no escopo de `/* USER CODE BEGIN PFP */`

```

void Config_Timer(void);

```

4. Dentro da função main, vamos montar o vetor de amostras da senóide no vetor sine\_wave declarado dentro do escopo de `/* USER CODE BEGIN 1 */`:

```

uint8_t i;

int8_t step = 0;

int8_t direction = 1; // 1 para subir, -1 para descer

uint32_t dac_value;

```

```

// Inicializa o vetor de valores na memoria

// a serem transferidos para DAC via DMA

for(i = 0; i < SAMPLES; i++) {

sine_wave[i] = (uint32_t)(OFFSET + (OFFSET * sin(2 * PI * i / SAMPLES)));

if(sine_wave[i] > DAC_MAX_VALUE) {

sine_wave[i] = DAC_MAX_VALUE;

}

}

```

Observe que foi removida a variável sine\_wave declarada no primeiro projeto.

5. No escopo de `/* USER CODE BEGIN 2 */`, insira a chamada da função que configura DMA:

```

Config_DMA();

```

6. No laço infinito, removeremos os cálculos das amostras da senóide e suas transferências para DAC no escopo de `/* USER CODE BEGIN 3 */`. A versão final é:

```

if (leFlag()) {

// Reseta flag

resetFlag();

// Calcular o proximo valor da onda triangular

step += direction;

// Verificar limites da onda triangular (0 a 4095)

if (step >= 50) {

direction = -1; // Começar a descer

step = 50;

} else if (step <= 0) {

direction = 1; // Começar a subir

step = 0;

}

// Ajustar o valor para escala de 12 bits (4096 níveis)

dac_value = (step * 4095) / 50;

// Atualizar o valor do DAC1_OUT2

DAC1->DHR12R2 = dac_value; // PA5

}

```

7. O que precisamos adicionar é a função de configuração do DMA no escopo de `/* USER CODE BEGIN 4 */`, seguindo o procedimento fornecido pelo fabricante:

**void Config\_DMA(void)** {

```

uint32_t endreg, endvetor;

endreg = (uint32_t)&(DAC2->DHR12R1); // Endereco do registrador de

DAC2 onde se carrega o valor de 12 bits para o canal 1

endvetor = (uint32_t)sine_wave; // Endereco inicial do vetor com a

senoide

```

```

// TIM7_UP está na entrada de requisição 70 de DMAMUX1 (Tabela 101 do

RM)

// Saída DMAMUX1 canal 1 ligada a request de DMA1 canal 1 (seção

17.3.2 do RM)

RCC->AHB1ENR |= RCC_AHB1ENR_DMA1EN; // Habilitar clock do DMA1

// RM seção 17.4.3 mostra a sequência para se configurar o DMA e

DMAMUX

DMA1_Stream1->CR = 0; // Inicia CR com bits zerados

DMA1_Stream1->MOAR = endvetor; // Endereço da origem

DMA1_Stream1->PAR = endreg; // Endereço destino

DMA1_Stream1->NDTR = SAMPLES; // Número de transferências

DMA1_Stream1->CR |= DMA_SxCR_PL | // Prioridade máxima

DMA_SxCR_MSIZE_1 | // Elemento da memória de 32 bits

DMA_SxCR_PSIZE_1 | // Registrador de periférico de 32

bits

DMA_SxCR_MINC | // Incrementa memória

DMA_SxCR_CIRC | // Buffer circular

DMA_SxCR_DIR_0; // Da memória para o periférico

DMAMUX1_Channel1->CCR |= (DMAMUX_CxCR_DMAREQ_ID_6 |

DMAMUX_CxCR_DMAREQ_ID_2 | // Associa a request 70=0b0100 0110

DMAMUX_CxCR_DMAREQ_ID_1 ); // (TIM7 UP) ao canal 1 do DMAMUX1

DMA1_Stream1->CR |= DMA_SxCR_EN; // Habilita Canal 1 do DMA1

}

```

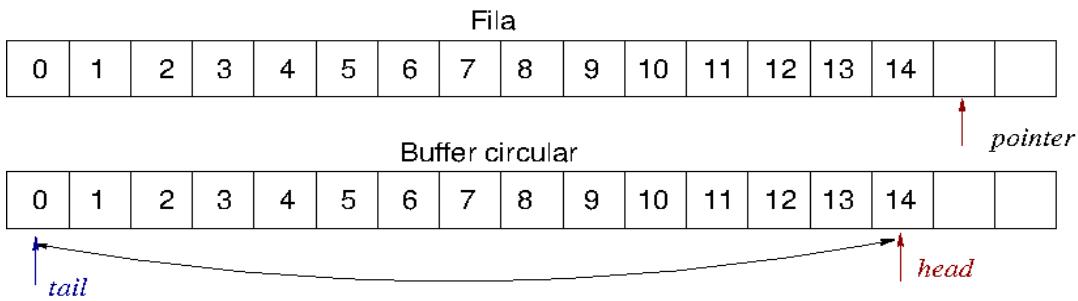

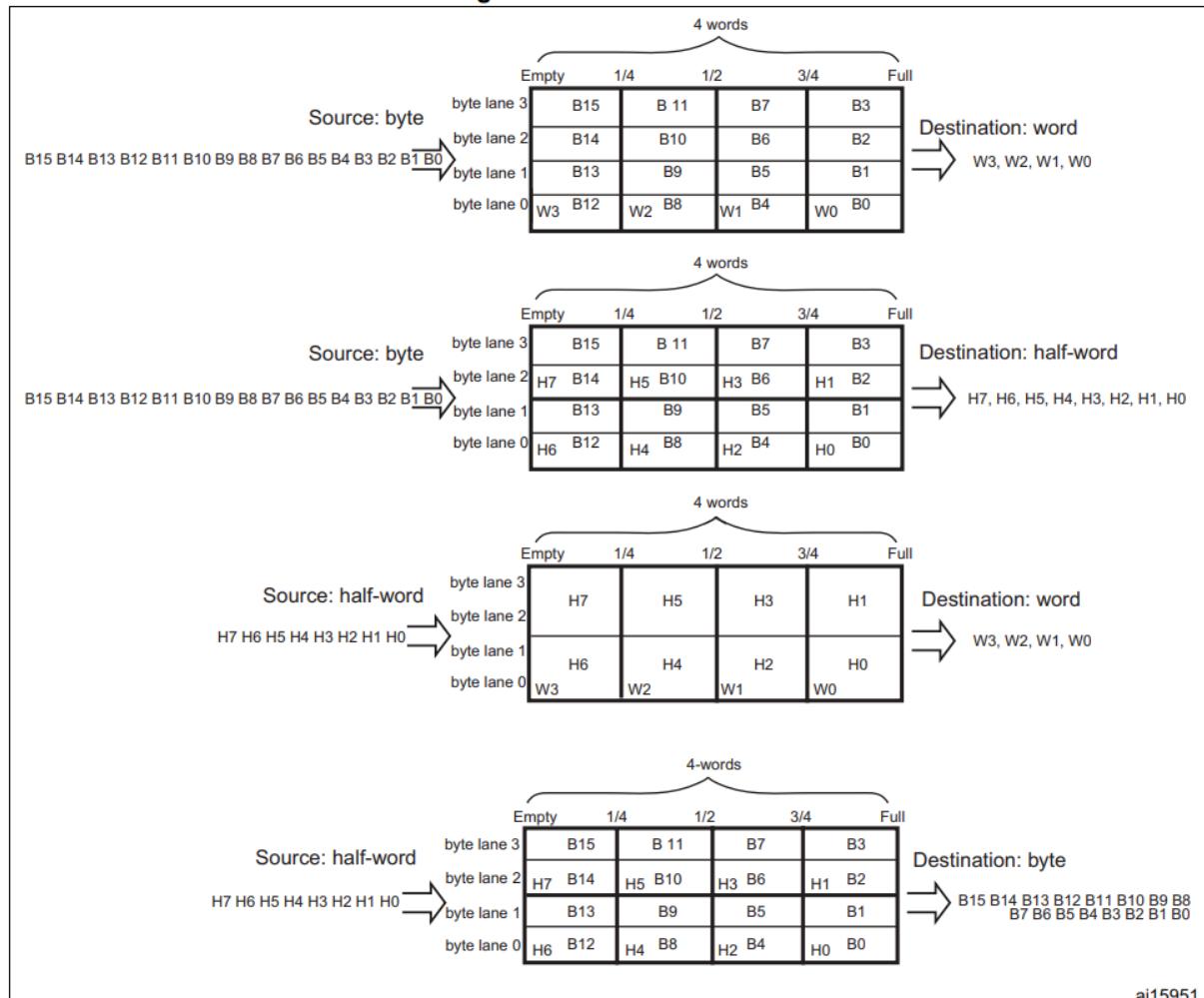

Aqui configuramos a *stream* (ou canal) 1 do DMA1 com o endereço de origem dos dados (no caso a memória) sendo o endereço da primeira amostra do vetor da senóide. O endereço de destino dos dados é o registrador DHR12R1, que recebe o valor digital a ser convertido. “R1” indica que o canal usado é o 1, e que os dados estão alinhados à direita (“R”). Também definimos o número de transferências a ser executado (no caso são 100 amostras), e depois fazemos a configuração geral: Prioridade máxima, transferências em 32 *bits* (apesar de usar 12 *bits*, os registradores de dados do DAC são de 32 *bits*), com incremento da posição na memória após cada transferência (para “varrer” o vetor), sem incrementar o endereço do destino (o registrador de dados não “avança” o endereço), transferências da memória para o periférico e *buffer* circular (ao terminar a transferência, o endereço de origem volta ao valor inicial).

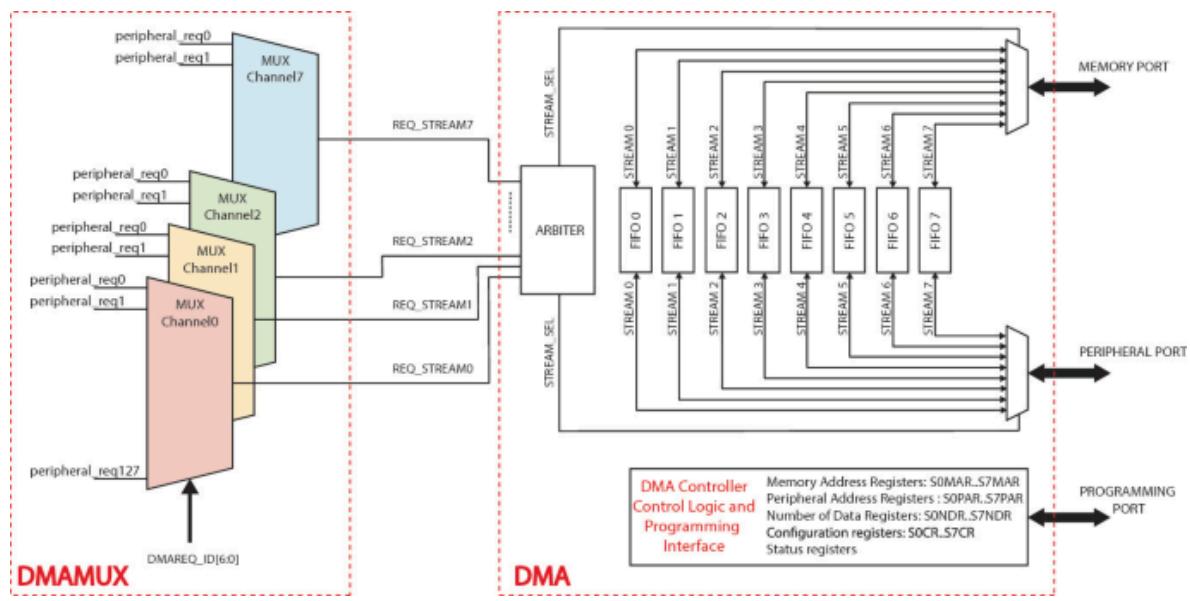

O registrador DMAMUX1\_Channel1 é um registrador de configuração do multiplexador do canal 1 do controlador DMA1, usado para rotear dados entre a memória e o registrador de dados do canal 1 do DAC2. Foi configurada a fonte de evento número 70 (*update* do *timer* 7), correspondente ao evento de *update* do TIM7, como *trigger* do canal 1 do DMA1. Assim, a cada *update* do TIM7, o canal 1 do DMA1 transfere uma amostra do vetor *sine\_wave*, localizado na memória, para o registrador de dados do canal 1 de DAC2. O modo circular está habilitado, de modo que ao atingir a centésima amostra, o *hardware* reinicia automaticamente o ciclo a partir da primeira amostra.

8. Agora vamos atualizar a função de configuração do *timer* TIM7 para habilitar a requisição do controlador DMA na ocorrência do evento de Update. Segue-se a nova versão com a inclusão da instrução de habilitação “`TIM7->DIER |= TIM_DIER_UDE;`”:

```

void Config_Timer(void) {

// Enable clock for TIM6 e TIM7

RCC->APB1LENR |= RCC_APB1LENR_TIM6EN | RCC_APB1LENR_TIM7EN;

// TIM7: Faz interrupção periódica

TIM7->EGR |= TIM_EGR_UG_Msk;

while (TIM7->EGR & TIM_EGR_UG);

TIM7->CR1 = 0;

TIM7->PSC = 64 - 1; // Dividir clock por 64 -> 1MHz

TIM7->ARR = 20 - 1; // Contar até 20 -> 50kHz

TIM7->CR1 = 0; // Registradores de controle inicialmente zerados

TIM7->CR2 = 0;

TIM7->DIER |= TIM_DIER_UIE; // Habilitar interrupção de update (UIE)

TIM7->DIER |= TIM_DIER_UDE; // Habilitar requisição de DMA em evento

de atualização

TIM7->CR1 |= TIM_CR1_CEN; // Start timer

// Configurar prioridade da interrupção de TIM7 e habilitar no NVIC

NVIC_SetPriority(TIM7_IRQn, 1);

NVIC_EnableIRQ(TIM7_IRQn);

}

```

9. Após as atualizações, faça um *Build* e transfira o código executável para o microcontrolador. Conecte as pontas de prova do **osciloscópio** nos pinos 1 e 2 do [conector H8](#) (DAC) e ligue o terra do **osciloscópio** no pino 3 do mesmo conector, como no primeiro projeto para visualizar as duas formas de onda geradas.

10. Reavalie os testes de validação executados no primeiro projeto e compare os resultados com os obtidos nesta nova implementação. Note que a primeira implementação dependia da intervenção da CPU para transferir cada amostra individualmente, enquanto nesta, a CPU apenas inicia a contagem do temporizador TIM7, delegando a transferência cíclica das amostras ao *hardware* (controlador DMA1).

Em termos de periféricos, realize uma análise comparativa dos recursos utilizados em ambas as abordagens. No que concerne ao código, investigue as diferenças nos fluxos de controle, nas configurações dos periféricos e na proporção de responsabilidade entre *software* e *hardware* na geração das respectivas formas de onda. Caso não tenha uma resposta clara no momento, não se preocupe, retomaremos este ponto posteriormente.

11. A partir dessas comparações, você consegue discernir o papel fundamental do controlador DMA e do multiplexador DMAMUX? Ao transferir a responsabilidade da transferência de dados para esses componentes de *hardware* especializados, o benefício obtido em relação a uma implementação puramente via *software* supera a complexidade adicional na configuração desses *hardwares*? Vamos aprofundar nossa compreensão desses elementos de *hardware* para otimizar seu uso?

12. Em um sistema onde o *timer* TIM7 dispara requisições DMA a uma frequência excessivamente alta, excedendo a capacidade de processamento individual de cada requisição, o que leva a eventos de subcarga (em inglês, *underrun*), como o DMA lidará com essa situação? As requisições subsequentes serão descartadas ou existe algum mecanismo de tratamento para essa condição de alta frequência? Abordaremos essa questão adiante.

13. Em uma transferência DMA configurada em modo circular para leitura contínua de um *buffer* na memória, o DMA retorna automaticamente ao início ao alcançar o final do *buffer*. Considerando que o vetor *sine\_wave* é atualizado sequencial e dinamicamente, se o processamento dos dados pela CPU for mais rápido que a taxa de leitura do DMA, o que acontecerá com os dados recém-atualizados? Eles serão enfileirados em outro *buffer* para aguardar processamento? Como podemos garantir a integridade dos dados nesse cenário? A resposta será explorada adiante.

## Projeto de conversor A/D disparado por *hardware*, com DMA

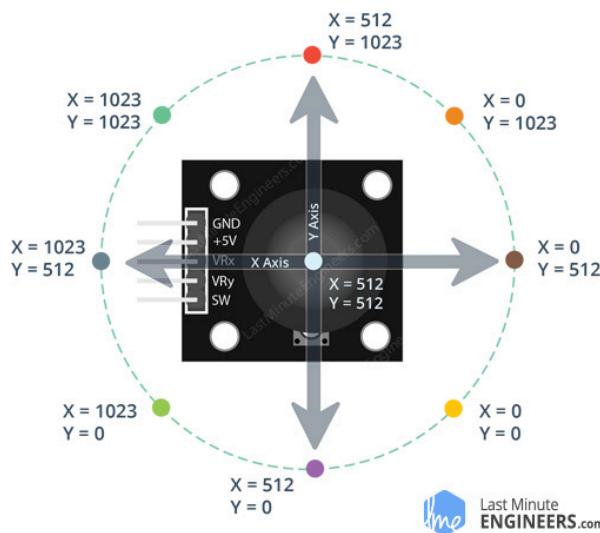

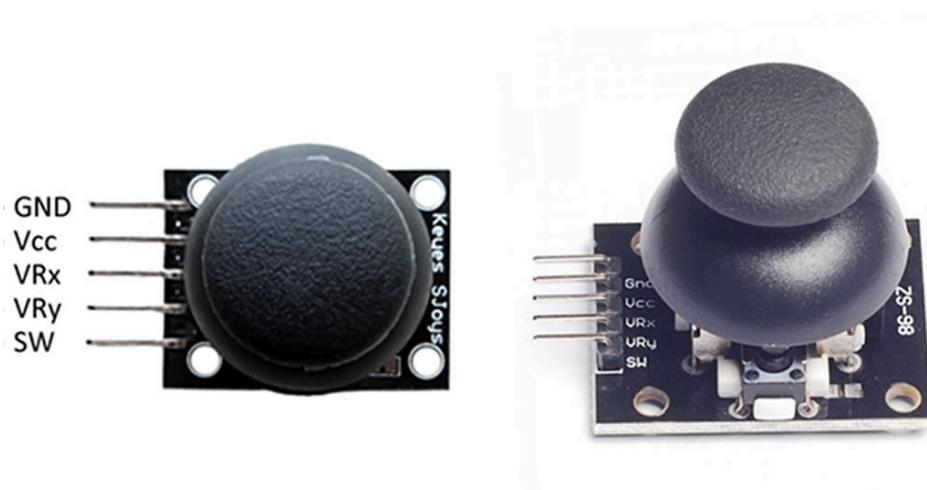

Imagine um projeto em que você possa captar movimentos em tempo real usando um [joystick](#), coletando informações sobre deslocamentos nos eixos X e Y. No terceiro projeto, a CPU enfrentou um “gargalo” ao interromper seu fluxo de execução para processar os dados convertidos pelo ADC. Essa abordagem limita a velocidade de conversão e pode prejudicar a responsividade do sistema, especialmente quando lidamos com taxas de amostragem elevadas. Agora, vamos elevar nosso projeto a um novo patamar! Utilizando o recurso de DMA (*Direct Memory Access*), poderemos automatizar a transferência dos dados convertidos para um *buffer*, sem a necessidade de intervenção da CPU. Além disso, vamos configurar o ADC para converter múltiplos canais, sequenciando automaticamente as leituras. Essa abordagem não apenas aprimorará a eficiência, mas também abrirá um leque de possibilidades para explorar diferentes sensores ou fontes de dados.

1. Crie um novo projeto usando o *Cube*, com o nome “ADC\_Joystick”, **sem inicializar os periféricos**. Ative o *Debug* e gere o código, mantendo o *clock* padrão de 64MHz.

2. Como nos projetos anteriores, vamos criar algumas funções, sendo uma para configurar o ADC, uma para configurar o *timer*, uma para configurar o DMA, uma para iniciar as conversões periódicas e outra para parar as conversões. Além disso, dentro do arquivo “stm32h7xx\_it.c” vamos criar apenas uma função para indicar se há resultado novo no ADC, já que os valores obtidos serão transferidos ao *buffer* diretamente pelo DMA. Por ser uma função definida no outro arquivo, precisamos prototipá-la no arquivo “main.c”. No escopo de `/* USER CODE BEGIN PFP */`, crie os protótipos das funções:

```

void Config_Timer(void);

void Config_ADC(void);

void Config_DMA(void);

void Start_Conv(void);

void Stop_Conv(void);

uint8_t Frame_Complete(void);

void Reset_FrameComplete (void);

```

3. No escopo de `/* USER CODE BEGIN 4 */`, vamos implementar as cinco primeiras funções, começando com a de configuração de *timer*:

```

void Config_Timer(void) {

RCC->APB1LENR |= RCC_APB1LENR_TIM6EN; // Habilita clock de TIM6

TIM6->EGR |= TIM_EGR_UG_Msk; // atualizacao inicial dos

registradores

while (TIM6->EGR & TIM_EGR_UG);

TIM6->CR1 &= ~TIM_CR1_CEN; // Desabilita o contador

TIM6->PSC = 63999; // Prescaler, assumindo clock de 64 MHz, timer a 1

kHz

TIM6->ARR = 49; // Periodo do timer: 1kHz / 50 = 20Hz

TIM6->CR2 &= ~TIM_CR2_MMS;

TIM6->CR2 |= TIM_CR2_MMS_1; // MMS[2:0] = 010: Update Event

}

```

Esta função é similar à do terceiro projeto, exceto pelo período de *trigger*, que agora é de 20Hz, pois iremos ler dois canais e cada *trigger* inicia a conversão de um deles.

4. Na sequência, vamos implementar a função de configuração do ADC:

```

void Config_ADC(void) {

//Configurar PC4 e PC5 como analog

RCC->AHB4ENR |= RCC_AHB4ENR_GPIOCEN;

GPIOC->MODER |= GPIO_MODER_MODE4 | GPIO_MODER_MODE5;

// Habilitar o clock do ADC1

RCC->AHB1ENR |= RCC_AHB1ENR_ADC12EN;

// Resetar o ADC1 (garantir que o ADC esteja desabilitado antes de

configurar)

if (ADC1->CR & ADC_CR_ADEN) {

ADC1->CR |= ADC_CR_ADDIS; // Desabilitar o ADC se já estiver

habilitado

while (ADC1->CR & ADC_CR_ADEN); // Aguardar até o ADC ser

desabilitado

}

ADC1->CR = 0;

// Desabilitar o deep power down

ADC1->CR &= ~ADC_CR_DEEPPWD;

// Habilitar o regulador de tensão do ADC (modo intermediário)

ADC1->CR |= ADC_CR_ADVREGEN;

// Aguardar estabilização do regulador de tensão do ADC

while (!(ADC1->ISR & ADC_ISR_LDORDY));

// Definir a fonte de ADC clock: clock do sistema/2 (64MHz/2)

// O registrarador eh comum para os 2 modulos

ADC12_COMMON->CCR &= ~(ADC_CCR_CKMODE);

ADC12_COMMON->CCR |= ADC_CCR_CKMODE_1;

// Calibrar o ADC1 (modo de entrada única)

ADC1->CR &= ~ADC_CR_ADCALDIF; // Garantir que a calibração seja no

modo single-ended

ADC1->CR |= ADC_CR_ADCAL; // Iniciar calibração

```

```

while (ADC1->CR & ADC_CR_ADCAL); // Auardar fim da calibração

// Após a calibração, auardar a estabilização do ADC

for(int i = 0; i < 10000; i++);

// Configurar o ADC1 para conversão nos canais 4 e 8

ADC1->SQR1 = 0;

ADC1->SQR1 &= ~ADC_SQR1_L; // Configuração para conversão de

2 canais

ADC1->SQR1 |= ADC_SQR1_L_0;

ADC1->SQR1 |= (ADC_SQR1_SQ1_2 | // Selecionar canal 4 na sequência

regular (PC4)

ADC_SQR1_SQ2_3); // Selecionar canal 8 na sequência

regular (PC5)

// Configurar o tempo de amostragem dos canais

ADC1->SMPR1 &= ~(ADC_SMPR1_SMP4 | ADC_SMPR1_SMP8); // Limpar

configurações anteriores

ADC1->SMPR1 |= (ADC_SMPR1_SMP4_0 |

ADC_SMPR1_SMP8_0); // Amostragem de 2.5 ciclos de ADC

// Pre-selecionar os canais

ADC1->PCSEL |= (ADC_PCSEL_PCSEL_4 |

ADC_PCSEL_PCSEL_8); // Pre-seleciona canais 4, 8

// Configurar a resolução (16 bits)

ADC1->CFGR &= ~ADC_CFGR_RES;

// Configurar o ADC para disparo externo pelo TIM6 Update Event

// Reference Manual, Tabelas 194 e 196.

ADC1->CFGR &= ~(ADC_CFGR_EXTSEL | ADC_CFGR_EXTEN); // Limpar

configuração anterior de trigger

ADC1->CFGR |= (ADC_CFGR_EXTSEL_3 |

ADC_CFGR_EXTSEL_2 |

ADC_CFGR_EXTSEL_0); // EXTSEL = 01101 para TIM6 Update

Event

ADC1->CFGR |= ADC_CFGR_EXTEN_0; // Habilitar trigger em borda de

subida (EXTEN = 01)

//Habilitar DMA modo circular

ADC1->CFGR |= ADC_CFGR_DMNGT; //DMA (modo 0b11)

// Habilitar o ADC1

ADC1->ISR |= ADC_ISR_ADRDY; // Limpar flag de prontidão

ADC1->CR |= ADC_CR_ADEN; // Habilitar ADC1

while (!(ADC1->ISR & ADC_ISR_ADRDY)); // Auardar até o ADC estar

pronto

//Iniciar conversões

ADC1->CR |= ADC_CR_ADSTART;

}

```

Esta também é análoga à do terceiro projeto, exceto que agora vamos converter 2 canais ao invés de um. O pino PC5 também é configurado como analógico, correspondendo ao canal 8 do ADC1. Veja a última coluna da tabela a seguir.

| Pin/ball name <sup>(1) (2)</sup> |                    |                   |                     |                     |                        |                   |                    |        |          |         |         |              |         |          |  |     | Pin name<br>(function<br>after reset) | Pin<br>type | I/O<br>structure                                                                                                                                                               | Alternate functions                       | Additional<br>functions |

|----------------------------------|--------------------|-------------------|---------------------|---------------------|------------------------|-------------------|--------------------|--------|----------|---------|---------|--------------|---------|----------|--|-----|---------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------|

| LQFP100 with SMPS                | TFBGA100 with SMPS | LQFP144 with SMPS | WL CSP132 with SMPS | UF BGA169 with SMPS | UF BGA176+25 with SMPS | LQFP176 with SMPS | TFBGA225 with SMPS | LQFP64 | TFBGA100 | LQFP100 | LQFP144 | UF BGA176+25 | LQFP176 | TFBGA216 |  |     |                                       |             |                                                                                                                                                                                |                                           |                         |

| 34                               | K3                 | 46                | K9                  | J6                  | N6                     | 52                | R5                 | 23     | K3       | 31      | 43      | R3           | 53      | R3       |  | PA7 | I/O                                   | FT_ah1      | TIM1_CH1N,<br>TIM3_CH2,<br>TIM8_CH1N,<br>DFSDM2_DATIN1,<br>SPI1_MOSI/I2S1_SDO,<br>SPI6_MOSI/I2S6_SDO,<br>TIM14_CH1,<br>OCTOSPI_M1_IO2,<br>FMC_SDNWE,<br>LCD_VSYNC,<br>EVENTOUT | ADC12_INP7,<br>ADC12_INN3,<br>OPAMP1_VINM |                         |

| 35                               | H4                 | 47                | H7                  | K6                  | R6                     | 53                | M6                 | 24     | G4       | 32      | 44      | N5           | 54      | N5       |  | PC4 | I/O                                   | FT_a        | DFSDM1_CKIN2,<br>I2S1_MCK,<br>SPDIFRX1_IN2,<br>FMC_SDNE0,<br>LCD_R7, EVENTOUT                                                                                                  | ADC12_INP4,<br>OPAMP1_VOUT,<br>COMP1_INM  |                         |

| 36                               | J4                 | 48                | J8                  | N5                  | M7                     | 54                | N6                 | 25     | H4       | 33      | 45      | P5           | 55      | P5       |  | PC5 | I/O                                   | FT_ah1      | SA1_D3,<br>DFSDM1_DATIN2,<br>PSSI_D15,<br>SPDIFRX1_IN3,<br>OCTOSPI_M1_DQ5,<br>FMC_SDCKE0,<br>COMP1_OUT,<br>LCD_DE, EVENTOUT                                                    | ADC12_INP8,<br>ADC12_INN4,<br>OPAMP1_VINM |                         |

Os *bits* ADC\_SQR1\_L do registrador [ADC\\_SQR1](#) definem o comprimento da sequência de conversão, correspondendo ao número de conversões menos 1. Em projetos anteriores, esses *bits* eram configurados como 0000, indicando uma única conversão. Neste caso, são ajustados para 0001, o que equivale a duas conversões sequenciais. A seleção dos canais que compõem a sequência é feita por meio dos *bits* ADC\_SQRx\_SQy nos registradores ADC1\_SQR1 a ADC1\_SQR4 (com  $x = 1$  a 4), onde cada campo SQy define o canal a ser convertido na posição  $y$  da sequência. Neste projeto, configuramos os campos ADC\_SQR1\_SQ1 e ADC\_SQR1\_SQ2 para selecionar [os canais 4 e 8](#), respectivamente. Além disso, é necessário habilitar previamente todos os canais utilizados no registrador ADC1\_PCSEL, que controla a pré-seleção dos canais permitidos para conversão. Por fim, para otimizar a transferência de dados, configure o campo DMNGT no registrador [ADC1\\_CFGR](#) para habilitar a integração com o controlador DMA. Essa configuração permite que o ADC1 gere automaticamente uma requisição de DMA ao final de cada conversão ou sequência, dependendo do modo operacional. Neste cenário específico, o modo DMA com *buffer* circular está ativado.

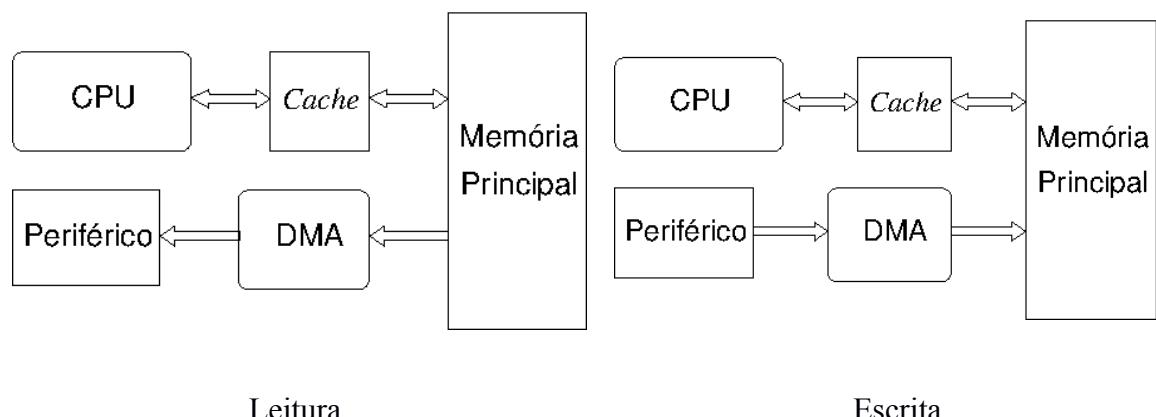

Além disso, a **interrupção para o evento EOC (do inglês *End Of Conversion*) não foi habilitada para o armazenamento dos valores do registrador ADC1->DR**, pois o controlador DMA assumirá este gerenciamento. Veremos mais adiante que **o controlador DMA é configurado para transferir automaticamente o conteúdo do registrador ADC1->DR para o vetor adc assim que um novo valor é registrado, sem a necessidade de intervenção da CPU**. Essa abordagem simplifica a programação do controle de fluxo de dados.

É importante observar a diferença entre o DMA e o NVIC. Enquanto o **DMA opera de forma totalmente independente do núcleo** durante a maior parte do processo de

transferência de dados, movendo blocos de informação entre periféricos e memória sem intervenção da CPU, o **NVIC** é o responsável por gerenciar as interrupções que *são processadas pelo núcleo*.

5. Precisamos ainda configurar o DMA. Logo após as funções anteriores, implemente a função correspondente:

```

void Config_DMA(void) {

uint32_t endreg, endvetor;

endreg = (uint32_t)&(ADC1->DR); // Endereco do registrador de dados

ADC1

endvetor = (uint32_t)adc; // Endereco inicial do vetor de dados

// ADC1 está na entrada de requisição 9 de DMAMUX1 (Tabela 101 do RM)

// Saida DMAMUX1 canal 1 ligada a request de DMA1 canal 1 (secao

17.3.2 do RM)

RCC->AHB1ENR |= RCC_AHB1ENR_DMA1EN; // Habilitar clock do DMA1

// RM secao 17.4.3 mostra a sequencia para se configurar o DMA e

DMAMUX

DMA1_Stream1->CR = 0; // Inicia CR com bits zerados

DMA1_Stream1->MOAR = endvetor; // Endereco da destino

DMA1_Stream1->PAR = endreg; // Endereco de origem

DMA1_Stream1->NDTR = SAMPLES; // Numero de transferencias

DMA1_Stream1->CR |= DMA_SxCR_PL | // Prioridade maxima

DMA_SxCR_MINC | // Incrementa memoria

DMA_SxCR_CIRC | // Buffer circular

DMA_SxCR_TCIE; // Interrupcao de transfer complete

// Do periferico para a memoria (DIR = 00)

DMA1_Stream1->CR &= ~DMA_SxCR_MSIZE_Msk;

DMA1_Stream1->CR |= DMA_SxCR_MSIZE_0; // Elemento da memoria de 16

bits

DMA1_Stream1->CR &= ~DMA_SxCR_PSIZE_Msk;

DMA1_Stream1->CR |= DMA_SxCR_PSIZE_0; // Elemento da periferico de 16

bits

//Configurar interrupcao de TC prioridade 1

NVIC_SetPriority(DMA1_Stream1_IRQn, 1); // Configura NVIC para

interrupcoes do DMA

NVIC_EnableIRQ(DMA1_Stream1_IRQn);

DMAMUX1_Channel1->CCR = (DMAMUX_CxCR_DMAREQ_ID_0 |

DMAMUX_CxCR_DMAREQ_ID_3); // Associa a request 9 ao canal

1 do DMAMUX1

DMA1_Stream1->CR |= DMA_SxCR_EN; // Habilita Canal 1 do DMA1

}

```

A configuração do DMA nesta função apresenta semelhanças com o projeto anterior, embora com algumas distinções importantes. Primeiramente, os endereços de memória do vetor (adc) e do registrador de dados do periférico (ADC1->DR) são distintos, assim como a fonte de requisição. O número de amostras a serem transferidas coincide com o projeto anterior. Adicionalmente, a configuração do registrador DMA1\_Stream1->CR difere: os *bits* de direção da transferência (DIR=0b00) agora especificam uma transferência do periférico para a

memória, ao invés de memória para periférico (DIR=0b01). Além disso, o tamanho das amostras, tanto na memória quanto no periférico, foi ajustado para 16 *bits*, substituindo a configuração anterior de 32 *bits*. Por fim, o multiplexador (MUX) do DMA é configurado para associar o canal 1 à [fonte de requisição número 9](#), correspondente ao ADC1 (conforme a Tabela 101 do Manual de Referência), para transferir dados do ADC para a memória. Em contraste com o projeto anterior, onde o *timer* TIM7 requisitava um canal DMA para transferir dados da memória para o DAC.

Cabe ressaltar que quando um periférico, como o DMA, precisa sinalizar um evento para o núcleo (por exemplo, a conclusão de uma transferência de dados), ele gera um pedido de interrupção. Esse pedido é então gerenciado pelo NVIC, que determina a prioridade e direciona o núcleo para executar a rotina de tratamento de interrupção (ISR) correspondente. Portanto, embora o DMA realize a transferência de dados de forma autônoma, a *notificação* e o *tratamento* de eventos relacionados ao DMA (como a conclusão da transferência) envolvem a ativação do NVIC e a execução de código pelo núcleo. Neste projeto, a interrupção de transferência completa do DMA é habilitada com prioridade 1 no NVIC. Essa colaboração permite que o sistema reaja de forma eficiente aos eventos gerados pelos periféricos, mesmo com a transferência de dados ocorrendo em paralelo.

6. As funções “Start\_Conv” e “Stop\_Conv” são idênticas às do terceiro projeto, podendo ser copiadas. Elas são responsáveis por iniciar periodicamente uma conversão no ADC1 com os seus eventos de *Update*.

7. Vamos agora implementar a função do arquivo “stm32h7xx\_it.c”. Inicialmente, vamos definir uma variável no escopo do arquivo para auxiliar na função. No escopo de `/* USER CODE BEGIN PV */`, declare a variável:

```

uint8_t complete = 0;

```

E no escopo de `/* USER CODE BEGIN PFP */`, os protótipos das funções

```

uint8_t Frame_Complete(void);

void Reset_FrameComplete (void);

```

8. Agora vamos implementar a ISR de fim de transferência DMA e a função para a interação com o código do arquivo “main.c”. No escopo de `/* USER CODE BEGIN 1 */`, implemente as funções:

```

void DMA1_Stream1_IRQHandler(void) {

if(DMA1->LISR & DMA_LISR_TCIF1) { // Flag de transfer complete

DMA1->LIFCR |= DMA_LIFCR_CTCIF1; // Limpa flag

complete = 1;

}

}

```

E no escopo de `/* USER CODE BEGIN 0 */`

```

uint8_t Frame_Complete(void) {

```

```

uint8_t c;

c = complete;

return c;

}

void Reset_FrameComplete (void) {

complete = 0;

}

```

A ISR opera de maneira similar ao terceiro projeto. A principal diferença reside na atualização da *flag* `complete`, que só assume o valor 1 após a transferência de todas as amostras (100 no total, sendo 50 por canal) para a área de memória `adc`. Essa área é sobreescrita em blocos nas transferências subsequentes. Ao contrário do terceiro projeto, que descartava novas conversões se data não tivesse sido lido, neste projeto a sobreescrita é incondicional após um atraso de aproximadamente 1000ms. Esse atraso ocorre quando o *timer* `TIM6` é reativado e a *flag* `complete` é resetada para 0.

9. Voltando ao arquivo “`main.c`”, vamos implementar o código principal. Inicialmente, precisamos de um vetor para armazenar os dados convertidos. Este vetor deve ser global, pois precisa ser visível na função de configuração do DMA. No escopo de `/* USER CODE BEGIN PV */`, declare a variável:

```

uint32_t adc[SAMPLES];

```

e lembre-se de definir o número de amostras no escopo de `/* USER CODE BEGIN PD */`:

```

#define SAMPLES 100

```

10. Dentro da função “`main()`”, no escopo de `/* USER CODE BEGIN 2 */`, chame as funções de configuração:

```

Config_DMA();

Config_ADC();

Config_Timer();

```

11. Finalmente, vamos definir o código do *loop* principal. Abaixo da linha `/* USER CODE BEGIN 3 */`, escreva o código:

```

Start_Conv();

Reset_FrameComplete(); //Resetar o buffer

while(!Frame_Complete()) {} //Aguardar o preenchimento

Stop_Conv();

HAL_Delay(1000);

```

e coloque um *breakpoint* na linha do `HAL_Delay`. Faça um *Build* no programa.

12. Adicione a conexão do outro eixo do *joystick* ao canal 8 do ADC, de acordo com a figura já apresentada no segundo projeto. Observe que o pino +5V do *joystick* deve ser conectado

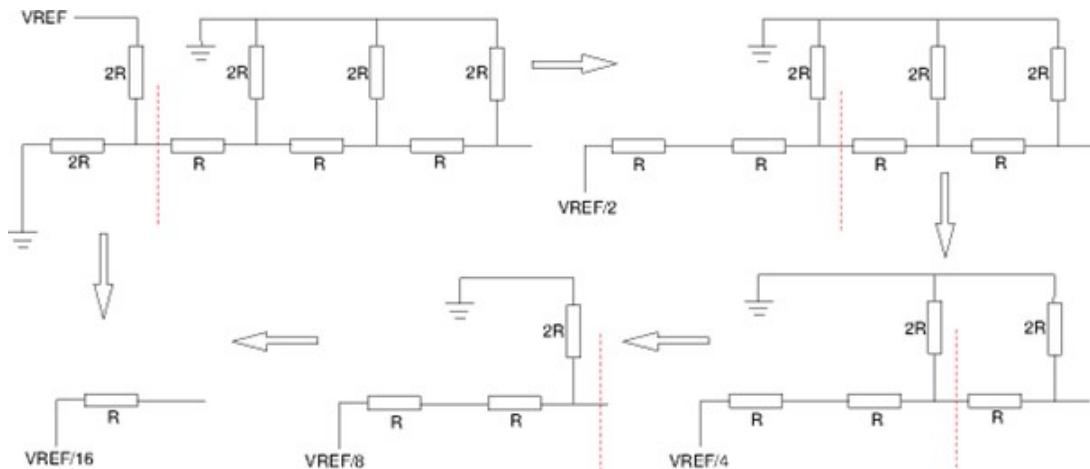

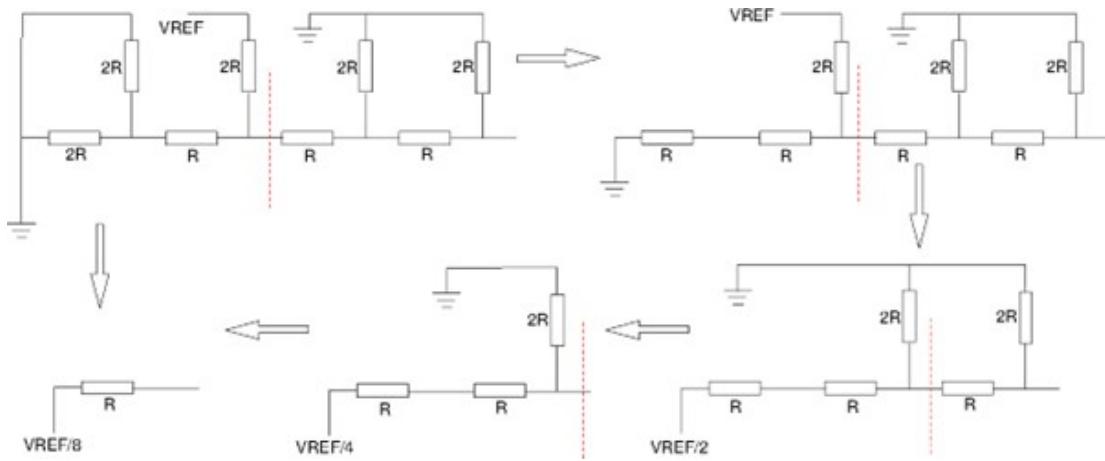

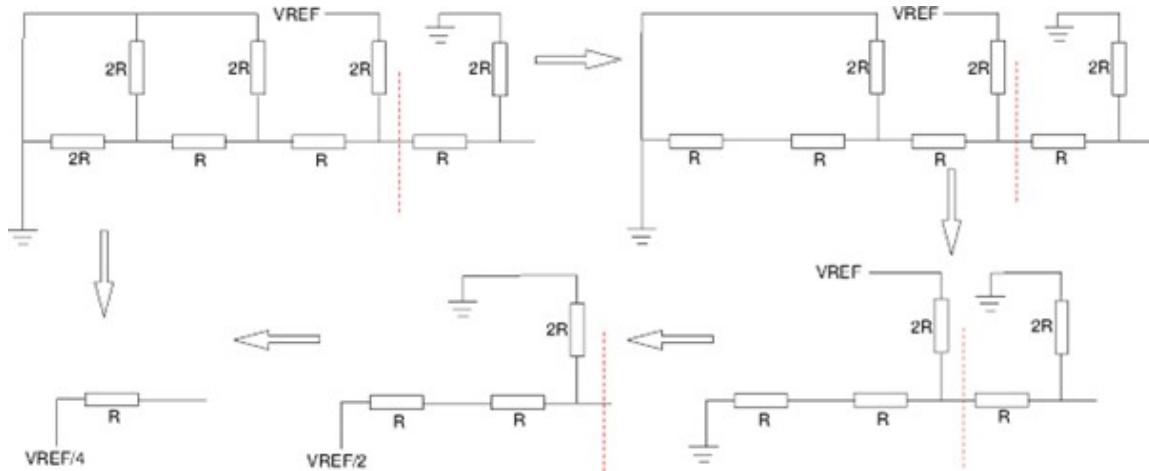

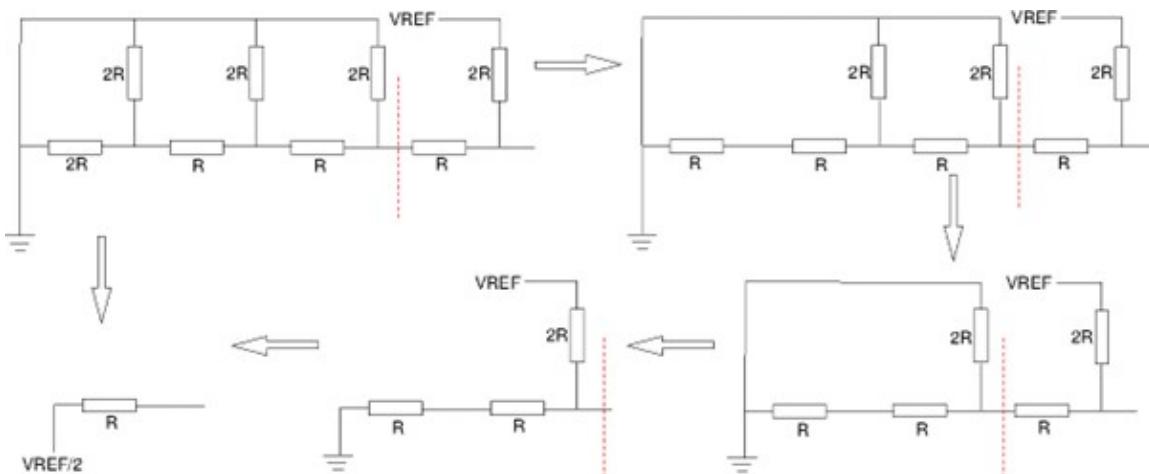

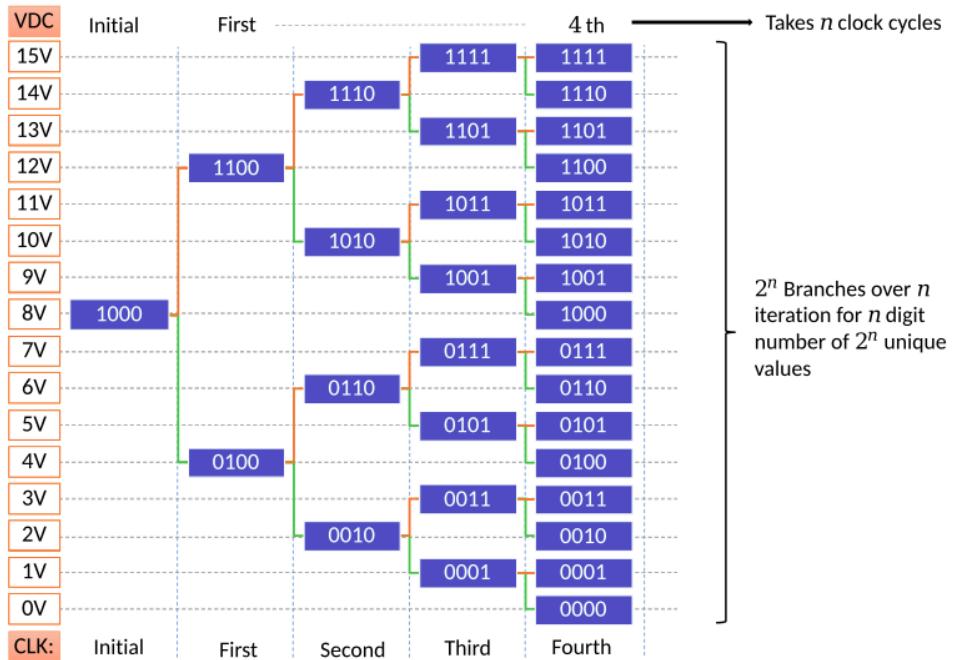

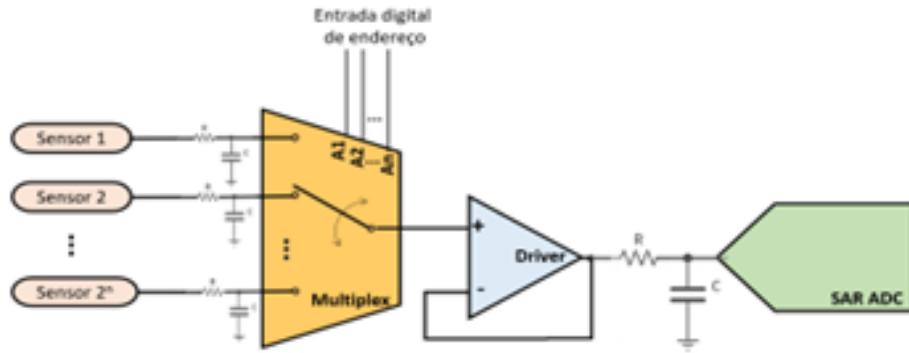

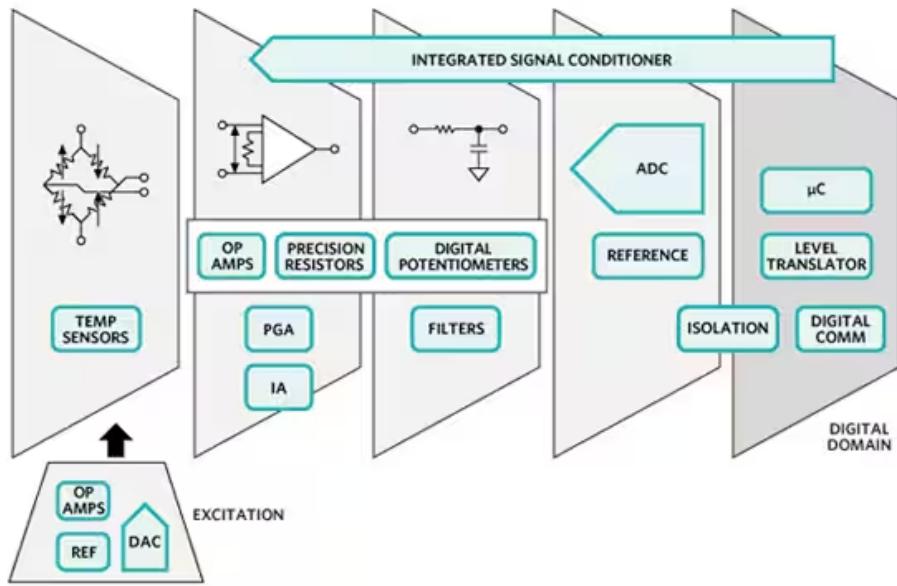

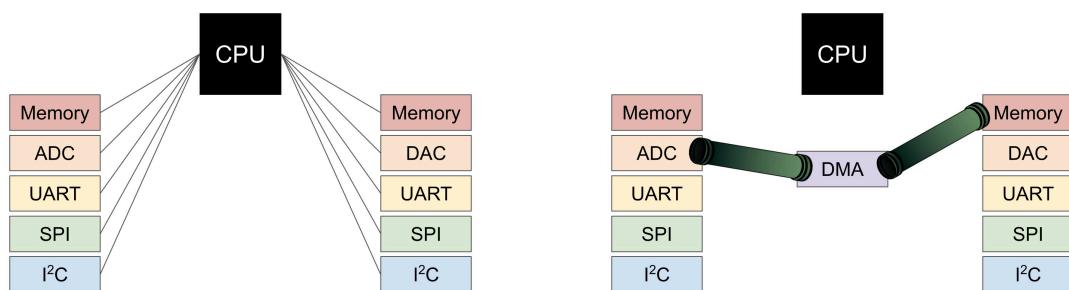

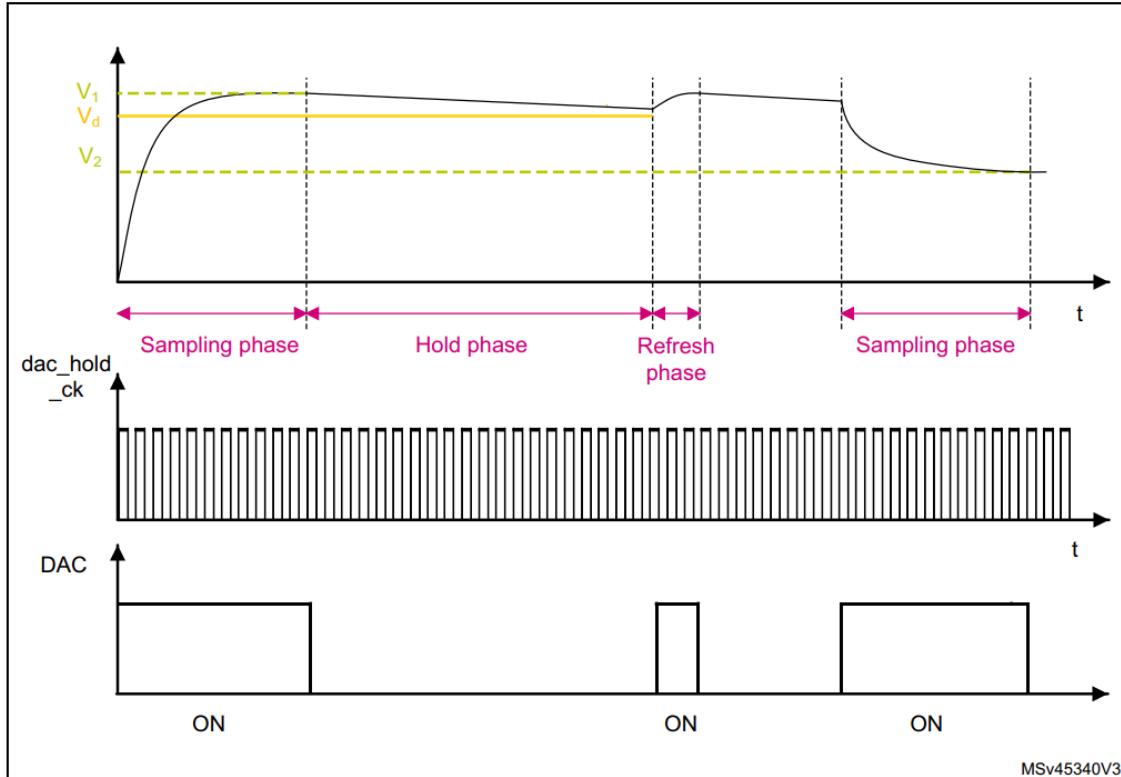

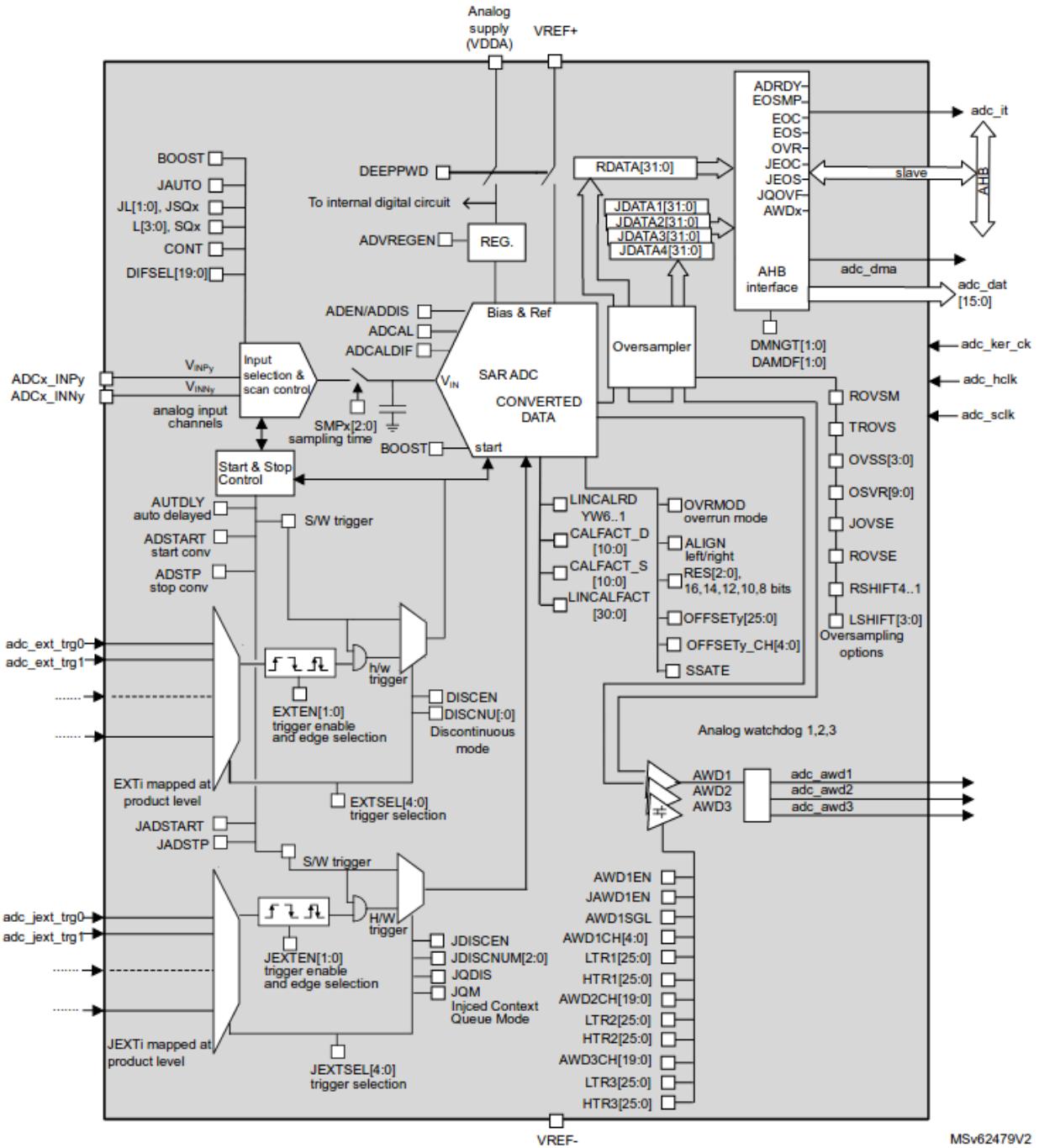

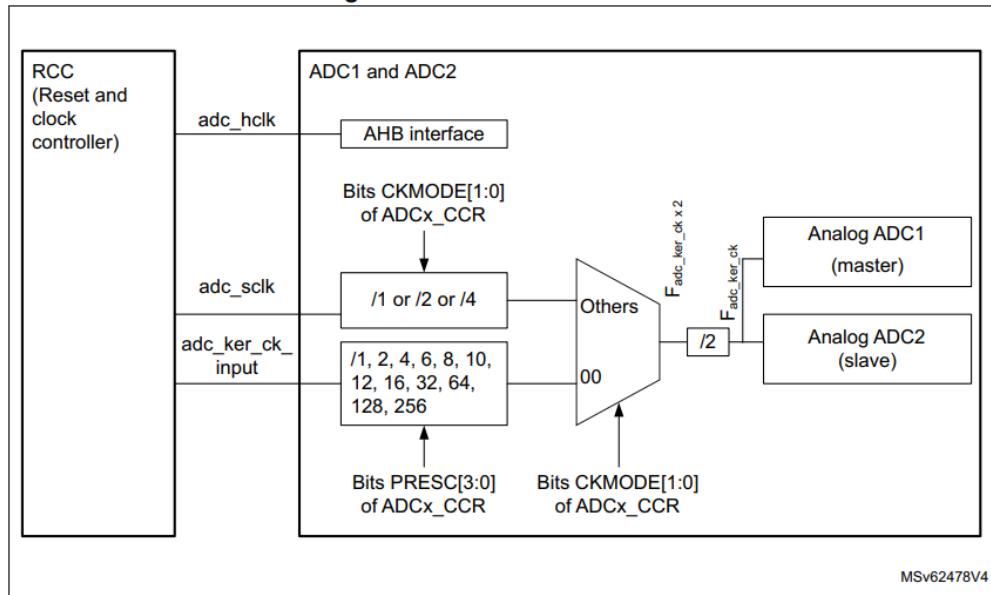

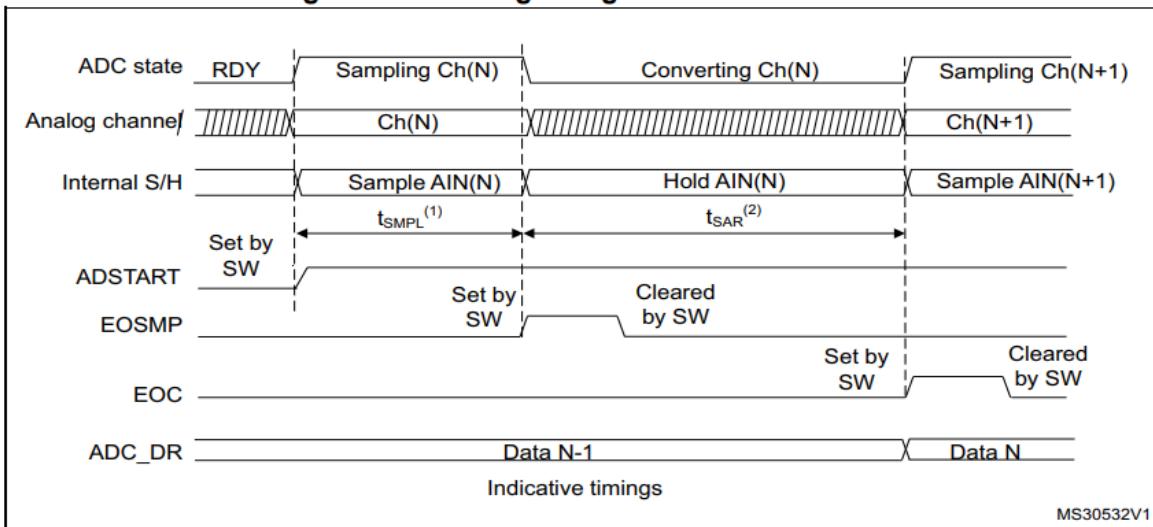

em 3.3V. Transfira o código executável para o microcontrolador no modo *Debug*. Abra a aba “Live Expressions” e insira a variável “adc”. Continue (“Resume”) a execução do programa. A cada parada no *breakpoint*, examine o conteúdo do vetor “adc”. Experimente mover apenas um eixo de cada vez enquanto executa a conversão ADC e transferência; veja como as conversões dos diferentes canais são organizadas no vetor.